1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении микропроцессорных систем и микро-ЭВМ с контролем.

Цель изобретения - повьшение достоверно сти контроля ,

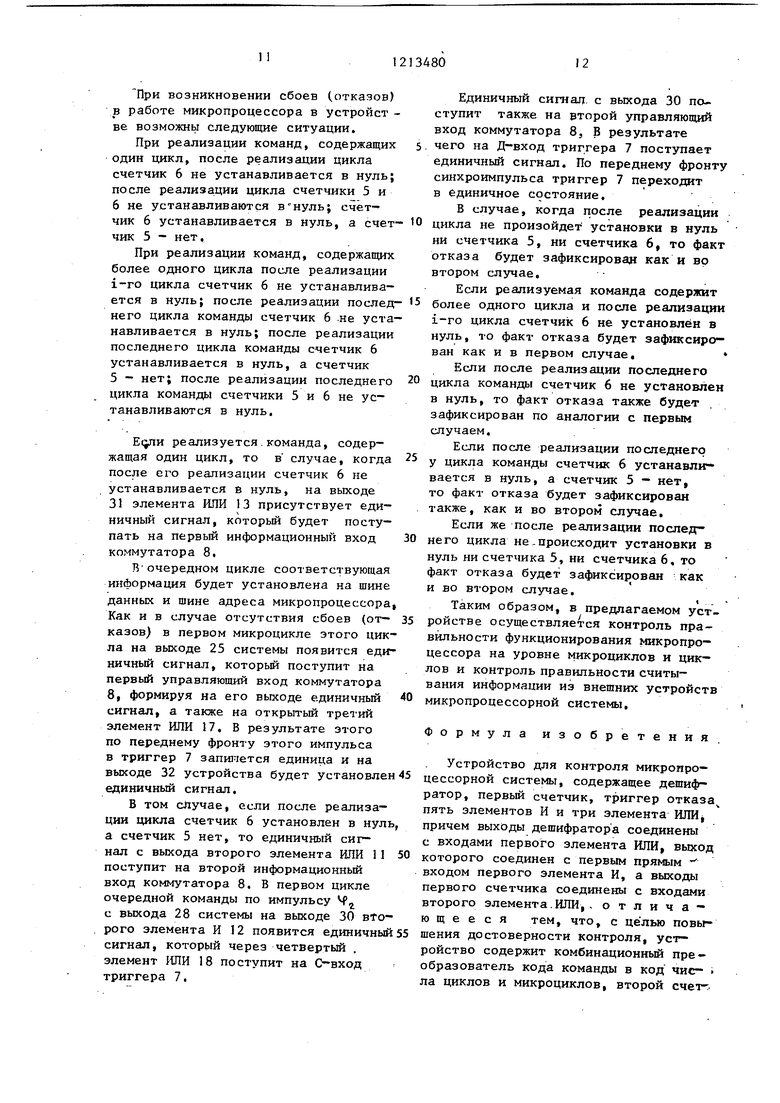

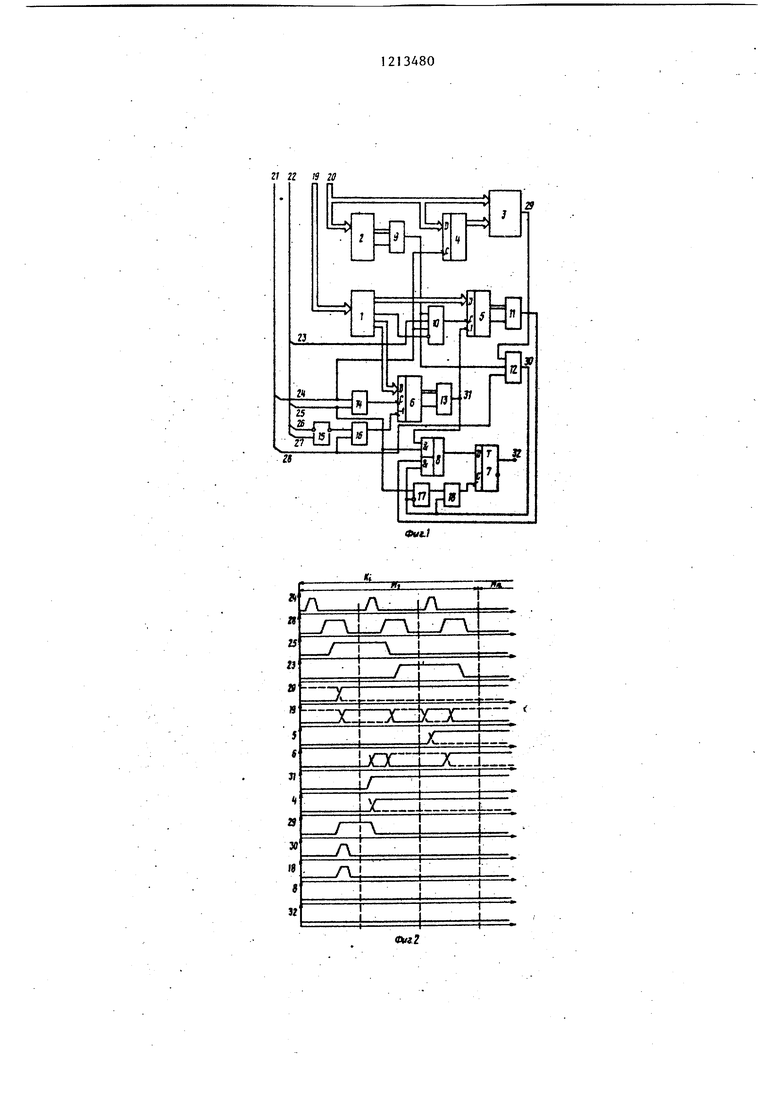

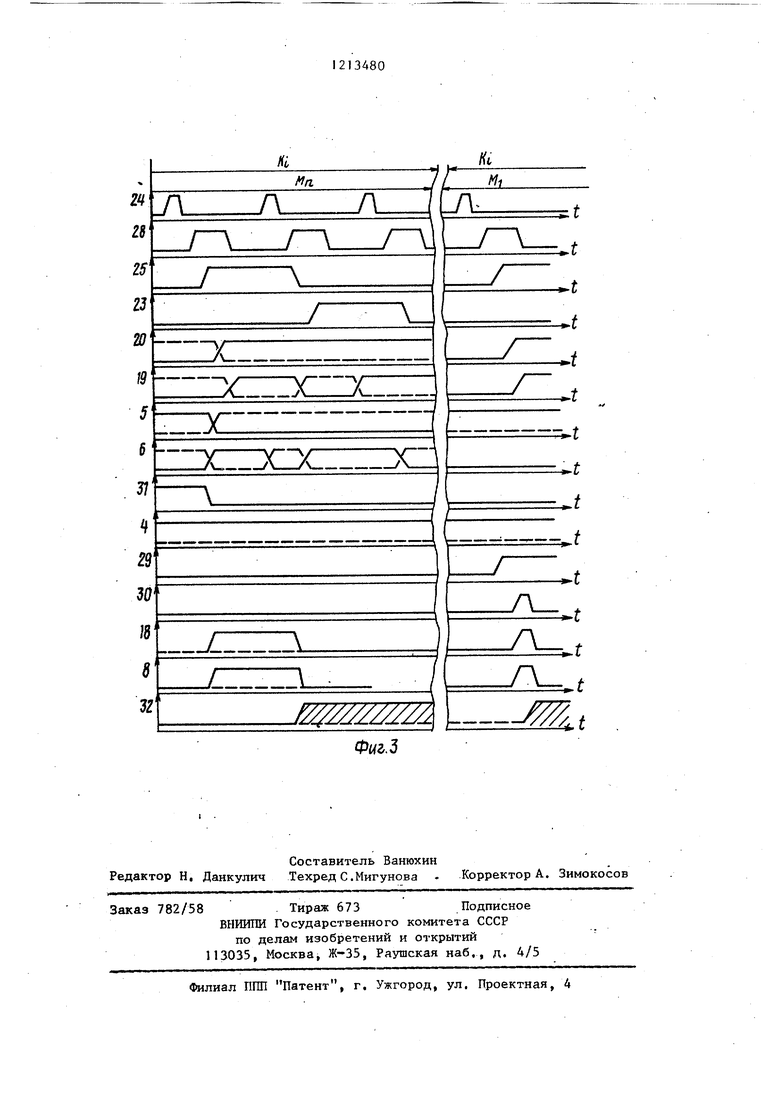

На фиг, 1 представлена функциональная схема устройства для контроля микропроцессорной системы; на г, 2иЗ - временные диаграммы, поясняющие работу устройства,

Устройство (фиг, 1J содержит комбинационный преобразователь 1 кода команды в код числа циклов и микроциклов, дешифратор 2, блок 3 сравнения, буферный регистр 4, первьй счетчик 5, второй счетчик 6, триггер 7 отказов, коммутатор 8, первьй элемент ИЛИ 9, первьй элемент И 10, второй элемент ИЛИ 11, пятый.элемент И 12, третий элемент ИЛИ 13, второй элемент И 14, элемент ИЛИ-НЕ 15, четвертьй элемент И 16, третий элемент И 17, четвертый элемент-ИЛИ 18, выходную шину 19 данных контролируемой микропроцессорной системы, выходную адресную шину 20 контролируемой микропроцессорной системы, группу выходов 21 синхронизации контролируемой микропроцессорной системы, группу управляющих выходов 22 контролируемой микропроцессорной системы, выход 23 разрешения ввода данных контролируемой микропроцессорной системы, первую выходную шину 24 синхронизации контролируемой микропроцессорной системы, выход 25 режима ввода слова состояния контролируемой микропроцессорной системы, выход 26 режима ожидания контролируемой микропроцессорной системы, выход 27 режима захвата контролируемой микропроцессорной системы, вторую выходную шину 28 синхронизации контролируемой микропроцессорной системы, выход 29 блока 3 сравнения, выход 30 пятого элемента И 12, выход 31 третьего элемента ИЛИ 13, выход 32 отказа (сбоя) устройства.

Комбинационный jпреобразователь 1 kop,a команды в код числа циклов и микроциклов предназначен для опреде ления по коду слова состояния процессора соответствующего ему числа мик- роциклов в цикле и по коду команды - количества циклов в команде.

-10

20

213480

Дешифратор 2 .предназначен для определения по коду адреса ячейки блока памяти вида считываемой информации: команда или данные.

5 Блок 3 сравнения предназначен для формирования сигнала, указывающего на выставление : на шине адреса оче редкого адреса. Буферный регистр 4 предназначен для хранения кодов адресов командБ или данньпс, по которым осуществляется обращение к высшим уст ройствам.

Первый счетчик 5 предназначен для осуществления счета числа реализован-

5 ных в команде циклов. Второй счетчик 6 предназначен для осуществления счета числа реализованных в цикле микро- циклов. Триггер 7 отказа предназначен для формирования сигнала сбоя (отказа) объекта контроля. Коммутатор 8 предназначен для подачи сигнала результата контроля правильности выполнения циклов и команды на информационный вход триггера 7 отказов.

Первьй элемент ИЛИ 9 предназначен для формирования единичного сигнала при поступлении с выхода 20 адреса кода адреса команды. Первьй элемент И 10 предназначен для управления

30, синхронизацией первого счетчика 5 Второй элемент ИЛИ 11 предназначен дпя формирования единичного сигнала . при установке в нуль первого счетчика 5, Пятый элемент И 12 предназна35 чен для формирования сигнала управления коммутатором 8 и синхронизацией триггера 7 отказов. Третий элемент ИЛИ 13 предназначен для формирования единичного сигнала при обнулении второго счетчика 6, Второй элемент И 14 предназначен для управления синхронизацией второго счетчика 6,

25

40

Элемент ИЛИ-НЕ 15 предназначен для формирования разрешающего сигнала для четвертого элемента И 16. Четвертый элемент И 16 предназначен дпя формирования импульсов счета для второго счетчика 6. Третий элемент И 17 предназначен для формирования сигнала синхронизации триггера 7 отказа при проверке содержимого второго счетчика 6, Четвертый элемент Ш1И 18 предназначен для передачи сигнала синхро- низации на соответствующий вход триггера 7 отказа.

По входу данных устройства поступает информация с шины I9 данных

контролируемой микропроцессорной системы.

По входу адреса устройства постут пает информация с адресной шины 20 микропроцессорной системы.

По группе выходов 21 синхронизации контролируемой микропроцессорной системы поступает последовательность импульсов У (по шине 24 синхронизации) и Yi( по шине 28 синхронизации), которая поступает также на соответствующие входы синхронизации Y и М . микропроцессора,

С группы выходов 22 управления контролируемой микропроцессорной системы поступают сигналы, свидетельствующие о том, что шина данных микро-.

0000000000000000

- f

10000000000000000

20000000000000001

10000000000000000

20000000000000001

30000000000000010

10000000000000000

20000000000000001

30000000000000010

40000000000000011

0000000000000000

0000000000000000

00000000000000 10

0000000000000011

0000000000000100

Из приведенной таблищл видно,- что единичное значение сигнала на первом выходе дешифратор а появляется только

процессора, находится в режиме ввода данных, на шине данных микпропроцес- сора выставлено слово состояния процессора, в микропроцессоре отсут- ствует режим ожидания и запрещено прямое обращение к памяти соответственно ,

Пример вьшолнения предлагаемого устройства фиг, 1) приведен для случая проверки правильности функционирования микропроцессорной системы, построенной.на базе микропроцессора типа К580, INTEL 8080 или другого аналогичного.

Работа дешифратора 2 при реализации команд, содержащих от одного до пяти циклов, представлена в табл, 1,

Таблица

о о о о .,.0 о 1

0000 ,,,0 о 1 0000 ,..0 о о

0000 ,..00 1 0000 ...о о о

о о о о ...0.0 о

0000..,0 о 1

0000...000

0000...о о о

0000...000

0000 ...о о 1

о о о о ....о о о о о о о ...о о о

0000 ...о о о 0000 ...000

в первом цикле команды, когда на шине адреса выставлен код адреса команды. Во всех остальньк циклах в

соответствующих командах на шине адреса выставляется код адресов яче-i ек,памяти с данными, и поэтому значение соответствующего выходного сигнала дешифратора 2 равно нулю.

1 01 001001

Как видно из табл. 2, единичное значение сигнала на разрешающем выходе комбинационного преобразователя 1 появляется только при реализации команд переходов. Во всех остальных случаях значение сигнала на этом выходе равно нулю, что позволяет блокировать работу устройства, ,в случае поступления на вход мик -: ропроцессора кода команды перехода.

Входы и выходы предлагаемого устройства однозначно соответствуют по функциональному назначению и характе ристикам входам и выходам микропроцессора.

i 12134806

Работа комбинационного преобразо- вателя 1 кода команды в код числа циклов и микроциклов при реализации одно-, двух- и трехбайтных команд 5 представлена в табл. 2,

Таблица 2

О О 1

0101

В устройстве контроль правильно- 45 сти функционирования микропроцессорной системы осуществляется следующим образом.

В первом микроцикле первого Цикла на щине адреса и шине данных 50 микропроцессора выставляется код адреса команды и код слова состояния процессора соответственно. По первом коду определяется, что адрес на шине адреса микропроцессора является адре 55 сом команды. По второму коду определяется число микроциклов в первом цикле команды. В этом же микроцикле на выходе 25 системы появляется сигнал, свидетельствующий о том, что на шине данных находится .код слова состояния процессора,

В очередном микроцикле по синхроимпульсу Ч , поступающему на выход 24 синхронизации системы, код числа микроцикло, уменьшенный на единицу, т.е. число (Nji -1) поступает в счетчик 6, где NJ - число микроциклов в i-M цикле j-й команды. Это необходимо для того, чтобы запись этого кода осуществлялась во втором цикле команды. По импульсу Ч, , поступающему с выхода 28 синхронизации системы, происходит уменьшение содержимого счетчика 6 на единицу.

Во втором цикле работы устройства с выхода 23 системы поступает единичный сигнал, свидетельствующий о том, что шина данных микропроцессора находится в режиме ввода информации.

В третьем микроцикле работы микропроцессора на шину данных поступает код команды, считанной из блока памяти. По импульсу Y в этом микроцикле произойдет запись числа циклов в команде в счетчик 5.

По импульсу Ч произойдет уменьшение содержимого счетчика 6 на единицу. Так будет продолжаться до тех пор, пока счетчик 6 микроциклов не установится в нуль.

Это свидетельствует о том, что первый цикл команды выполнен. При этом произойдет уменьшение содержимого счетчика 5 на единицу.

Если реализуемая команда содержит один цикл, то после установки в нуль счетчика 6 должна произойти установк в нуль счетчика 5 при правильном функционировании микропроцессора. Если в работе микропроцессора были сбои (или возник отказ, то-в первом микроцикле очередной команды они обнаруживаются следующим образом В этом случае содержимое счетчика 5, или счётчика 6. или обоих счетчиков будет отличаться от нуля. Коммутатор 8 будет открыт или по второму информационному входу, или по первому информационному входу, или по обоим одновременно, В первом микроцикле очередной команды по импульсу с выхода 28 синхронизации системы на выходе элемента И I2 появится единич0

5

0

5

0

5

0

5

ньй сигна л, а через время t, равное времени между передними фронтами импульса и импульсом на выходе 25, на выходе 25 системы появится также единичный сигнал.

В результате в триггер 7 отказа запишется единица и будет зафиксирован факт отказа. Если сбоев (отказов) в работе контролируемой системы не возникло, то работа устройства будет продолжена. .

В том случае, если команда.реализуется за два и более циклов, то после реализации каждого цикла содержимое счетчика 6 должно быть равно, нулю. При этом происходит уменьшение содержимого счетчика 5 на едя- лицу. Контроль правильности реализации микроциклов осуществляется подачей единичного сигнала на выходе 25 системы..

Если работа микропроцессора происхо дила в цикле с нарушениямиj.то факт сбоя отказа).будет зафиксирован, Контроль правильности выполнения команды осуществляется яроверкой на равенство нулю содержимого счетчика 5 после того, как на шине адреса . микропроцессора будет выставлен код адреса очередной команды.

Устройство работает следующим образом.

В исходном .состоянии все элементы памяти устройства находятся в нулевом состоянии (входы начальной установки не показаны). Функционирование микропроцессора начинается после включения питания с выполнения первой команды программы, расположенной в блоке памяти в ячейке с, нулевым значением адреса. В первом микроцикле первого цикла на шине адреса будет выставлен код адреса первой команды реализуемой программы, а на шине данных - код слова состояния процессора. На выходы 24 и 28 контролируй- емой системы поочередно поступают им-. пульсы Ц и Ч з. с соответствующих выходов генератора тактовых импульсов контролируемой микропроцессорной системы. Через время t. на выходе 25 системы появится единичный сигнал, который откроет второй .элемент И 14 и третий элемент И 17 и поступит на первый управляющий вход коммутатора 8, На этом первый микроцикл работы устройства заканчивается.

Код адреса первой команды поступит на вход дешифратора 2 и на выход первого элемента ИЛИ 9 будет установлен единичный сигнал, который откроет первый элемент И 10 и пятый элемент И 42,

Код слова состояния процессора, поступив на вход комбинационного преобразователя 1, преобразуется в код числа микроциклов первого цик- ла и поступает со второго информа- ционного выхода преобразователя 1 на информационный вход счетчика 6, С приходом первого импульса Ч второго микроцикла на выходе второго элемента И 14 будет сформирован единичный импульс синхронизации, в результате чего код () числа микроциклов запишется в счетчик 6, С приходом второго импульса Ч . на выходе четвертого элемента И 16 будет сформирован единичный сигнал, по которому произойдет уменьшение на единицу содержимого счетчика 6. Через время, t единичный сигнал с выхода 25 системы снимается. Через время t,j, равное времени задержки подачи сигнала Разрешение записи относительно импульса на выходе 23 системы будет установлен единичн сигнал. На этом работа устройства н втором микроцикле завершается.

35

40

45

При отсутствии сигналов Ожидание Захват в. третьем микроцикле рабО ты устройства на шине данньрс системы ; будет установлен код команда, считанной из памяти. Этот код команды п О , ступит на вход комбинационного пре- образователя 1, Предположим, что считанная команда не является командой перехода. Тогда с первого информационного выхода комбинационного преобразователя 1 код числа циклов в команде поступит на информационный вход счетчи-; ка 5 .Единичный сигнал с управляющего выхода комбинационного преобразова- . теля 1 поступит на инверсный вход первого элементами 10 и откроет его, По импульсу 4, в этом микроцикле

работы на выходе первого элемента

И 10 будет сформирован сигнал синхронизации и код числа циклов в команде будет записан в счетчик 5, По импуль- су зтом микроцикле работы содержимое счетчика 6 будет уменьшено на единицу. Через время t единичный

50

0

5

0

5

0

5

0

5

0

сигнал на выходе 23 системы будет сня т,

В дальнейшем работа устройства продолжается следующим образом, В каждом микроцикле цикла команды по импульсу Ч будет происходить уменьшение содержимого счетчика 6 на единицу, .

При вьшолнении последнего цикла по импульсу f в этом цикле при правильном функционировании устройства должно произойти обнуление счетчика 6, При этом, после появления нулевого сигнала на выходе третьего элемента ИЛИ 14 произойдет уменьшение содержимого счетчика 5 на единицу, В случае, если реализуемая команда содержит один цикл, в очередном цикле на шине 20 адреса и шине 19 данных устанавливается соответствующая информация и работа у :тройст - ва не отличается от описанной,

В том случае, когда реализуется команда с числом циклов более одного во втором цикле исполнения команды на шине данных будет установлен «од слова состояния процессора.

По импульсу Ч, во втором микроцикле этого цикла в счетчик 6 запишется код числа микроциклов во втором цикле выполнения команды. При отсутствии сбоев (отказов) работа устройства аналогична описанной, В том случае, если реализуемая микропроцессором команда является командой перехода, то после того как на шине данных будет установлен код, d с первого информационного выхода комбинационного преобразователя 1 на информационный вход счетчика 5 поступит код числа циклов в команде, на управляющем ; выходе преобразователя появится единичный сигнал, которьй закроет первый элемент И 10. В результате будет запрещено формирование сигнала синхронизации счетчика 5, который вследствие этого останется в исходном (нулевом) состоянии. После реализации первого цикла команды перехода счетчик 6 пересчет в нулевое состояние. Это состояние счетчиков 5 и 6, соответствующее исходному состоянию всего устройства в целом, будет поддержит-- ваться до тех пор, пока микропроцессор не перейдет к реализации команды, не являющейся командой перехода.

При возникновении сбоев (.отказов) в работе микропроцессора в устройст - ве возможны следующие ситуации.

При реализации команд, содержащих один цикл, после реализации цикла счетчик 6 не устанавливается в нуль; после реализации цикла счетчики 5 и 6 не устанавливаются в нуль; счетчик 6 устанавливается в нуль, а счет- чик 5 - нет.

При реализации команд, содержащих более одного цикла после реализации i-ro цикла счетчик 6 не устанавливается в нуль; после реализации послед- него цикла команды счетчик 6 .не устанавливается в нуль; после реализации последнего цикла команды счетчик 6 устанавливается в нуль, а счетчик 5 - нет; после реализации последнего цикла команды счетчики 5 и 6 не устанавливаются в нуль,

Eiyin реализуется.команда, содержащая один цикл, то в случае, когда после его реализации счетчик 6 не устанавливается в нуль, на выходе 31 элемента ИЛИ 13 присутствует единичный сигнал, который будет поступать на первый информационный вход коммутатора 8,

R-очередном цикле соответствующая информация будет установлена на шине данных и шине адреса микропроцессора Как и в случае отсутствия сбоев (от- казов) в первом микроцикле этого цикла на выходе 25 системы появится едрг- ничный сигнал, которьй поступит на первый управляющий вход коммутатора 8, формируя на его выходе единичный сигнал, а также на открытый третий элемент ИЛИ 17, В результате этого по переднему фронту этого импульса в триггер 7 запшчется единица и на выходе 32 устройства будет установлен единичный сигнал,

В том случае, если после реализации цикла счетчик 6 установлен в нуль а счетчик 5 нет, то единичный сигнал с выхода второго элемента ИЛИ 1I поступит на второй информационный вход коммутатора 8. В первом цикле очередной команды по импульсу 4 с выхода 28 системы на выходе 30 второго элемента И 12 появится единичный сигнал, который через четвертый . элемент ИЛИ 18 поступит на С-вход триггера 7.

Единичный сигнал с выхода 30 поступит также на рторой управляющий вход коммутатора 8, В результате чего на Д-вход триггера 7 поступает единичный сигнал. По переднему фронт синхроимпульса триггер 7 переходит в единичное состояние,

В случае, когда после реализации цикла не произойдет установки в нуль ни счетчика 5, ни счетчика 6, то фак отказа будет зафиксирован как и во втором случае.

Если реализуемая команда содержит более одного цикла и после реализаци i-ro цикла счетчик 6 не установлен в нуль, то факт отказа будет зафиксирован как и в первом случае,

Если после реализации последнего цикла команды счетчик 6 не установле в нуль, то факт отказа также будет зафиксирован по аналогии с первым случаем.

Если после реализации последнего у цикла команды счетчик 6 устанавли вается в нуль, а счетчик 5 - нет, то факт отказа будет зафиксирован также, как и во втором случае,

Если же после реализации последнего цикла не-Происходит установки в нуль ни счетчика 5, ни счетчика 6, то факт отказа будет зафиксирован как и во втором случае.

Таким образом, в предлагаемом устройстве осуществляется контроль правильности функционирования микропроцессора на уровне микроциклов и циклов и контроль правильности считывания информации из внешних устройств микропроцессорной системы.

Формула изобретен и я

Устройство для контроля микропроцессорной системы, содержащее дещиф- ратор, первый счетчик, триггер отказа пять элементов И и три элемента ИЛИ причем выходы дешифратора соединены с входами первого элемента ИЛИ, выход которого соединен с первым прямым входом первого элемента И, а выходы первого счетчика соединены с входами второго элемента.ИЛИ,. отличающееся тем, что, с целью повышения достоверности контроля, устройство содержит комбинационный преобразователь кода команды в код чис- ла циклов и микроциклов, второй счет-:

чик, коммутатор, буферный регистр, блок сравнения, четвертьм элемент ИЛИ и элемент ИЛИ-НЕ, причем выход кода числа циклов в команде комбинационного преобразователя кода команды в код чисда циклов и микроциклов соединен с информационным входом первого счетчика, выход кода числа микроциклов в цикле комбинационного преобразователя кода команды в код числа циклов и микроциклов соединен с информационным входом второго счечика, разрешающий выход комбинационного преобразователя кода команды в код числа циклов и микроциклов соединен с ищерсным входом первого элемента И, выходы второго счетчика соединены с входами третьего элемента ИЛИ, выход которого соединен со счетным входом первого счетчика и первым информационным входом ком - мутатора, выходная адресная шина контролируемой микропроцессорной системы соединена с входом дешифратора, первым входом блока сравнения и информационным входом буферного регистра, выход буферного регистра соединен с вторым входом блока сравнения, выходная шина данных контролируемой микропроцессорной системы соединена с входом комбинационного преобразователя кода команды в код числа циклов и микроциклов, выход разрешения ввода данных контролиру- емой микропроцессорной системы соединен с вторым прямым входом первого элемента И, йыход режима ввода слова состояния контролируемой микропроцессорной системы соединен с первым входом второго элемента И, прямым входом третьего элемента Л и первмм управляющим входом коммутатора, выход режима ожидания кон.- тролируемой микропроцессорной системы соединен с инверсным входом зле мента ШШ-НЕ, выход режима захвата контролируемой микропроцессорной системы соединен с прямым входом элемента ИЛИ-НЕ, первая выходная шина синхронизации контролируемой мик-

ррпроцессорной системы соединена с вторым входом второго элемента И, третьим прямым входом первого элемента И и входом синхронизации буферного регистра, вторая выходная шина

синхронизации контролируемой микропроцессорной системы соединена с первыми входами четвертого и пятого элементов И, выход первого элемента ИЛИ соединен с вторым входом пятого

элемента И, выход блока сравнения соединен с третьим входом пятого элемента И, выход которого соединен с первым входом четвертого элемента ШШ, инверсньм входом третьего эле

мента И и вторым управляющим входом коммутатора, выход третьего элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом синхрониза11ии триггера отказа, выход коммутатора соединен с информационным входом триггера отказа, единичный выход которого является выходом отказа устройства, выход элемента ИЛИ-НЕ соединен с вторым

входом четвертого элемента И, выход которого соединен сО счетным входом второго счетчика, выход второго эле- мента И соединен с входом синхронизации второго счетчика, выход первого

элемента И соединен с входом синхронизации первого счетчика, выход вто-i рого элемента ИЛИ соединен с вторым информационным входом коммутатора.

Ф«г.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля условных переходов микропроцессора | 1984 |

|

SU1238076A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство приоритета | 1990 |

|

SU1829033A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

Изобретение касается цифровой вычислительной техники и может быть использовано при построении микропроцессорных систем и микро-ЭВМ с кон±ролем. Целью изобретения является повьппение достоверности контроля, Ё устройстве осуществляется контроль . правильности функционирования микропроцессора на уровне микроциклов и . циклов и контроль правильности счи-г тывания информации из внешних устройств микропроцессорной системы. Устройство содержит ко бинационный преобразователь кода команды в код числа циклов и микроциклов, дешифраг тор, блок сравнения, буферный ре- гистр, два счетчика, триггер отказов, коммутатор, четыре элемента ИЛИ, пять злементов И, элемент Ш1№- НЕ, 3 ил,, 2 табл. Од 4i 00

| Дяс | |||

| Коффрон | |||

| Технические средстт ва микропроцессорных систем | |||

| М.; Мир, 1983, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-23—Публикация

1984-07-13—Подача