Изобретение относится к шочислительной технике и электронике и может быть использовано при построении многоканальных вычислительных систем, в частности для поканального разделения системы, например, в режиме проверки работоспособности каждого канала мажоритарно-резервированной системы.

Известен мажоритарный элемент на комплементарных МДЩ-транзисторах

Недостаток известного элемента заключается в его узких функциональ ных возможностях, в частности, проявляющихся в невозможности его использования для поканального разделения систем.

Наиболее близким к предлагаемсмлу по технической сущности является мажоритарный элемент, содержащий первый, второй МДП-транзисторы с ка налами р-типа, третий, четвертый МДП-транзисторы с каналами п-типа, первый, второй, третий инверторы, выходы которых подключены к выходу элемента, первый инвертор вк.точен между стоками первого и третьегр МДП-транзисторов, истоки которьис соединены соответственно с шиной питания и общей шиной, второй и третий.

инверторы вкллочены между стоками второго и четвертого МДП-транзисторов, истоки которых соединены соответств ено с шиной питания и общей шиной, аатворы первого, третьего МДП-транзисторов и вход второго инвертора соединен с вторым информационным входом, входа первого и третьего инверторов - с первым, зат

fO воры второго и четвертого МДП-транзисторов - с. третьим 2,

Однако мажоритарный элемент не -Обеспечивает возможности отключения сигналов, поступающих в данный канал

15 из других, в то время, как такая необходимость возникает в режимах проверки работоспособности каждого канала, а также при отказе двух каналов в трехканальной системе.

20

Цель изобретения - расширение функциональных возможностей мажоритарного элемента.

Поставленная цель достигается тем, что в мгокоритарный элемент, со25держащий первый, второй МДП-транзисторы с каналами р-типа и третий, четвертый МДП-транзисторы с каналами п-типа, первый, второй, третий инверторы, выходы которых соединены

30 с выходом элемента, первый инвертор

включен между стоками первого и третьего МДП-транзисторов, истоки которых соединены соответственно с. шиной питания и общей шиной, второй и тpeти l инверторы включены между стоками второго и четвертого МДПтранэисторов, затворы первого и ; третьего МДП-транзис,торов и вход второго инвертора соединен с вторым информационным входом, входы первог и третьего инверторов - с первым, затворы второго и четвертого МДПтранзисторов - с третьим, введены пятый и шестой МДП-транзисторы с каналами р-типа, истокиtкоторых соединены с шиной.питания, а стоки соответственно со стоком первого к истоком второго МДП-транзисторы, и седьмой, восьмой МДП-транзисторы с каналами п-типа, истоки которых соединены с общей шиной, а стоки соответственно со стоком третьего и истоком четвертого МДП-транзисторов, затворы пятого, восьмого МДПтранзисторов соединены с прямым, а затворы шестого, седьмого - с инверсным управляющими входами.

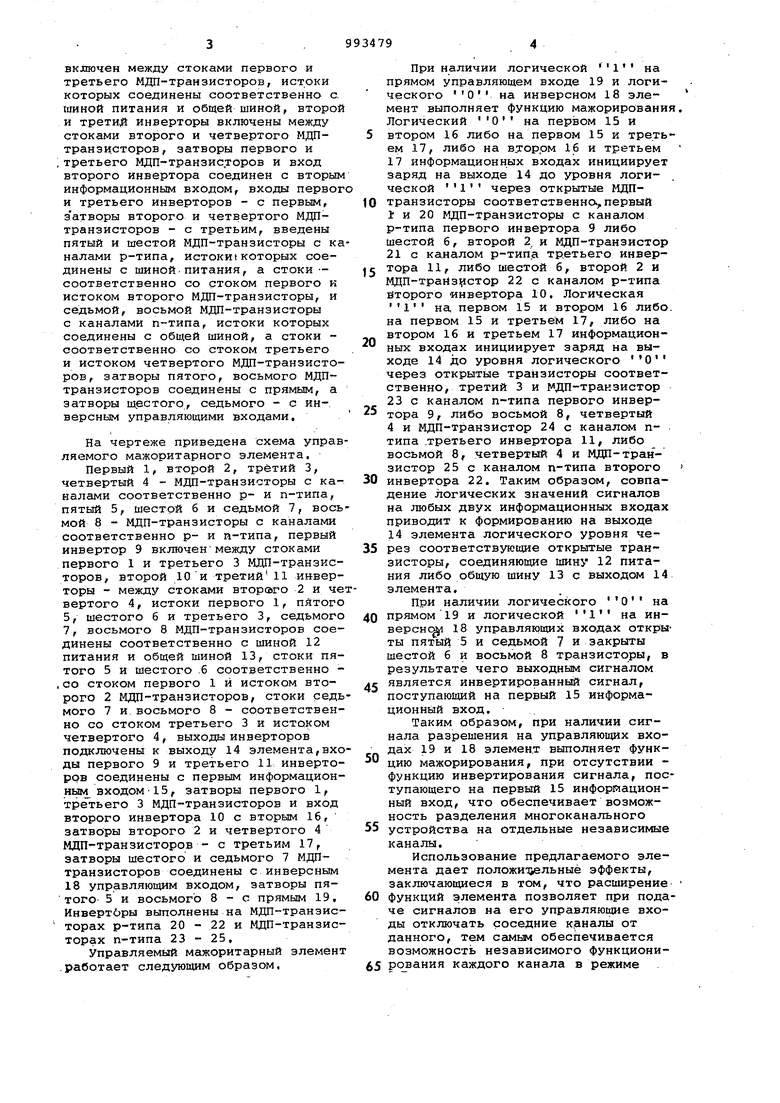

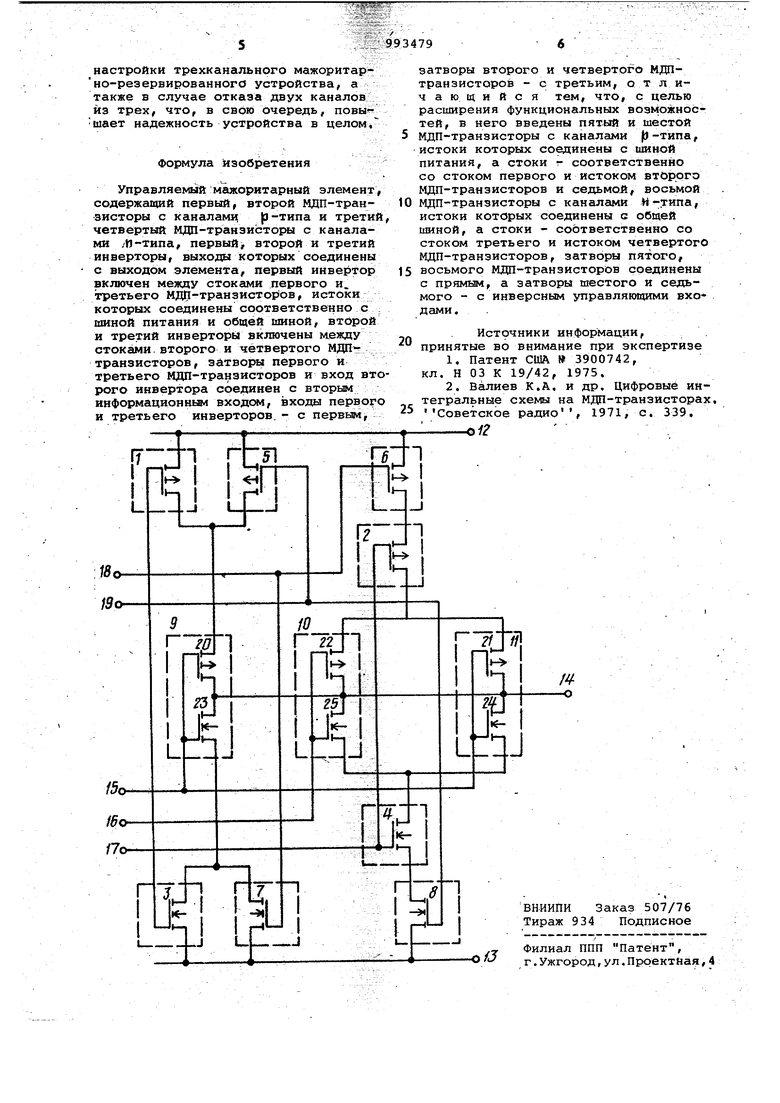

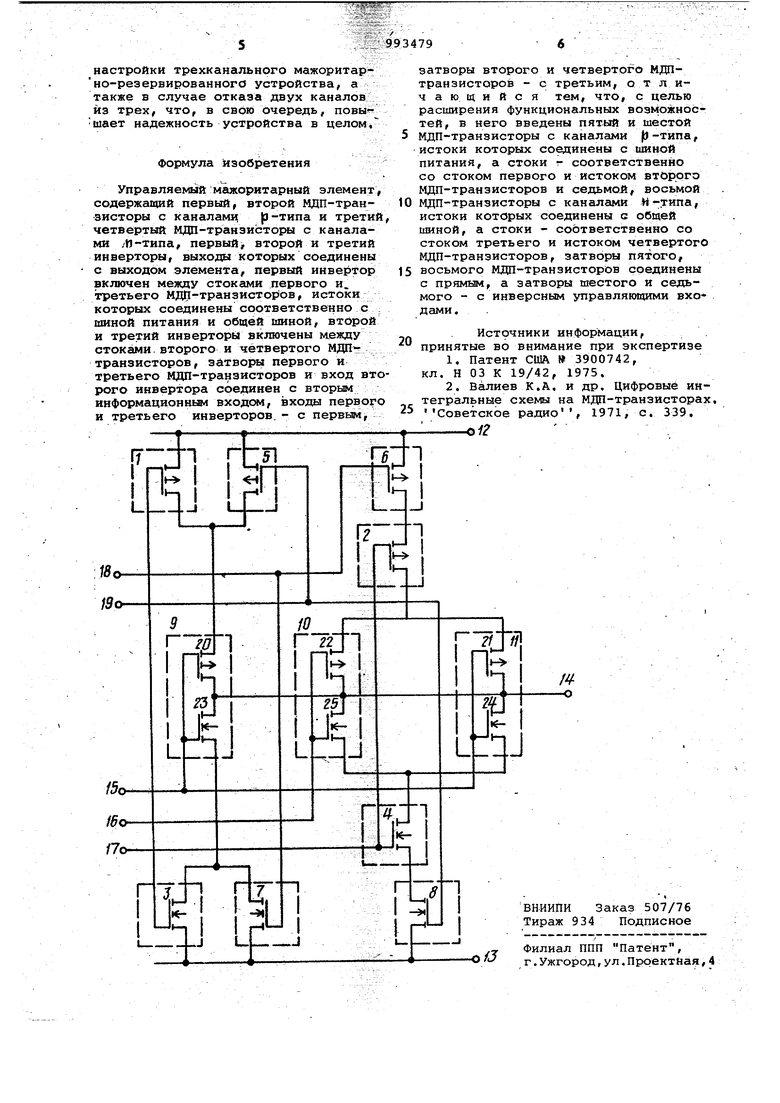

На чертеже приведена схема управляемого мажоритарного элемента.

Первый 1, второй 2, третий 3, четвертый 4 - МДП-транзисторы с каналами соответственно р- и п-типа, пятый 5, шестой б и седьмой 7, восьмой 8 - МДП-транзисторы с каналами соответственно р- и п-типа, первый инвертор 9 включенмежду стоками первого 1 и третьего 3 МДП-транзисторов, второй 10и третий11 инверторы - между стоками вторсьго 2 и чевертого 4, истоки первого 1, питого 5, шестого б и третьего 3, седьмого 7, восьмого 8 МДП-транзисторов соединены соответственно с шиной 12 питания и общей шиной 13, стоки пятого 5 и шестого .6 соответственно ,со стоком первого 1 и истоком второго 2 МДП-транэисторов, стоки седьмого 7 и.восьмого 8 - соответственно со стоком третьего 3 и истоком четвертого 4, выходы инверторов подключены к выходу 14 элемента,входы первого 9 и третьего 11 инверторов соединены с первым информационным входом 1 5 , затворы первого 1, третьего 3 МДП-транзисторов и вход второго инвертора 10 с вторым 16, затворы второго 2 и четвертого 4 МДП-транзисторов - с третьим 17, затворы шестого и седьмого 7 МДПтранзисторов соединены с инверсным 18 управляющим входом, затворы пятого 5 и восьмого 8 - с прямым 19. Инверторы выполнены на МДП-транзисторах р-типа 20 - 22 и МДП-транзисторах п-типа 23-25,

Управляемый мажоритарный элемент .работает следующим образом.

При наличии логической i на прямом управляющем входе 19 и логического О на инверсном 18 элемент выполняет функцию мажорирования. Логический О на первом 15 и втором 16 либо на первом 15 и третьем 17, либо на втором 16 и третьем 17 информационных входах инициирует заряд на выходе 14 до уровня логической 1 через открытые МДПQ транзисторы соответственно первый 1: и 20 МДП-транзисторы с каналом р-типа первого инвертора 9 либо шестой б, второй 2, и МДП-транзистор 21 с каналом р-типа третьего инвер5 тора 11, либо шестой 6, второй 2 и МДП-траНз стор 22 с каналом р-типа йторого инвертора 10, Логическая на, первом 15 и втором 16 либо, на первом 15 и третьем 17, либо на

втором 16 и третьем 17 информационных входах инициирует заряд на выходе 14 до уровня логического О через открытые транзисторы соответственно, третий 3 и МДП-тракзистор 23 с каналом п-типа первого инвертора 9, либо восьмой 8, четвертый 4 и МДП-транзистор 24 с каналом птипа .третьего инвертора 11, либо восьмой 8, четвертый 4 и МДП-транзистор 25 с каналом п-типа второго

0 инвертора 22, Таким образом, совпадение логических значений сигналов на любых двух информационных входах приводит к формированию на выходе 14 элемента логического уровня че5 рез соответствующие открытые транзисторы, соединяющие шину 12 питания либо общую шину 13 с выходом 14 элемента.

При наличии логического О на

0 прямом 19 и логической на инверснс 18 управляющих входах открыты пятый 5 и седьмой 7 и закрыты шестой 6 и восьмой 8 транзисторы, в результате чего выходным сигналом

с является инвертированный сигнал, поступающий на первый 15 информационный вход,

Таким образом, при наличии сигнала разрешения на управляющих входах 19 и 18 элемент выполняет функ цию мажорирования, при отсутствии функцию инвертирования сигнала, поступающего на первый 15 информационный вход, что обеспечивает возможность разделения многоканального

5 устройства на отдельные независимые каналы,

Использование предлагаемого элемента дает положийельныё эффекты, заключающиеся в том, что расширение

0 функций элемента позволяет при подаче сигналов на его управляющие входы отключать соседние кдналы от данного, тем самым обеспечивается возможность независимого функциони5 рования каждого канала в режиме

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Формирователь импульсов для блоков памяти | 1985 |

|

SU1278973A1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Генератор импульсов,управляемый напряжением | 1980 |

|

SU902229A1 |

Авторы

Даты

1983-01-30—Публикация

1981-07-22—Подача