ходами дешифратора цикла, выходы третьего и четвертого элементов И соединены соответственно с вторыми входами второго и первого элементов ИЛИ, выходы которых через формирователь импульса соединены с первыми входами пятого, шестого эдемевтов И, третьего и четвертого элементов ИЛИ и с входом третьего счетчика, второй вход пятого элемента И соединен с прямым выходом триггера направления передачи, инверсный выход которого соединен с вторым входом шестого элемента И с сбросовым входом реверсивмого счетчика, суммирующий и вы читающий входы которого соединены соответственно с выходами пятого и шестого элементов И, а вход параллельной записи - через шифратор с выходом третьего счетчика, выход реверсивного счетчика соединен с

информационными входами дешифратора состояния и дешифратора цикла, второй вход Четвертого элемента ИЛИ-и первый вход пятого элемента ИЛИ являются третьим входом блока, вторые входы третьего и пятого элементов ИЛИ и первый вход триггера направления передачи являются четвертым входом блока, выход пятого элемента ИЛИ соединен с первым входом триггера разрешения обмена, второй вход которого и второй вход триггера направления передачи соединены с выходом третьего счетчика, группа выходов Дешифратора состояния является группой разрешающих выходов блока, первый и второй выходы дешифратора состояния, выходы третьего и четвертого элементов ИЛИ являются соответственно первым, вторым, третьим и четвертым входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1411809A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для сопряжения разноскоростных вычислительных устройств | 1991 |

|

SU1789986A1 |

| Устройство для обмена информацией | 1982 |

|

SU1072035A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРОВ,- содержащее блок запуска обмена, первый - четвертый входы которого соединены соответственно с первым, вторым запросными и первым, вторым входами готовности устройства, блок управления, первыйчетвертый входы которого соединены соответственно с первым, вторым входами сопровождения устройства, с первым, вторым выходами блока запуска обм.ена, первый и второй ревер-. сивный коммутаторы, управлякяцие входы которых соединены с первым и ; вторым выходами блока управления, причем третий, четвертый выходы блог ка управления соединены соответственно с первым и вторым выходами прерывания устройства, первый входвыход первого реверсивного коммутатора и второй вход-выход второго реверсивного коммутатора соединены соответственно с первым и вторым информационными входами-выходами устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены группа блоков памяти, первая и вторая группы реверсивных коммутаторов, причем первый информационный вход-выход реверсивного коммутатора первой группы соединен с входом-выходом соответствующего блока памяти группы, первый информационный вход-выход реверсивного коммутатора второй группы соединен с вторым информационным входом-выходом предшествующего реверсивного коммутатора второй группы и с вторым входом-выходом соответствующего реверсивного коммутатора первой группы, второй информационный вход-выход первого реверсивного ка1 1мутатора соединен с первым информационным входом-выходом первого реверсивного коммутатора второй группы, первый информационный вход-выход второго реверсивного коммутатора соединен с вторыми информационны1 и входами-выходами последних реверсивных коммутаторов первой и второй групп, управляющие входы реверсивных комi мутаторов первой и второй групп соединены с соответствуюЕДоми выходами (П С группы разрешающих выходов блока управления . 2. Устройство по п. 1, отличающее ся тем, что блок уп.равления содержит шесть элементов И, пять элементов ИЛИ, три счетчика, реверсивный счетчик, шифратор, дешифратор состояния, дешифратор Ьп цикла, формирователь импульса, триггер разрешения обмена и триггер на:AD правления передачи, причем первый, второй входы блока соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых и управляющий вход дешифратора состояния соединены с выходом триггера разрешения обмена, выходы первого и второго элементов И соединены соответственно с входами первого и второго счетчиков, выход первого счетчика соединен с первыми входами третьего элемента И и первого элемента ИЛИ, выход второго счетчика соединен с первыми входами четвертого элемента И и второго элемента ИЛИ, вторые входы третьего и четвертого элементов И соединены соответственно с первым и вторым вы

Изобретений относится к вычисли тельной технике , конкретно к устрой ствам обмена пакетами между однородными вычислительными махчинами, и может быть использовано в многома шинных системах. Известно устройство для. сопряжения процессоров, построенное по при ципу почтового ящика l Наиболее близким к изобретению по технической сущности является . устройство для сопряжения процессоров, .содержащее регистр, соединенный через коммутаторы с соответствующими шинами передачи данных, схемы формирования управляющих сигналов 2j . Недостатком известных устройств является то, что запись в буфер и сч тывание из него производится раздел но во времени, что уменьшает скорость обмена информацией. Цель изобретения - повышение быстродействия . Поставленная цель достигается тем, что в устройство для сопряжени двух процессоров, содержащее блок запуска обмена, первый - четвертый входы которого соединены соответстве нн0 с первым, вторым запросными и с первым, вторым входами готовности устройства, блок управления, первый - четвертый входу которого соединены соответственно с первым, вторым входами сопровождения устройства, с первым, вторым входами. блока запуска обмена, первый и. второй реверсивные коммутаторы, управляющие входы которых соединены , с первым и вторым выходами блока управления, причем третий, четвертый выхода блока управления соедииены соответственно с первым и вторым выходами прерывания усуройства/ первый вход - выход первого реверсивного коммутатора и второй вход - выход второго реверсивного коммутатора соединены соответственно с первым и вторым информационными входами - вькодами устройства, введены группа блоков памяти, пер,вая и вторая группы реверсивных коммутаторов, причем первый информационный вход - выход реверсивного коммутатора первой группы соединен с входом - выходом соответствующего блока памяти, первый информационный вход-выход реверсивного коммутатора второй группы соединен с вторым информационным входом-выходом преддаест вующего реверсивного коммутатора второй группы, и с вторым входом-выходом соОТветствукяцего реверсивного коммутатора первой группы, второй информационный вход-выход первого реверсивного кo лмyтaтopa соединен с первым информационным входомвыходом первого реверсивного коммутатора второй группы, первый информационный вход-выход второго реверсивного коммутатора соединен с вторыми информационными входамивыходами последних реверсивных коммутаторов первой и второй групп, управляющие входы реверсивных коммутаторов первой и второй групгг . , , соединены с соответствую1цими вы- ходами группы разряжающих выходов блока управления.

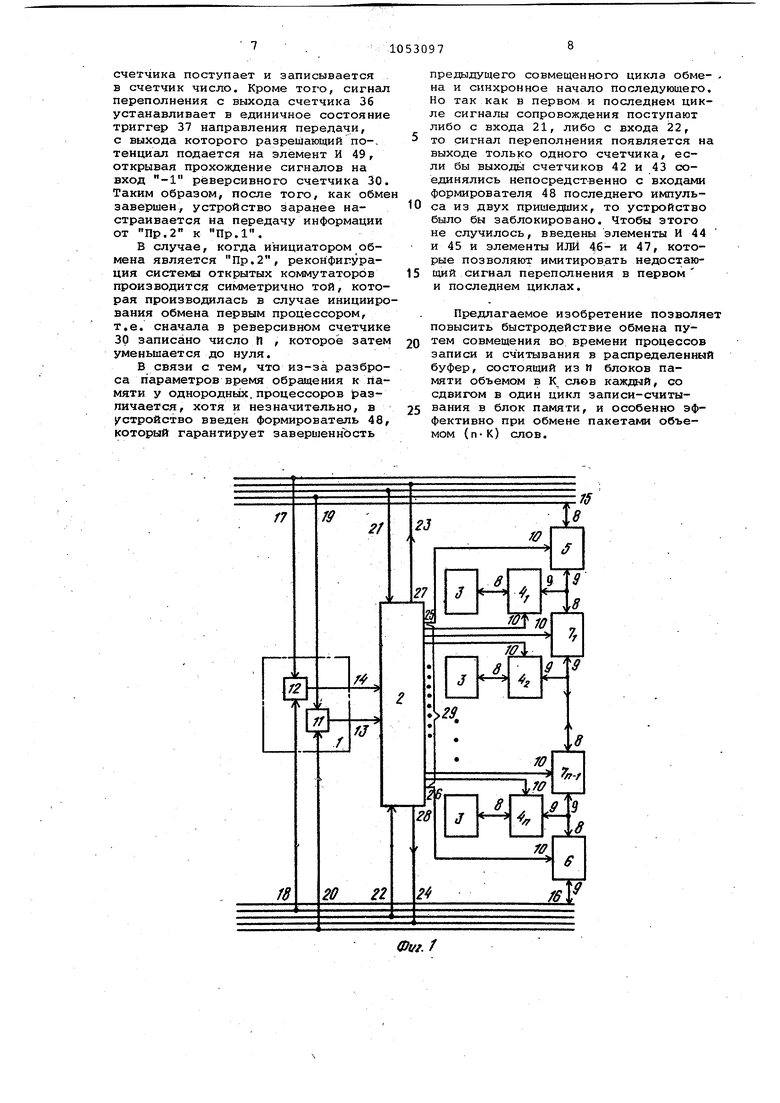

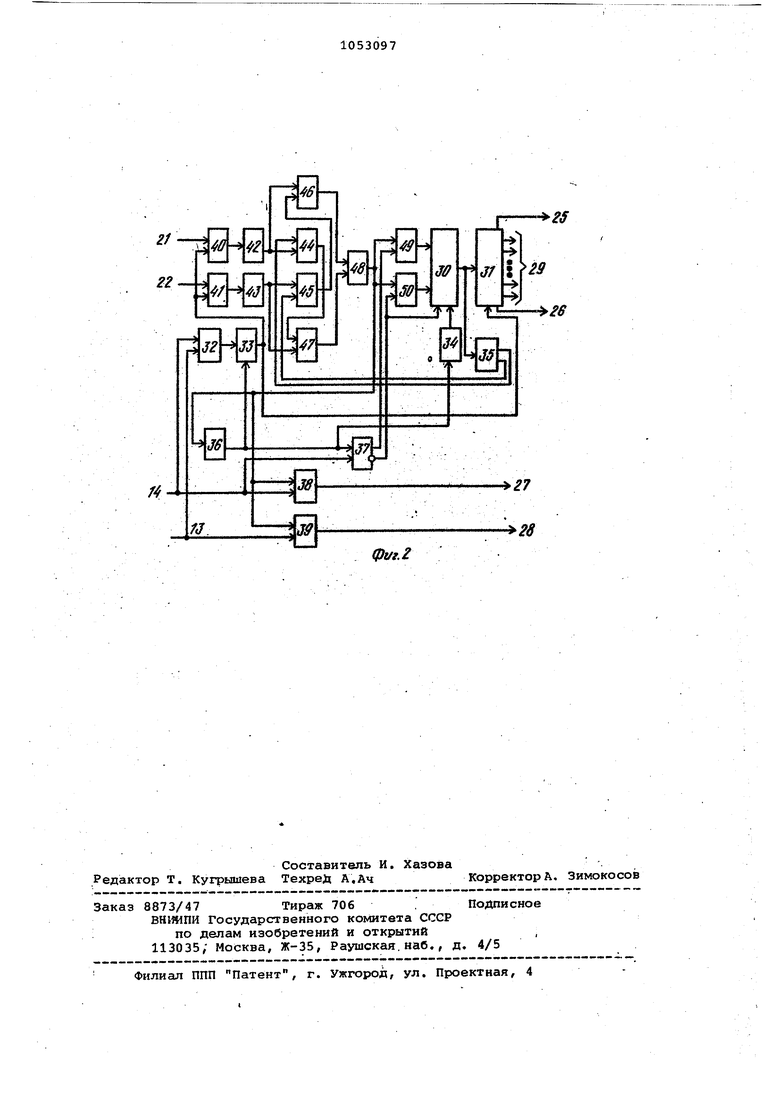

Блок управления содержит шесть элементов И, пять элементов ИЛИ, три счеТчика, реверсивный счетчик, шифратор, дешифратор состояния, дешифратор цикла, формирователь импульса, триггер разрешения обмена и триггер направления передачи, причемпервый, второй входы блока соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых и управляющий вход дешифратора состояния соединены с выходом триггера разрешения обмена, выходы первого и второго элементов И соединены соответственно с .входами первого и второго счетчиков, выход первого счетчика соединен с цервыми входами третьего элемента И и первого элемента ИЛИ, выход второго счетчика соединен , с первыми входс1ми четвертого элемента И и второго элемента ИЛИ вторые входы третьего и четвертого элементов К соединены соответственно с первым и вторым выходами дешифратора цикла, выходы третьего и четвертого элементов И соединены соответственно с вторыми входами вто- : рого и первого элементов ИЛИ, ВЫходы которых через формирователь импульса соединены с первыми входами пятого, шестого элементов И, третьего, четвертого элементов ИЛИ и с входом третьего счетчика, второй вход пятого элемента И соединен с прямым выходом триггера направления передачи, инверсный выход которого соединен с вторым входом шестого элмента И и сбросовым входом реверси8 ного счетчика, суммирующий и вычитающий входы которого соединены соответственно с выходами пятого и шестого элементов И, а вход параллельной записи - через шифратор - с выхдом третьего счетчика, выход реверсивного счетчика соединен с информационными входами дешифратора состояния и дешифратора цикла, второй вход четвертого элемента ИЛИ и первый вход пятого элемента ИЛИ являются третьим входом блока, вторые входы третьего и пятого элементов ИЛИ и первый Вход триггера направления передачи являются четвертым входом блока, выход пятого элемента ИЛИ соединен с первым входом триггра разреигения обмена, второй вход которого и Второй вход триггера направления передачи соединены с выходом третьего счетчика, группа выходов дешифратора состояния является группой разрешающих выходов блока, первый и второй выходы дешифратора состояния,, выходы третьего и четвертого элементов ИЛИ являются соответственно первым, вторым третьим и четвертым выходами блока.

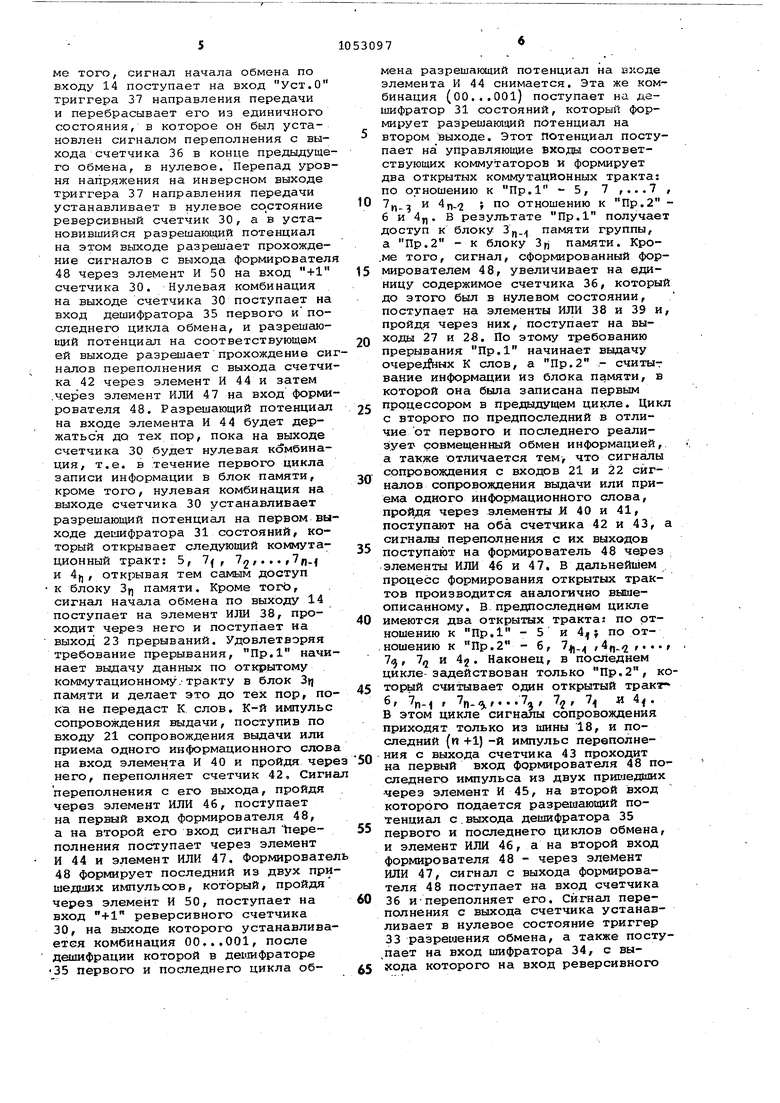

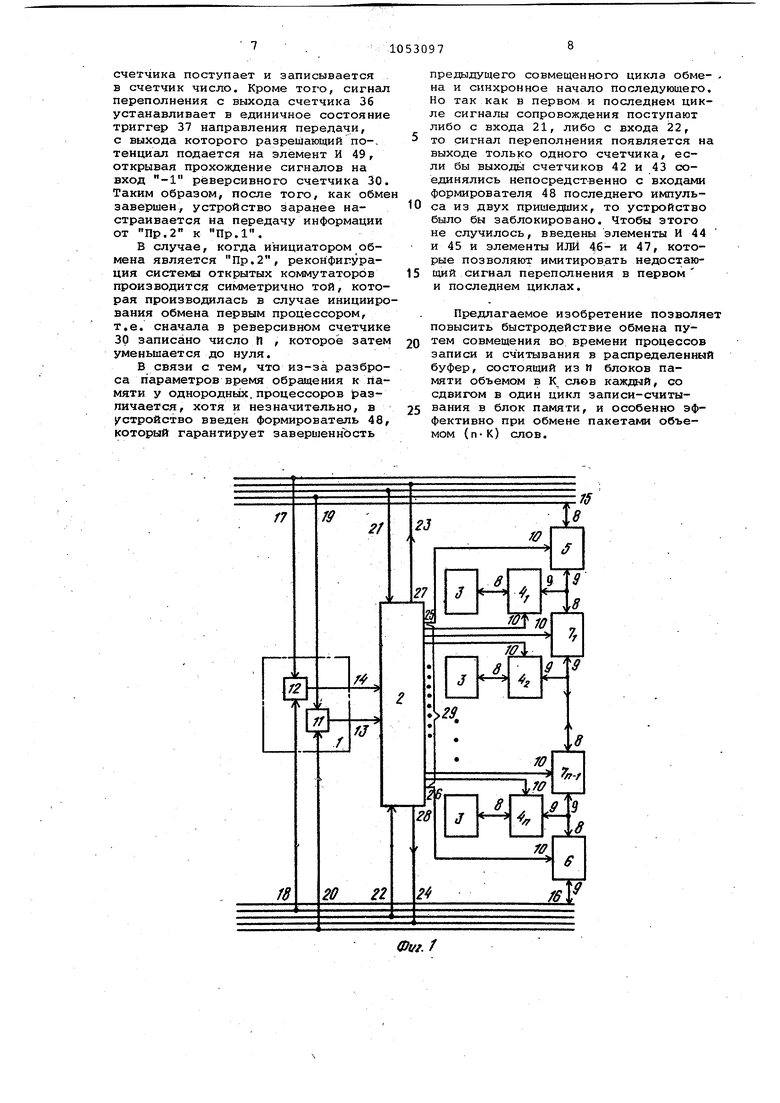

На фиг. 1 представлена структурная схема устройства} на фиг. 2 структурная схема блока управления. .

Устройство содержит блок 1 запуска обмена, блок 2 управления, группу блоков 3 памяти, первую груп0пу реверсивных коммутаторов 4.(-4,, первый 5 И второй б реверсивные . коммутаторы, вторую группу реверсивных коммутаторов 7|-7f, , первый 8 и второй 9 информационные входы-выходы реверсивных коммута5торов, управляющие входы 10 реверсив ного коммутатора, элементы И 11 и 12 блока запуска обмена, выходы 13и 14 блока запуска обмена, первый 15 и второй 16 информационные входы-вы0ходы, первый 17 ивторой 18 запросные входы, -первый 19 и второй 20 входы готовности, первый 21 и второй 22 входы сопровождения, первый 23 и второй 24 выходы прерывания, первый

5 25, второй 26, третий 27 и четвертый 28 выходы блока управления, груп пу 29 разрешаклцих выходов блока управления.

Блок управления содержит-(фиг.2)

0 реверсивный счетчик 30, дешифратор 31 состояния, элемент или 32, триг- . , гер:33 разрешения обмена, шифратор 34, дешифратор 35 цикла, счетчик 36, триггер 37 направления передачи,

5 элементы ИЛИ 38 и 39, элементы И 40 и 41, счетчики 42 и 43, элементы И 44 и 45, элементы ИЛИ 46 и 47, формирователь 48 импульса, элементы И 49 и 50.

Устройство работает следующим об0разом.

Пусть инициатором обмена будет тот Процессор, чья шинная магистраль на фиг. 1 расположена сверхуi Назовем его Пр.1, а другой, участ5вующий в обмене, - Пр.2. Если первому процессору .необходимо передать пакет информации в Пр.2, он по шине 17 посылает сигнал запроса на обмен в блок 1- запуска обмена/.

0 Если на второй вход элемента И 12 по входу 18 подается разрешающий потенциал, соответствующий готовности Пр.2 к приему пакета, то на выходе 14 блока 1 запуска обмена

5 появляется сигн.ал начала обмена, который, пройдя через элемент ИЛИ 32, перебрасывает триггер 33 разрешения обмена в единичное состояние, и на его выходе устанавливается раз0решающий потенциал, который снимает запрет дешифрации в дешифраторе 31 состояний и разрешает прохождение сигналов с входов 21 и 22 сигналов сопровождения выдачи или приема 5 Рдного информационного слова. Кроме того, сигнал начала обмена по входу 14 поступает на вход Уст.О триггера 37 направления передачи и перебрасывает его из единичного состояния, в которое он был установлен сигналом переполнения с выхода счетчика 36 в конце предыдущего обмена, в нулевое. Перепад уровня напряжения на инверсном выходе триггера 37 направления передачи устанавливает в нулевое состояние реверсивный счетчик 30, а в установившийся разрешающий потенциал на этом выходе разрешает прохождение сигналов с выхода формирователя 48 через элемент И 50 на вход +1 счетчика 30. Нулевая комбинация на выходе счетчика 30 поступает на вход дешифратора 35 первого и последнего цикла обмена, и разрешеиощий потенциал на соответствующем ей выходе разрешает прохождение сигналов переполнения с выхода счетчика 42 через элемент И 44 и затем .через элемент ИЛИ 47 на вход формирователя 48. Разрешающий потенциал на входе элемента И 44 будет держаться до тех пор, пока на выходе счетчика 30 будет нулевая кбмбинация, т.е. в течение первого цикла записи информации в блок памяти, кроме того, нулевая комбинация на выходе счетчика 30 устанавливает разрешающий потенциал на первом выходе дешифратора 31 состояний, который открывает следующий коммутационный тракт: 5, 7( , 72,...,7п.{ и 4)j , открывая тем самым доступ к блоку 3f) памяти. Кроме того, сигнал начала обмена по выходу 14 поступает на элемент ИЛИ 38, проходит через него и поступает на выход 23 прерываний. Удовлетворяя требование прерывания, Пр.1 начинает выдачу данных по открытому коммутационному/тракту в блок 3ц памяти и делает это до тех пор, пока не передаст К слов, К-й импульс сопровозкдения выдачи, поступив по входу 21 сопровождения выдачи или приема одного информационного слова на вход элемента И 40 и пройдя через него, переполняет счетчик 42, Сигнал переполнения с его выхода, пройдя через элемент ИЛИ 46, поступает на первый вход формирователя 48, а на второй его вход сигнал переполнения поступает через элемент И 44 и элемент ИЛИ 47. Формирователь 48 формирует последний из двух приедших импульсов, который, пройдя ерез элемент И 50, поступает на ход +1 реверсивного счетчика 0, на выходе которого устанавливатся комбинация 00...001, после ешифрации которой в деишфраторе 5 первого и последнего цикла обмена разрешающий потенциал на входе элемента И 44 снимается. Эта же комбинация (00...001) поступает на. дешифратор 31 состояний, который формирует разрешающий потенциал на 5 втором выходе. Этот потенциал поступает на управляющие входы соответствующих коммутаторов и формирует два открытых коммутационных тракта: по отношению к Пр.1 - 5, 7 ,...7 , 10 n-i n-i п° отношению к Пр.2 6 и 4„. В результате Пр.1 получает доступ к блоку 3,.;) памяти группы, а Пр.2 - к блоку Зп памяти. Кро.ме того, сигнал, сформированный фор15 мирователем 48, увеличивает на единицу содержимое счетчика 36, который до этого был в нулевом состоянии, поступает на элементы ИЛИ 38 и 39 и, пройдя через них, поступает на вы0 ходы 27 и 28. По этому требованию прерывания Пр.1 начинает выдачу очеред ных К слов, а Пр.2 - считыг вание информации из блока памяти, в которой она была записана первым 25 процессором в предыдущем цикле. Цикл с второго по предпоследний в отличие от первого и последнего реализует совмещенный обмен информацией, а также отличается тем, что сигналы сопровождения с входов 21 и 22 сйг налов сопровождения выдачи или приема одного информационного слова, пройдя через элементы Я 40 и 41, поступают на оба счетчика 42 и 43, а сигналы переполнения с их выходов

5 поступают на формирователь 48 через элементы ИЛИ 46 и 47, В дальнейшем процесс формирования открытых трактов производится аналогично вышеописанному, В. предпоследнем цикле

0 имеются два открытых тракта по отношению к Пр,1 - 5 и портношению к Пр,2 - 6, 7|,. ,п-1 7t, 7 и 4j. Наконец, в последнем цикле-задействован только Пр.2, ко5 торый считывает один открытый тракт6, 7. , 7./5,, . .7 , 7 , 7 и 4| . В этом цикле сигнсшы сопровозкдения приходят только из шины 18, и последний (п +1) -и импульс переполнел ния с выхода счетчика 43 проходит

на первый вход формирователя 48 последнего импульса из двух пршяедших через элемент И 45, на второй вход которого подается разрешающий потенциал с.выхода дешифратора 35

первого и последнего циклов обмена, и элемент ИЛИ 46, а на второй вход формирователя 48 - через элемент ИЛИ 47, сигнал с выхода формирователя 48 поступает на вход счетчика

0 36 и-переполняет его. Сигнал переполнения с выхода счетчика устанавливает в нулевое состояние триггер 33 разрешения обмена, а также посту,пает на вход шифратора 34, с вы5 кода которого на вход реверсивного

счетчика поступает и записывается в счетчик число. Кроме того, сигнал переполнения с выхода счетчика 36 устанавливает в единичное состояние триггер 37 направления передачи, с выхода которого разрешающий по-, тенциал подается на элемент И 49, открывая прохождение сигналов на вход -1 реверсивного счетчика ЗО. Таким образом, после того, как обме завершен, устройство заранее настраивается на передачу информации от Пр.2 к Пр.1.

В случае, когда инициатором обмена является Пр.2, реконфигурация системы открытых коммутаторов производится симметрично той, которая производилась в случае инициирования обмена первым процессором, т.е. сначала в реверсивном счетчике 30 записано число П , которое затем уменьшается до нуля.

В связи с тем, что из-за разброса параметров время обращения к памяти у однородньах. процессоров различается, хотя и незначительно, в стройство введен формирователь 48, который гарантирует завершенность

предыдущего совмещенного цикла обме- . на и синхронное начало последующего. Но так как в первом и последнем цикле сигналы сопровождения поступают либо с входа 21, либо с входа 22,

то сигнал переполнения появляется на выходе только одного счетчика, если бы выходы счетчиков 42 и 43 соединялись непосредст-венно с входами формирователя 48 последнего импульса из двух пришедших, то устройство было бы заблокировано. Чтобы этого не случилось, введены элементы И 44 и 45 и элементы ИЛИ 46- и 47, которые позволяют имитировать недостающи и сигнал переполнения в первом и последнем циклах.

Предлагаемое изобретение позволяет повысить быстродействие обмена путем совмещения во времени процессов записи и считывания в распределенный буфер, состоящий из W блоков памяти объемом в К слов каждый, со сдвигом в один цикл записи-считывания в блок памяти, и особенно эффективно при обмене пакетами объемом (п-К) слов.

Фш. /

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена информацией | 1977 |

|

SU734655A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессов | 1974 |

|

SU507866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-07—Публикация

1982-05-11—Подача