1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах.

Цель изобретения - повышение надежности устройства.

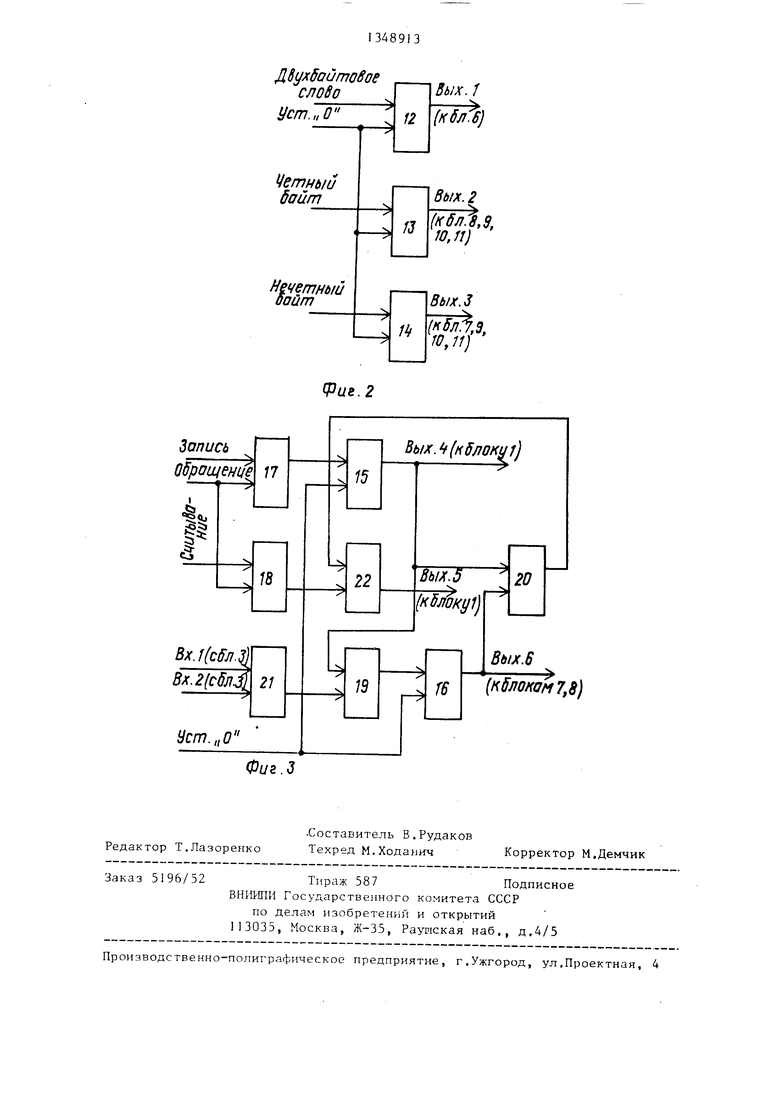

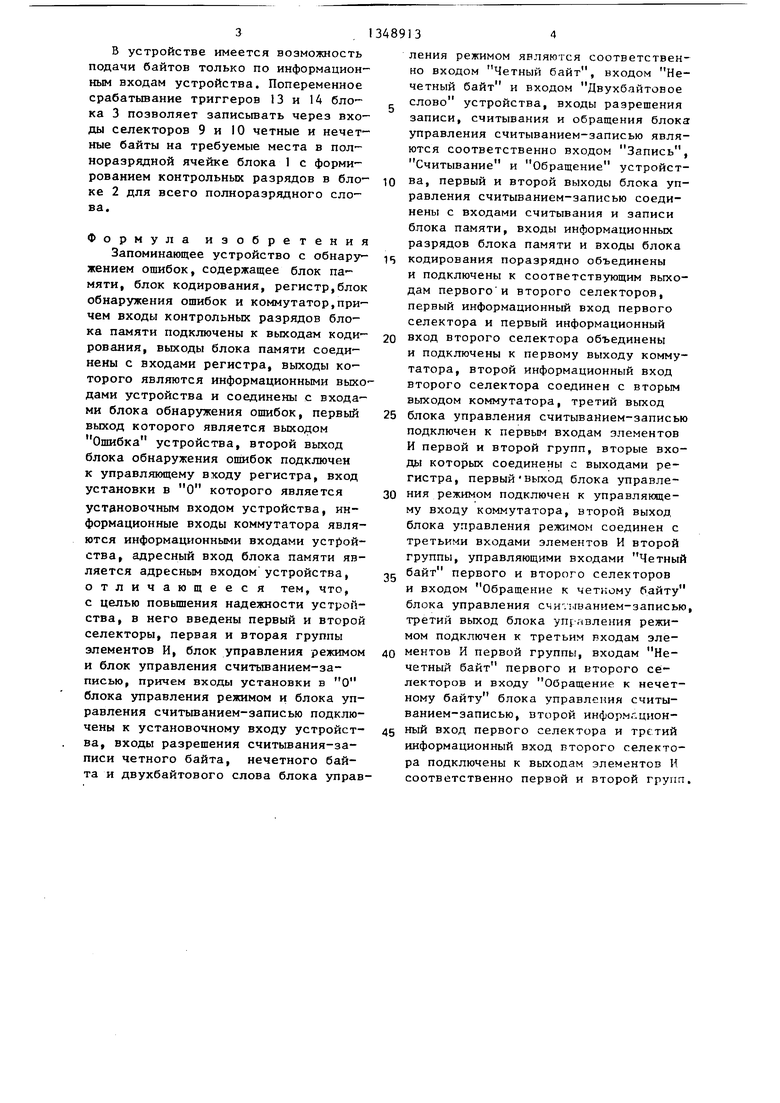

На фиг.1 представлена функциональная схема запоминающего устройства; на фиг, 2 и фиг, 3 - примеры выпол- нения функциональных схем блока управления режимом и блока управления считьтанием-записью соответственно.

Запоминающее устройство содержит (фиг,1) блок 1 памяти, блок 2 кодиро вания, блок 3 управления режимом,регистр 4, блок 5 обнаружения ошибок, коммутатор 6, первую группу элементов И 7, вторую группу элементов И 8 первый селектор 9, второй селектор 10, блок II управления считыванием- записью,

Блок 3. содержит (фиг,2) первый триггер 12, второй триггер 13 и третий триггер 14,

Блок II содержит (фиг,3) первый триггер 15, второй триггер 16, четыре элемента И 17-20 и два элемента ИЛИ 21 и 22.

Устройство работает следующим образом.

Перед началом работы в устройство поступает сигнал Установка О, который устанавливает все элементы и блоки в исходное состояние.

В режиме записи и считывания полных двухбайтовых слов устройство работает следующим образом,

В режиме записи на элемент И 17 блока 11 поступают сигналы Запись и Обращение, которые устанавливают триггер 12 в состояние 1. На коммутатор 6 с информационных входов устройства подается код записываемого слова, который через селекторы 9 и 10 передается на запись в блок 1 и на блок 2 для формирования контрольных разрядов слова. С блока 2 контрольные разряды также передаются в блок 1 для записи вместе с пос- тупившим словом. Управляет записью полного слова триггер 12 блока 3, на который при этом поступает управляющий сигнал, устанавливающий его в состояние 1,

В режиме считывания информации на элемент И 18 блока И подается управляющий потенциал Считывание, и сигнал Обращение через элемент

132

И 18, элемент ИЛИ 22 запускает блок 1. Из блока 1 в регистр 4 счи- тьшается полноразрядное слово вместе с контрольными разрядами. Это слово передается на информационные выходы устройства и вместе с контрольными разрядами на блок 5, где осуществляется контроль и коррекция счи тьшаемой информации. При обнаружении некорректируемой ощибки в блоке 5 формируется сигнал Ошибка, сигнализирующий процессору (не показан) о наличии неисправности в запоминающем устройстве. При обнаружении коррек - тируемой ошибки блок 5 исправляет в необходимом порядке информацию, и на информационные выходы выдается правильный код.

Рассмотрим работу устройства при обработке неполных слов (отдельно четных и начетных байтов). При этом хранение информации в блоке 1 осуществляется все равно полньми двухбайтовыми словами. При работе с четными байтами сигналом с входа Четный байт устанавливается в состояние J триггер 13 блока 3. Сигнал разрешения с этого триггера отк- рьшает элементы И 8 и управляет работой селектора 9.

В режиме записи сигналами с входов Запись и Обращение через элемент И 17 устанавливается в состояние 1 триггер 15 блока 11, разрешая тем самым запись информации в блок 1. Сигналом с триггера 13 блока 3 через элемент ИЛИ 21 и элемент И 19 блока II устанавливается в состояние I триггер 16, который отк- рьшает элементы И 8 и через элемент И 20 и элемент ИЛИ 22 блока 11 производит считьюание уже записанного в блок 1 четного байта, который с регистра 4 подается через элементы И 8 и селектор 10 на запись в блок 1 одновременно с четным байтом, который передается на блок 1. с информа-. ционных входов устройства через коммутатор 6 и селектор 9. Одновременно в блоке 2 формируются контрольные разряды полного слова (вновь поступившего четного байта и записанного ранее нечетного байта, которые также записьшаются в блок 1).

Аналогично производится запись нечетного байта и формирование контрольных разрядов для всего слова.

в устройстве имеется возможность подачи байтов только по информационным входам устройства. Попеременное срабатьшание триггеров 13 и 14 блока 3 позволяет записьшать через входы селекторов 9 и 10 четные и нечетные байты на требуемые места в полноразрядной ячейке блока 1 с формированием контрольных разрядов в блоке 2 для всего полноразрядного слова.

Формула изобретения Запоминающее устройство с обнаружением ошибок, содержащее блок памяти, блок кодирования, регистр,блок обнаружения ошибок и коммутатор,причем входы контрольных разрядов блока памяти подключены к выходам кодирования, выходы блока памяти соединены с входами регистра, выходы которого являются информационными выходами устройства и соединены с входами блока обнаружения ошибок, первый выход которого является выходом Ошибка устройства, второй выход блока обнаружения ошибок подключен к управляющему входу регистра, вход установки в О которого является установочным входом устройства, информационные входы коммутатора являются информационными входами ства, адресный вход блока памяти является адресным входом устройства, отличающееся тем, что, с целью повьшения надежности устройства, в него введены первый и второй селекторы, первая и вторая группы элементов И, блок управления режимом и блок управления считьшанием-за- писью, причем входы установки в О блока управления режимом и блока управления считьюанием-записью подключены к установочному входу устройства, входы разрешения считывания-записи четного байта, нечетного байта и двухбайтового слова блока управ489134

ления режимом являются соответственно входом Четный байт, входом Нечетный байт и входом Двухбайтовое слово устройства, входы разрешения записи, считывания и обращения блока управления считыванием-записью являются соответственно входом Запись, Считывание и Обращение устройст10 ва, первый и второй выходы блока управления считыванием-записью соединены с входами считывания и записи блока памяти, входы информационных разрядов блока памяти и входы блока

IS кодирования поразрядно объединены и подключены к соответствующим выходам первого и второго селекторов, первый информационный вход первого селектора и первый информационный

20 вход второго селектора объединены и подключены к первому выходу коммутатора, второй информационный вход второго селектора соединен с вторым выходом коммутатора, третий выход

25 блока управления считыванием-записью подключен к первым входам элементов И первой и второй групп, вторые входы которых соединены с выходами регистра, первый ВЫХОД блока управле30 НИН режимом подключен к управляющему входу коммутатора, второй выход блока управления режимом соединен с третьими входами элементов И второй группы, управляющими входами Четный

2g байт первого и второго селекторов и входом Обращение к четкому байту блока управления счи .мванием-записью, третий выход блока управления режимом подключен к третьим входам эле40 ментов И первой группы, входам Нечетный байт первого и второго cei- лекторов и входу Обращение к нечетному байту блока управления считыванием-записью, второй информг.цион45 ный вход первого селектора и третий информационный вход второго селектора подключены к выходам элементов И соответственно первой и второй групп.

Д6ух5айтовое слоёо

Уст. „О

Четный байт

Нечетньш Ва

wum

иг.2

Фиг.З

Редактор Т.Лазоренко

-Составитель В.Рудаков Техред М.Ходанич

Заказ 5196/52Тираж 587Подписное

ВНИ-ШН Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

12

Вых. 1 ,

(кблб)

/J

Вых. 2

(к 6л.8.9, Ю, Л)

1h

Вых. 3

(.

Ю,11

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Запоминающее устройство | 1990 |

|

SU1805496A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство управления для кассетной памяти на цилиндрических магнитных доменах | 1987 |

|

SU1495850A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и устройствах. Цель изобретения - повьппение надежности работи. Запоминающее устройство содержит блок 1 памяти, блок 2 кодирования, блок 3 управления режимом, регистр 4, блок 5 обнаружения ошибок, коммутатор 6, две группы элементов И 7, 8, селекторы 9, 10, блок 11 управления считьшаниеь:-записью. Устройство формирует контрольные коды для любого формата поступающей информации, причем производятся контроль вновь поступающей информации вместе с ранее записанной, что улучшает качество контроля 1П фор 5Лции в блоке памяти. Кроме того, обеспечена воз- можность работы как с полноразр5щны- ми двухбайтовыми словами, так и с отдельными четйыми ч чгчетчычп байтами с автоматичес i (,...р,-;,-.рС оакием слов и контрольных ьолс. . в блоке памяти и распределением o. L/ oi но словам . 3 ИГ: . S 00 4 00 СО Выходное I ИРГИяЛ-:

| Оперативное запоминающее устройство | 1972 |

|

SU483705A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-10-30—Публикация

1986-02-06—Подача