1

Изобретение относится к вычислительной технике и может быть исполь- зовацо при проектировании самоконтро- лнруемых микропроцессоров.

Цель изобретения - повышение достоверности контроля.

Сущность изобретения заключается в повышении достоверности функционирования путем организации контроля правильности реализации переходов при выполнении микрокоманд безусловных переходов за счет использования свободного ПОЛЯ управления логикой признаков в формате считьшаемых микрокоманд.

. Устройство функционирует следующим образом.

Блок модификации адреса, выполненный на микропроцессоре, производит управление формированием адресов микрокоманд, считываемых из блока памяти микрокоманд, а также обработку признаков, поступающих от центрального процессорного элемента. По сформи рованному адресу микрокоманды из бло ка памяти микрокоманд происходит ее считывание. Считанная, микрокоманда записывается в регистр микрокоманд. Информация с выхода этого регистра, в зависимости от ее назначения, используется следующим образом. Управляющая часть микрокоманды поступает на объект управления, а информация, управляющая переходом к очередному адресу микропрограммы,, - в блок модификаций адреса. В зависимости от того, какая микрокоманда считана и каким образом осуществляется переход к адресу очередной микрокоманды, в устройстве происходит контроль правильности переходов в микропрограмме на основании сравнения адреса микрокоманды перехода и того адреса, к которому необходимо перейти.

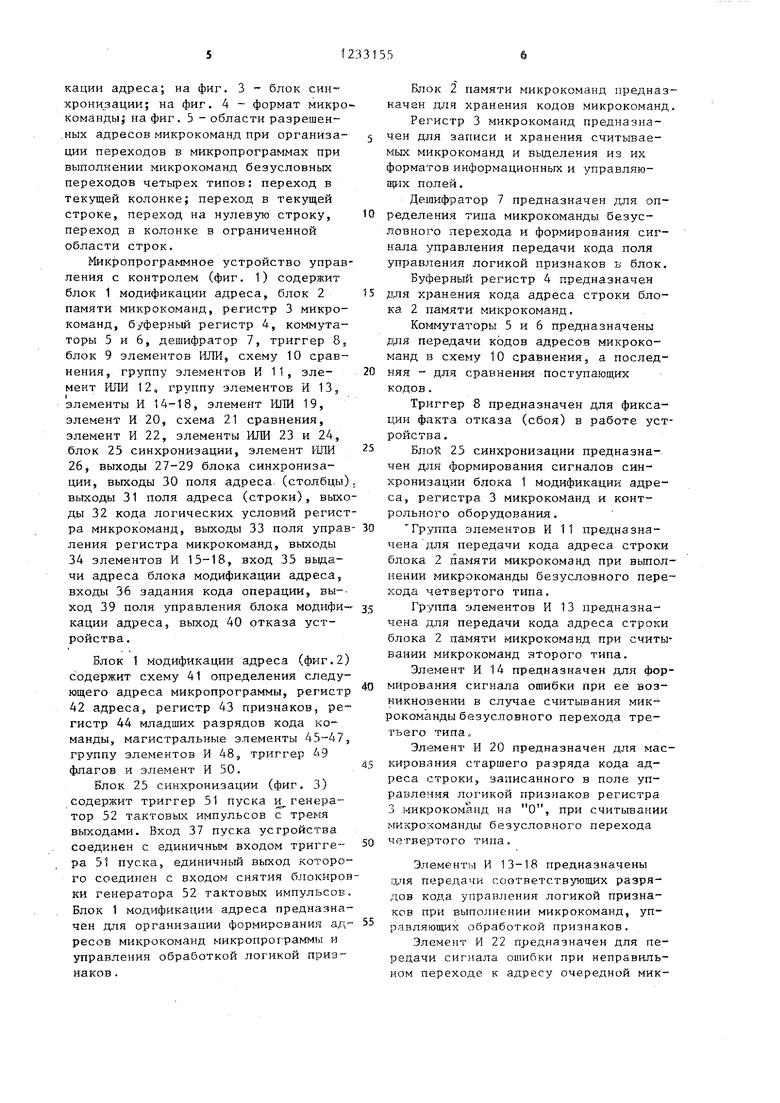

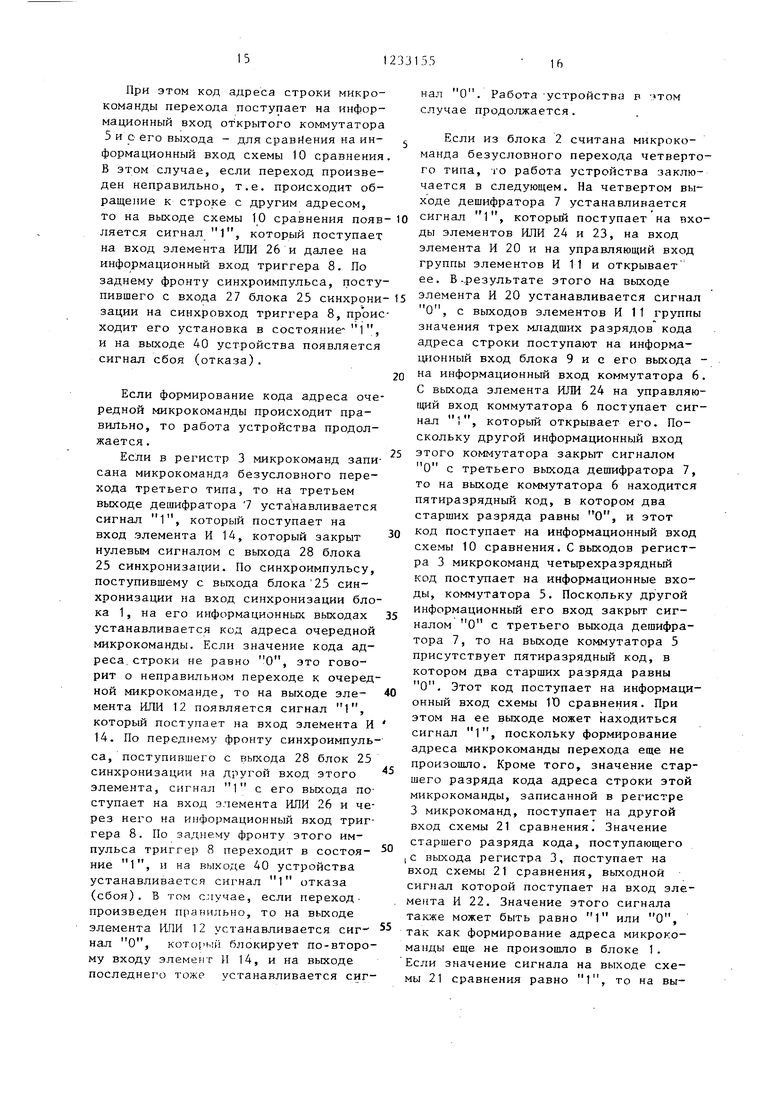

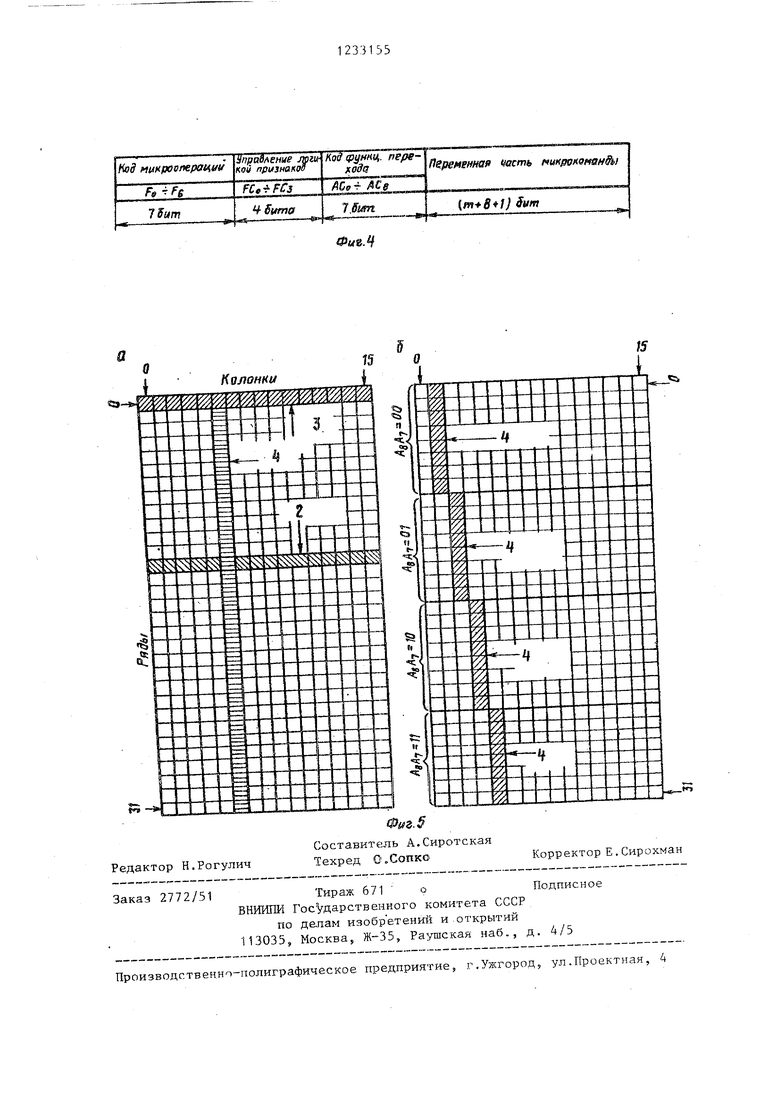

В предлагаемом устройстве в множестве команд реализуется четьфе типа команд безусловных переходов : переход в текущей колонке| переход в текущей строке; переход в нулевую строку; пе реход в любую строку в заданной колонке в ограниченной области строк.

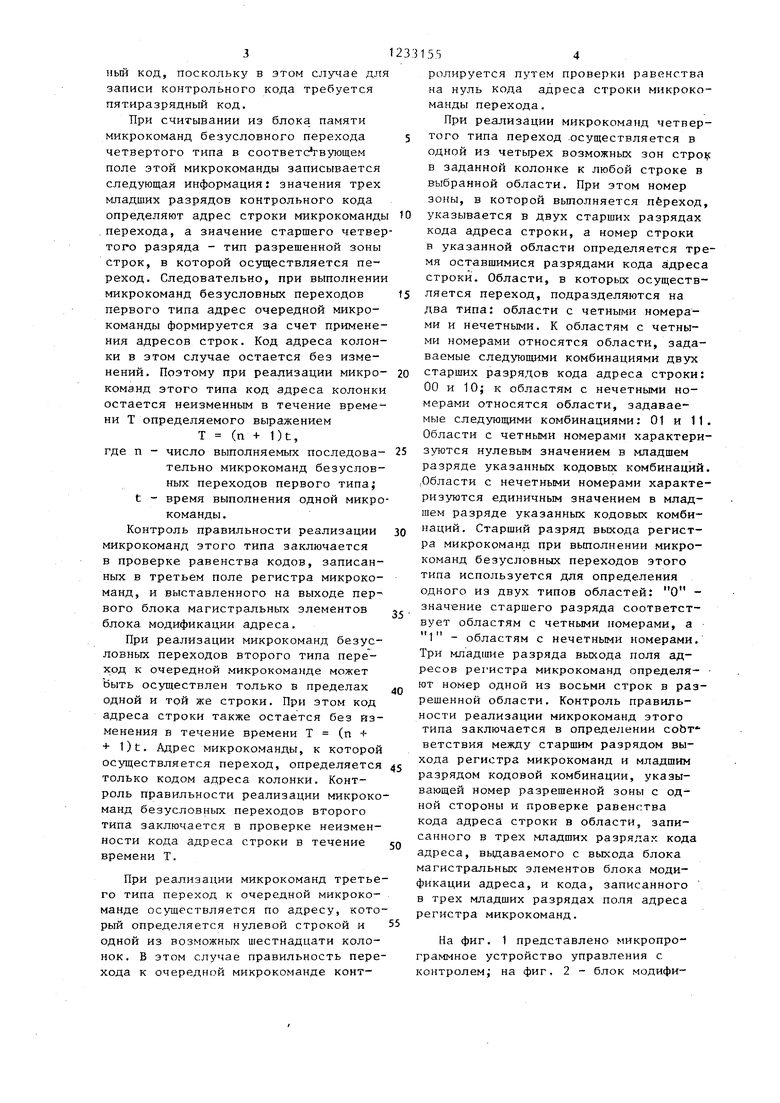

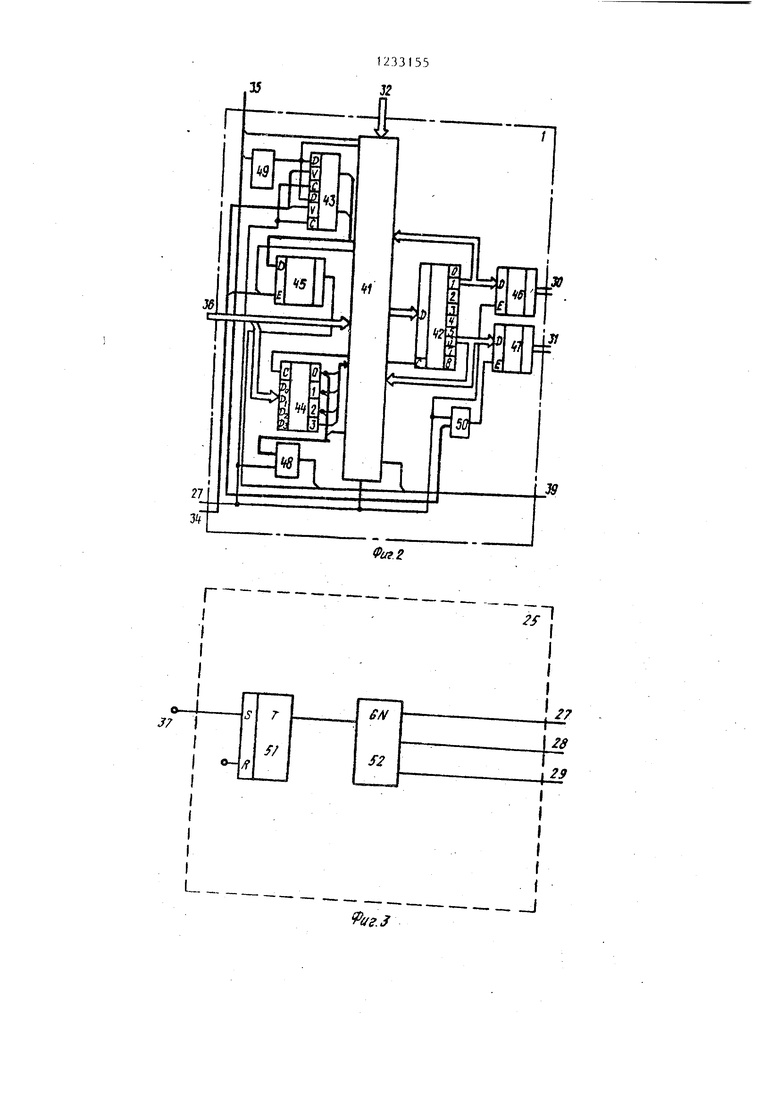

Формат считываемых микрокоманд из блока памяти микрокоманд состоит из следующих полей: поля кода микроопераций; поля управления логикой признаков; поля кода функпий перехода к слегдующему адресу микропрограммы и нескольких полей переменной час

25

331552

ти микрокоманды. В первом поле задается код микроопераций, во втором поле содержится информация, управляю- га;ая логикой записи признаков и их 5 считывания, в третьем поле - информация о типе перехода к следующему адресу микропрограммы и в полях переменной части микрокоманды - информация о коде маски, константы и т.д. 10 Устройство функционирует с блоком памяти микрокоманд матричного типа. Для задания адреса ячейки такого блока памяти необходимо задавать адрес строки и адрес колонки. Блоки 5 памяти матричного типа содержат 32 строки и 16 колонок,-чем обеспечивается хранение 512 микрокоманд. Для адресации ячеек памяти такого блока достаточно использовать девятираз- 2G рядный код, в котором первые четыре разряда задают адрес колонки, а оставшиеся пять разрядов - адрес строки. В процессе реализации заданных микропрограмм из блока памяти микрокоманд могут считываться микрокоманды как условных так и безусловных переходов. При этом независима от типа считываемых микрокоманд может выполняться или не выполняться управле- 30 ние логикой признаков. При вьшолне- . НИИ микрокоманд, реализация которых требует управления признаками (микрокоманды арифметических операций и логического сдвига), в соответствую- 35 щем поле записывается втравляющая . информация. В остальных микрокомандах ;iTo поле полезной информации для реализации тех или иных микрокоманд не н€1сет.

При считывании из блока памяти микрокоманд безусловных переходов такого типа в свободном поле задается контрольная информация, которая определяется типом микрокоманды безусловного перехода. При выполнении перехода к очередной микрокоманде по |Микрокоманде безусловного перехода первого типа переход осуществляется только в пределах той колонки, которая определяет адрес микрокоманды безусловного перехода. В этом случае в поле управления логикой признаков за.писывается код адреса колонки.

При считывании из блока памяти

55 микрокоманд безусловного перехода

второго и третьег.о типов разрядность

поля управления логикой признаков не

позволяет записывать в нем контроль-.

45

50

3

ньш код, поскольку в этом случае для записи контрольного кода требуется пятиразрядный код.

При считывании из блока памяти микрокоманд безусловного перехода четвертого типа в соответствующем поле этой микрокоманды записывается следующая информация: значения трех младших разрядов контрольного кода определяют адрес строки микрокоманды перехода, а значение старшего четвертого разряда - тип разрешенной зоны строк, в которой осуществляется переход. Следовательно, при выполнении микрокоманд безусловных переходов первого типа адрес очередной микрокоманды формируется за счет применения адресов строк. Код адреса колонки в этом случае остается без изменений. Поэтому при реализации микро- команд этого типа код адреса колонки остается неизменным в течение време ни Т определяемого выражением

Т (п + 1)t,

где п - число выполняемых последова- тельно микрокоманд безусловных переходов первого типа; t - время выполнения одной микрокоманды.

Контроль правильности реализации микрокоманд этого типа заключается в проверке равенства кодов, записанных в третьем поле регистра микрокоманд, и выставленного на выходе первого блока магистральных элементов блока модификации адреса.

При реализации микрокоманд безусловных переходов второго типа переход к очередной микрокоманде может быть осуществлен только в пределах одной и той же строки. При этом код адреса строки также остается без изменения в течение времени Т (п + + 1)t. Адрес микрокоманды, к которой осуществляется переход, определяется только кодом адреса колонки. Контроль правильности реализации микрокоманд безусловных переходов второго типа заключается в проверке неизменности кода адреса строки в течение времени Т.

При реализации микрокоманд третьего типа переход к очередной микрокоманде осуществляется по адресу, который определяется нулевой строкой и одной из возможных шестнадцати колонок. В этом случае правильность перехода к очередной микрокоманде контsШ Т520

25 ЗО5

JQ 45 jO

552331554

ролируется путем проверки равенства на нуль кода адреса строки микрокоманды перехода.

При реализации микрокоманд четвертого типа переход осуществляется в одной из четырех возможных зон строке в заданной колонке к любой строке в выбранной области. При этом номер зоны, в которой вьшолняется переход, указывается в двух старших разрядах кода адреса строки, а номер строки в указанной области определяется тремя оставшимися разрядами кода адреса строки. Области, в которых осуществляется переход, подразделяются на два типа: области с четными номерами и нечетными. К областям с четными номерами относятся области, задаваемые следующими комбинациями двух старших разрядов кода адреса строки: 00 и 10; к областям с нечетными номерами относятся области, задаваемые следующими комбинациями: 01 и 11. Области с четными номерами характеризуются нулевым значением в младшем разряде указанных кодовых комбинаций. (Области с нечетными номерами характеризуются единичным значением в младшем разряде указанных кодовых комбинаций. Старший разряд вьосода регистра микрокоманд при выполнении микрокоманд безусловнЕЯХ переходов этого типа используется для определения одного из двух типов областей: О - значение старшего разряда соответствует областям с четными номерами, а 1 - областям с нечетными номерами. Три младшие разряда выхода поля адресов рег истра микрокоманд определя- ют номер одной из восьми строк в разрешенной области. Контроль правильности реализации микрокоманд этого типа заключается в определении соЬт ветствия между старшим разрядом выхода регистра микрокоманд и младшим разрядом кодовой комбинации, указывающей номер разрешенной зоны с одной стороны и проверке равенства кода адреса строки в области, записанного в трех младших разрядах кода адреса, выдаваемого с выхода блока магистральных элементов блока модификации адреса, и кода, записанного в трех младших разрядах поля адреса регистра микрокоманд.

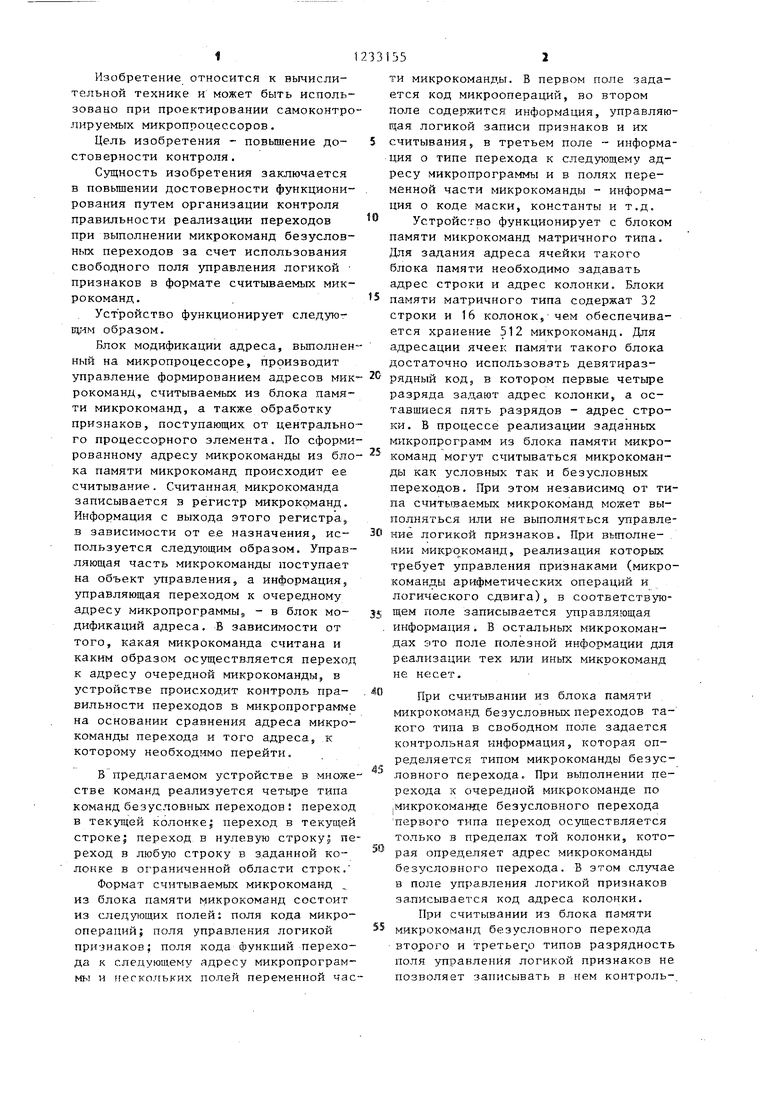

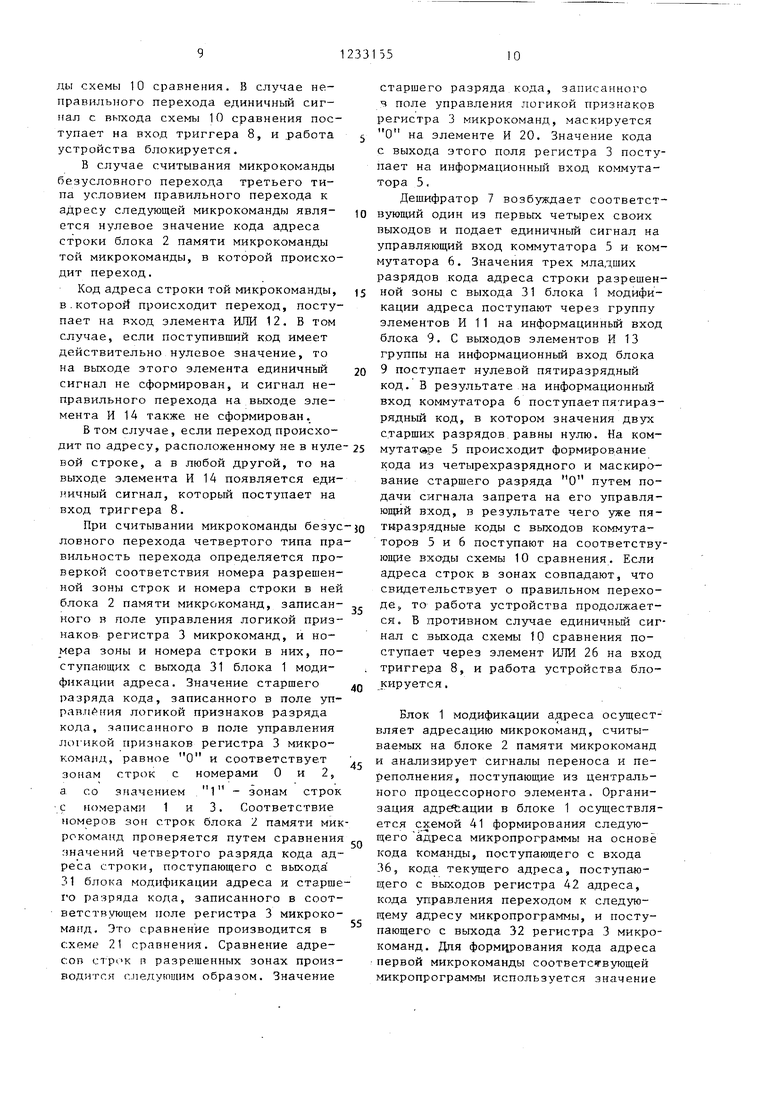

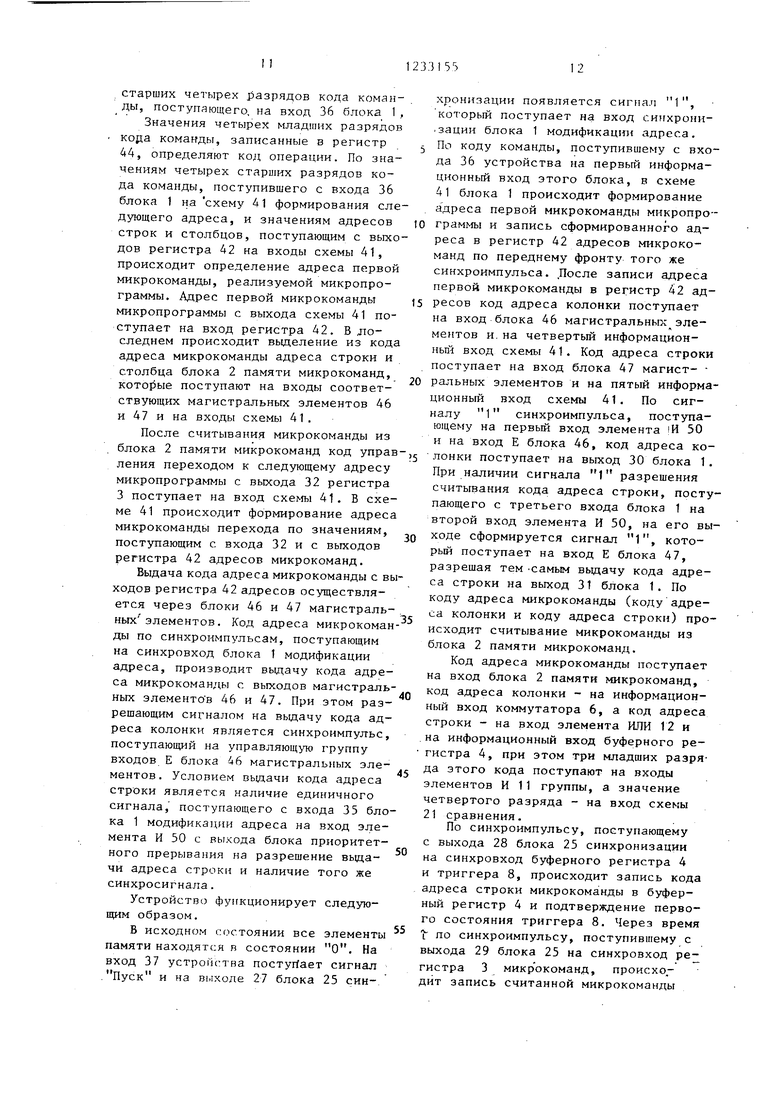

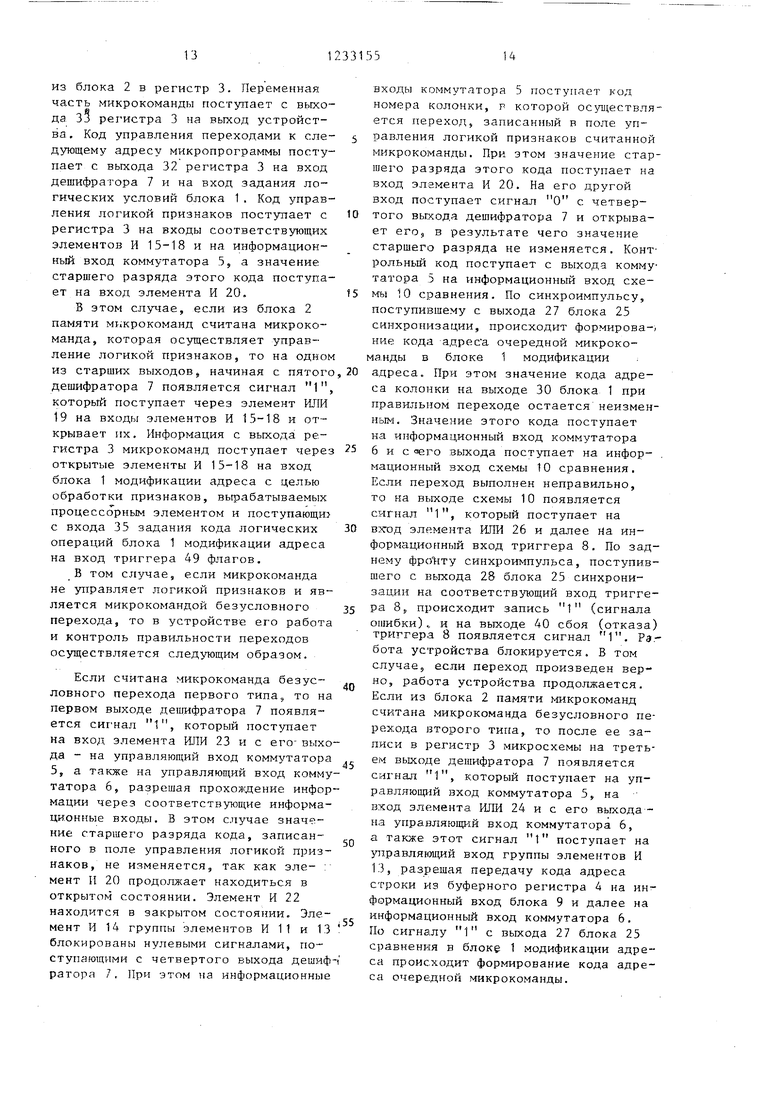

На фиг. 1 представлено микропрограммное устройство управления с контролем; на фиг, 2 - блок модифи

кацин адреса; на фиг. 3 - блок синхронизации; на фиг. 4 - формат микрокоманды; на фиг. 5 - области разрешен- .ных адресов микрокоманд при организа- ции переходов в микропрограммах при выполнении микрокоманд безусловных переходов четьфех типов: переход в текущей колонке; переход в текущей строке, переход на нулевую строку, переход в колонке в ограниченной области строк.

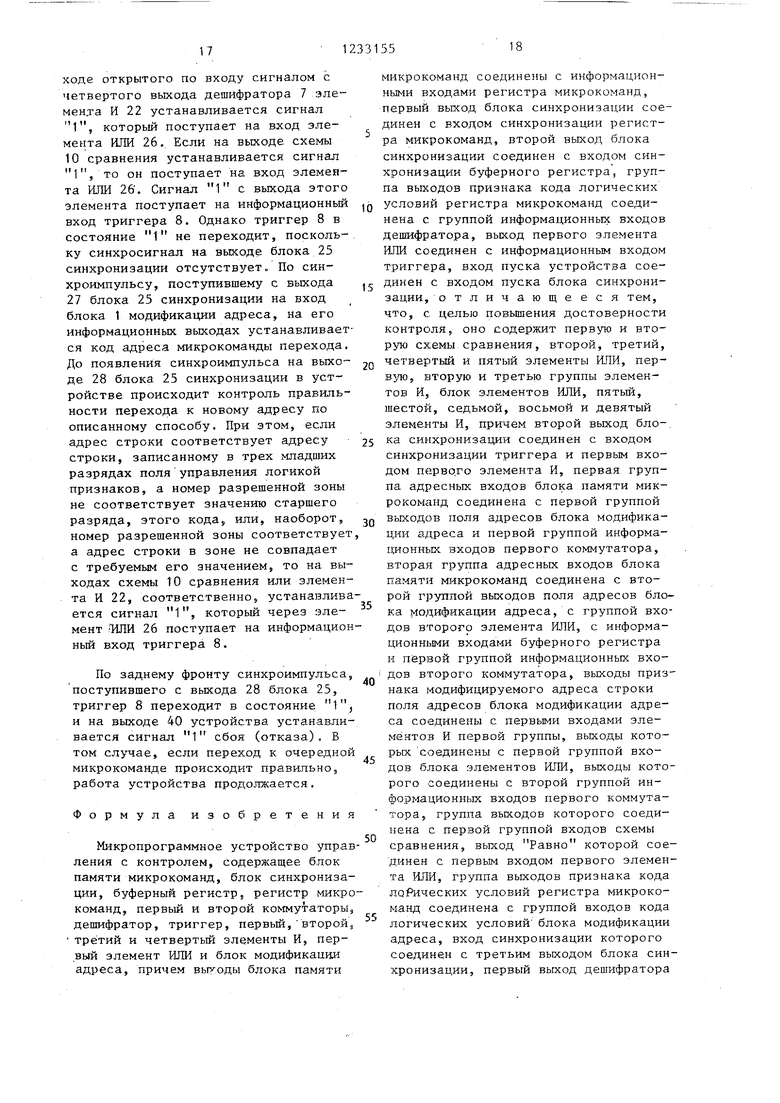

Микропрограммное устройство управления с контролем (фиг. 1) содержит блок 1 модификации адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд, буферный регистр 4, коммутаторы 5 и 6, дешифратор 7, триггер 8, блок 9 элементов ИЛИ, схему 10 сравнения, группу элементов И 11, эле- мент ИЛИ 12, группу элементов И 13, элементы И 14-18, элемент ШШ 19, элемент И 20, схема 21 сравнения, элемент И 22, элементы ИЛИ 23 и 24, блок 25 синхронизации, элемент ИЛИ 26, выходы 27-29 блока синхронизации, выходы 30 поля адреса, (столбцы) выходы 31 поля адреса (строки), выходы 32 кода логических условий регистра микрокоманд, выходы 33 поля управ ления регистра микрокоманд, выходы 34 элементов И 15-18, вход 35 выдачи адреса блока модификации адреса, входы 36 задания кода операции, вы-- ход 39 поля управления блока модифи- кации адреса, выход 40 отказа устройства.

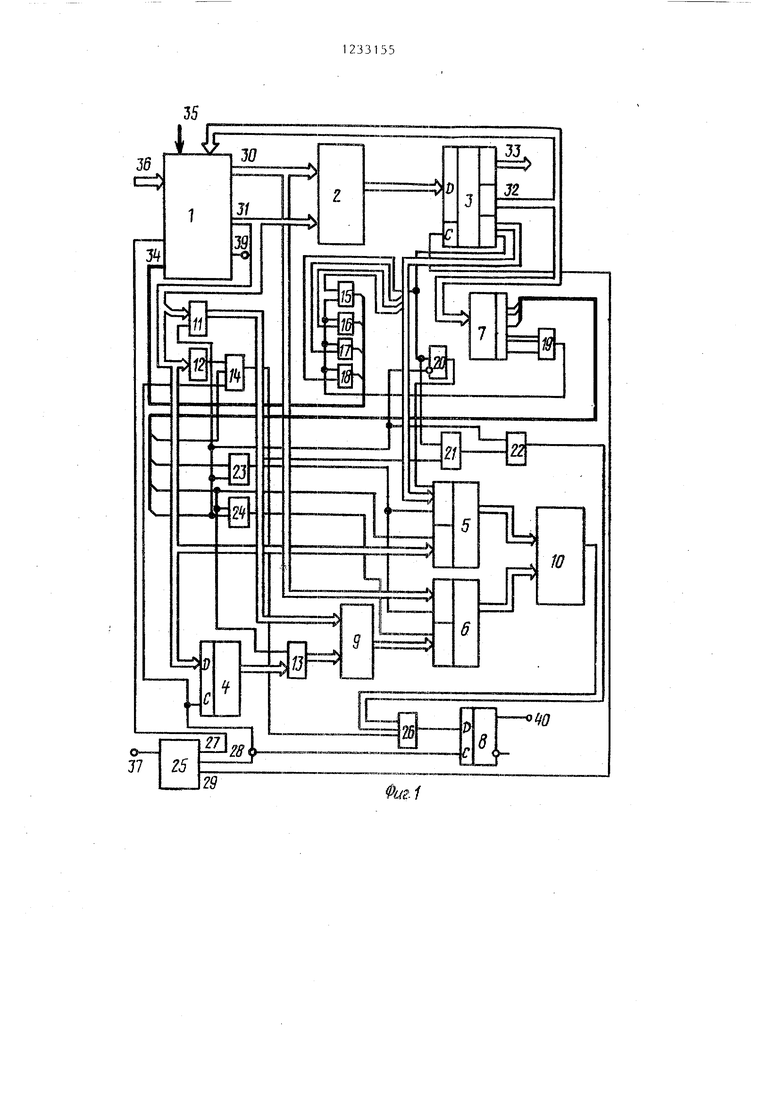

Блок 1 модификации адреса (фиг.2) содержит схему 41 определения следующего адреса микропрограммы, регистр 42 адреса, регистр 43 признаков, регистр 44 младших разрядов кода команды, магистральные элементы 45-47, группу элементов И 48, триггер 49 флагов и элемент И 50.

Блок 25 синхронизации (фиг. 3) содержит триггер 51 пуска и генератор 52 тактовых импульсов с тремя выходами. Вход 37 пуска устройства соединен с единичным входом тригге- ра 51 пуска, единичный вьсход которого соединен с входом снятия блокировки генератора 52 тактовых импульсов. Блок 1 модификации адреса предназначен для организации формирования ад ресов микрокоманд микропрограммы и управления обработкой логикой признаков .

5

О

5 0 0

0 5

Блок 2 памяти микрокоманд предназ- в:аче 1 для хранения кодов микрокоманд.

Регистр 3 микрокоманд предназначен для записи и хранения считываемых микрокоманд и выделения из их форматов информационных и управляющих полей.

Дешифратор 7 предназначен для определения типа микрокоманды безусловного перехода и формирования сигнала управления передачи кода поля управления логикой признаков в блок.

Буферный регистр 4 предназначен для хранения кода адреса строки блока 2 памяти микрокоманд.

Коммутаторы 5 и 6 предназначены даэя кодов адресов микрокоманд в схему 10 сравнения, а последняя для сравнения Поступающих кодов.

Триггер 8 предназначен для фиксации факта отказа (сбоя) в работе устройства .

Блой 25 синхронизации предназначен для формирования сигналов синхронизации блока 1 модификации адреса, ргэгистра 3 микрокоманд и контрольного оборудования.

Группа элементов И 11 предназначена Для передачи кода адреса строки блока 2 памяти микрокоманд при вьшол- нении микрокоманды безусловного перехода четвертого типа.

Группа элементов И 13 предназначена для передачи кода адреса строки блока 2 памяти микрокоманд при считывании микрокоманд второго типа.

Элемент И 14 предназначен для формирования сигнала ошибки при ее возникновении в случае считывания микрокоманды безусловного перехода третьего типа,,

Элемент И 20 предназначен для маскирования старшего разряда кода адреса строки, записанного в поле управления логикой признаков регистра 3 микрокома.нд на О, при считьгаании микрокоманды безусловного перехода четвертого типа.

Элементы И 13-18 предназначены ivm передачи соответствующих разрядов кода управления логикой признаков при выполнении микрокоманд, управляющих обработкой призршков.

Элемент И 22 предназначен для передачи сигнала ошибки при неправильном переходе к адресу очередной никрокоманды в случае реализации микрокоманды безусловного перехода четвертого типа.

Блок 9 элементов ИЛИ предназначен для передачи кодов адровсов строк блока 2 памяти микрокоманд с выхода буферного регистра 4 и с выхода элементов И 11 ..

Элемент ИЛИ 12 предназначен для определения ошибки при переходе к строке с ненулевым адресом при выполнении микрокоманды безусловного перехода третьего типа.

Элементы ИЛИ 23 и 24 предназначены для формирования сигналов управле1ния коммутаторами 5 и 6 соответственно .

Элемент ИЛИ 19 предназначен для формирования сигнала управления работой элементов И 15-18.

Элемент ИЛИ 26 предназначен для передачи сигнала сбоя (отказа) на информационный вход триггера 8 в случае его возникновения на выходах соответствующих элементов.

Схема 21 сравнения предназначена для сравнения признака зоны строк, в которой выполняется переход с признаком разрешения зоны, в которой разрешается такой переход.

Влек 25 синхронизации предназначен для выработки сигналов синхронизации устройства.

В устройстве осуществляется контроль правильности реализации микрокоманд безусловных переходов следующим образом.

В поле управления логикой признаков кажд.ой микрокоманды безусловного перехода записывается контрольный код, который в зависимости от типА реализуемой микрокоманды может быть кодом адреса строки или колонки. При этом, если из блока 2 памяти микрокоманд считьшается микрокоманда безусловного перехода первого типа, то в соответствующем поле регистра 3 считанной микрокоманды записывается код адреса колонки, в которой происходит переход. Условием правильного перехода считается переход по одной и той же колонке. При этом код адреса колонки не изменяется. После формирования кода адреса очередной микрокоманды происходит сравнение кода адреса колонки, записанного в соответствующем поле

to

15

20

5

0

5

0

5

0

5

регистра 3 микрокоманд, и адреса поступающего с выхода 30 блока 1 модификации адреса. Код с выхода соответ ствующего поля регистра 3 микроко- манд поступает на вход синхронизации коммутатора 5.

Дешифратор 7 на основании информации, записанной в поле управления переходами к следующему адресу микропрограммы, возбуждает один из первых четырех выходов, тем самым подает управляющий сигнал на вход коммутатора 5 и на управляющий вход коммутатора 6, Код адреса колонки блока 2 памяти микрокоманд поступает с выхода 30 блока 1 модификации адреса, тем самым на вход схемы 10 сравнения подаются два кода адреса колонки. В том случае, если микрокоманда безусловного перехода первого типа выполнена правильно, то на входы схемы 10. сравнения поступают два одинаковых кода, и сигнал ощибки на ее выходе отсутствует. Если переход выполнен неправильно, то единичный сигнал с выхода схемы 10 сравнения поступает на вход триггера 8 отказа, и работа устройства блокируется,

В случае реализации микрокоманды безусловного перехода второго типа, переход к следующему адресу производится в текущей строке. При этом адрес строки блока 2 памяти микрокоманд адреса микрокоманды безусловного перехода второго типа и адрес строки микрокоманды, в которой происходит переход, должны быть одинаковыми. Дешифратор 7 возбуждает один из соответствующих первых четырех выходов и подает единичный сигнал на управляющий вход коммутатора 5 и управляющий вход коммутатора 6, Код адреса строки блока 2 памяти микрокоманд микрокоманды безусловного перехода перед считыванием ее из этого блока запишется в регистр 4. Этот код поступает с выхода буферного регистра 4 через группу элементов И 13 и блок 9 на информационньй вход коммутора 6, А код адреса строки микрокоманды, в которой происходит переход, поступает с выхода 31 блока 1 модификации адреса на информационный вход коммутатора 5, Условием правильного перехода является равенство кодов, поступивших с выходов коммутатора 5 и 6, на соответствующие вхо

ды схемы 10 сравнения. В случае неправильного перехода единичный сигнал с выхода схемы 10 сравнения поступает на вход триггера 8, и работа устройства блокируется,

В случае считывания микрокоманды безусловного перехода третьего типа условием правильного перехода к адресу следующей микрокоманды является нулевое значение кода адреса строки блока 2 памяти микрокоманды той микрокоманды, в которой происходит переход.

Код адреса строки той микрокоманды, в.которой происходит переход, поступает на вход элемента ИЛИ 12. В том случае, если поступивший код имеет действительно нулевое значение, то на выходе этого элемента единичньй сигнал не сформирован, и сигнал неправильного перехода на выходе элемента И 14 также не сформирован.

В том случае, если переход происходит по адресу, расположенному не в нулевой строке, а в любой другой, то на выходе элемента И 14 появляется единичный сигнал, который поступает на вход триггера 8.

При считывании микрокоманды безусловного перехода четвертого типа правильность перехода определяется проверкой соответствия номера разрешенной зоны строк и номера строки в ней блока 2 памяти микрокоманд, записанного в поле управления логикой признаков регистра 3 микрокоманд, и номера зоны и номера строки в них, поступающих с выхода 31 блока 1 модификации адреса. Значение старшего разряда кода, записанного в поле уп- рап. логикой признаков разряда кода, записанного в поле управления 1к гикой признаков регистра 3 микрокоманд, равное О и соответствует зонам строк с номерами О и 2, а. со значением С номерами 1 и номеров зон строк блока 2 памяти мик рокоманд проверяется путем сравнения значений четвертого разряда кода адреса строки, поступающего с выхода 31 блока модификации адреса и старше г о разряда кода, записанного в соответствующем поле регистра 3 микрокоманд. Это сравнение производится в схеме 21 сравнения. Сравнение адресов ст рс к п разрешенных зонах производится (.педутишм образом. Значение

1 - зонам строк 3. Соответствие

0

5

0

5

0

5

5

0

5

старшего разряда кода, записанного ч поле управления логикой признаков регистра 3 микрокоманд, маскируется О на элементе И 20, Значение кода с выхода этого поля регистра 3 поступает на информационный вход коммутатора 5.

Дешр фратор 7 возбуждает соответствующий один из первых четырех своих выходов и подает единичный сигнал на управляющий вход коммутатора 5 и коммутатора 6, Значения трех младших разрядов кода адреса строки разрешенной зоны с выхода 31 блока 1 модификации адреса поступают через группу элементов И 11 на информацинньй вход блока 9, С выходов элементов И 13 группы на информационный вход блока 9 поступает нулевой пятиразрядный код, В результате на информационный вход коммутатора 6 поступает пятиразрядный код, в котором значения двух старших разрядов равны нулю. На ком- мутатаре 5 происходит формирование кода из четырехразрядного и маскирование старшего разряда О путем подачи сигнала запрета на его управляющий вход, в результате чего уже пятиразрядные коды с выходов коммутаторов 5 и 6 поступают на соответствующие вхо-ды схемы 10 сравнения. Если адреса строк в зонах совпадают, что свидетельствует о правильном переходе, то работа устройства продолжается, В противном случае единичньй сигнал с выхода схемы 10 сравнения поступает через элемент ИЛИ 26 на вход триггера 8, и работа устройства блокируется ,

Блок 1 модификации осуществляет адресацию микрокоманд, считы- ваемьсх на блоке 2 памяти микрокоманд и анализирует сигналы переноса и переполнения, поступающие из центрального процессорного элемента. Организация адре Ьации в блоке 1 осуществляется схемой 41 формирования следую- гцего адреса микропрограммы на основе кода команды, поступающего с входа 36, кода текущего адреса, поступающего с вькодов регистра 42 адреса, кода управления переходом к следующему адресу микропрограммы, и поступающего с выхода 32 регистра 3 микрокоманд. Для формирования кода адреса первой микрокоманды соответствующей ttiKponpограммы используется значение

старших четырех 3азрядов кода коман- ды, поступающего, на вход 36 блока 1 ,

Значения четырех младших разрядов кора команды, записанные в регистр 44, определяют код операции. По значениям четырех старших разрядов кода команды, поступившего с входа 36 блока 1 на схему 41 формирования следующего адреса, и значениям адресов строк и столбцов, поступающим с выходов регистра 42 на входы схемы 41, происходит определение адреса первой микрокоманды, реализуемой микропрограммы. Адрес первой микрокоманды микропрограммы с выхода схемы 41 поступает на вход регистра 42. В ло- следнем происходит выделение из кода адреса микрокоманды адреса строки и столбца блока 2 памяти микрокоманд, кото13ые поступают на входы соответствующих магистральных злементов 46 и 47 и на входы схемы 41.

После считывания микрокоманды из блока 2 памяти микрокоманд код управления переходом к следующему адресу микропрограммы с выхода 32 регистра 3 поступает на вход схемы 41, В схеме 41 происходит формирование адреса микрокоманды перехода по значениям, поступающим с входа 32 и с выходов регистра 42 адресов микрокоманд.

Выдача кода адреса микрокоманды с выходов регистра 42 адресов осуществляется через блоки 46 и 47 магистральных элементов. Код адреса микрокоманды по синхроимпульсам, поступающим на синхровход блока 1 модификации адреса, производит выдачу кода адреса микрокоманды с выходов магистральных элементо в 46 и 47. При этом разрешающим сигналом на выдачу кода адреса колонки является синхроимпульс, поступающий на управляющую группу входов Е блока 46 магистральных элементов. Условием выдачи кода адреса строки является наличие единичного сигнала, поступающего с входа 35 блока 1 модификации адреса на вход элемента И 50 с выхода блока приоритетного прерывания на разрешение вьща- чи адреса строки и наличие того же синхросигнала.

Устройство функционирует следующим образом.

В исходном состоянии все элементы памяти находятся в состоянии О. На вход 37 устройстЕ а nocTyriaeT сигнал .Пуск и на В1,1ходе 27 блока 25 син-

10

15

0

5

0

5

0

5

0

хронизации появляется сигнал 1, который поступает на вход синхрони- .зации блока 1 модификации адреса. По коду команды, поступившему с входа 36 устройства на первый информационный вход этого блока, в схеме 41 блока 1 происходит формирование адреса первой микрокоманды микропрограммы и запись сформированного адреса в регистр 42 адресов микрокоманд по переднему фронту того же синхроимпульса. .После записи адреса первой микрокоманды в регистр 42 адресов код адреса колонки поступает на вход блока 46 магистральных эле- ме(тов и. на четвертый информацион- ньш вход схемы 41. Код адреса строки поступает на вход блока 47 магнат- ральных элементов и на пятый информационный вход схемы 41. По сигналу 1 синхроимпульса, поступающему на первый вход элемента jH 50 и на вход Е блока 46, код адреса колонки поступает на выход 30 блока 1. При наличии сигнала 1 разрешения считывания кода адреса строки, поступающего с третьего входа блока 1 на второй вход элемента И 50, на его выходе сформируется сигнал 1, который поступает на вход Е блока 47, разрешая тем -самым вьщачу кода адреса строки на выход 31 блока 1. По коду адреса микрокоманды (коду адреса колонки и коду адреса строки) происходит считывание микрокоманды из блока 2 памяти микрокоманд.

Код адреса микрокоманды поступает на вход блока 2 памяти микрокоманд, код адреса колонки - на информационный вход коммутатора 6, а код адреса строки - на вход элемента ИЛИ 12 и на информационный вход буферного регистра 4, при этом три младших разряда этого кода поступают на входы элементов И 11 группы, а значение четвертого разряда - на вход схемы

21 сравнения.

По синхроимпульсу, поступающему

с выхода 28 блока 25 синхронизации на синхровход буферного регистра 4 и триггера 8, происходит запись кода адреса строки микрокоманды в буферный регистр 4 и подтверждение первого состояния триггера 8. Через время по синхроимпульсу, поступившему с выхода 29 блока 25 на синхровход регистра 3 микрокоманд, происходит запись считанной микрокоманды

из блока 2 в регистр 3. Переменная часть микрокоманды поступает с выхода 33 регистра 3 на выход устройства , Код управления переходами к еле- дующему адресу микропрограммы поступает с выхода 32 регистра 3 на вход дешифратора 7 и на вход задания логических условий блока 1. Код управления логикой признаков поступает с регистра 3 на входы соответствующих элементов И 15-18 и на информационный вход коммутатора 5, а значение старшего разряда этого кода поступает на вход элемента И 20.

В этом случае, если из блока 2 памяти макрокоманд считана микрокоманда, которая осуществляет управление логикой признаков, то на одном из старших выходовJ начиная с пятого дешифратора 7 появляется сигнал 1 который поступает через элемент ИЛИ 19 на входы элементов И 15-18 и открывает их. Информация с выхода регистра 3 микрокоманд поступает чере открытые элементы И 15-18 на вход блока 1 модификации адреса с целью обработки признаков, вьфабатываемых процессорным элементом и поступающи с входа 35 задания кода логических операций блока 1 модификации адреса на вход триггера 49 флагов.

В том случае, если микрокоманда не управляет логикой признаков и является микрокомандой безусловного перехода, то в устройстве его работа и контроль правильности переходов осуществляется следующим образом.

Если считана микрокоманда безусловного перехода первого типа, то на первом выходе дешифратора 7 появляется сиг нал 1, который на вход элемента ИЛИ 23 и с его- выхода - на управляющий вход коммутатора 5, а также на управляющий вход коммутатора 6, разрещая прохождение информации через соответствующие информационные входы, В этом случае значение старшего разряда кода, записанного в поле управления логикой признаков, не изменяется, так как эле- : мент И 20 продолжает находиться в oткpытo состоянии. Элемент И 22 находится в закрытом состоянии. Элемент И 14 группы элементов И 11 и 13 блокированы нулевыми сигналами, по ступающ 1ми с четвертого выхода дешифратора 7, При этом на информационные

5 О S

0 5 0

5

0

5

0

5

входы коммутатора 5 поступает код номера колонки, Р которой осуществляется переход, записанный в поле управления логикой признаков считанной микрокоманды. При этом значение старшего разряда этого кода поступает на вход элемента И 20, На его другой вход поступает сигнал О с четвертого вьпкода дешифратора 7 и открывает его, в результате чего значение старшего разряда не изменяется, Контрольный код поступает с выхода коммутатора 5 на информационный вход схемы 10 сравнения. По синхроимпульсу, поступившему с выхода 27 блока 25 синхронизации, происходит формирова-) ние кода адрес а очередной микрокоманды в блоке 1 модификации адреса. При этом значение кода адреса колонки на выходе 30 блока 1 при правильном переходе остается неизменным. Значение этого кода поступает на информационный вход коммутатора бис «го выхода поступает на инфор- , мационный вход схемы 10 сравнения, Если переход выполнен неправильно, то на выходе схемы 10 появляется сигнал 1, который поступает на в:кгод элемента ИЛИ 26 и далее На информационный вход триггера 8, По заднему фрсЛту синхроимпульса, поступившего с выхода 28 блока 25 синхронизации на соответствующий вход триггера В,, происходит запись 1 (сигнала

ошибки),. и на выходе 40 сбоя (отказа) триггера 8 появляется сигнал 1. Работа устройства блокируется, В том случае, если переход произведен верно, работа устройства продолжается. Если из блока 2 памяти микрокоманд считана микрокоманда безусловного перехода второго типа, то после ее записи в регистр 3 микросхемы на третьем выходе дешифратора 7 появляется сигнал 1, который поступает на управляющий вход коммутатора 5, на вход элемента ИЛИ 24 и с его вьгхода - на управляю1ций вход коммутатора 6, а также этот сигнал 1 поступает на травлянлций вход группы элементов И 13, разрешая передачу кода адреса строки из буферного регистра 4 на информационный вход блока 9 и далее на информационный вход коммутатора 6, По сигналу 1 с выхода 27 блока 25 сравнения в блоке 1 модификации адреса происходит формирование кода адреса очередной микрокоманды.

При этом код адреса строки микрокоманды перехода поступает на информационный вход открытого коммутатора 5 и р его выхода - для сравнения на ин- формационный вход схемы 10 сравнения В этом случае, если переход произведен неправильно, т.е. происходит обращение к строке с другим адресом, то на выходе схемы 10 сравнения появ ляется сигнал 1, который поступает на вход элемента ИЛИ 26 и далее на информационный вход триггера 8. По заднему фронту синхроимпульса, поступившего с входа 27 блока 25 синхррни зации на синхровход триггера 8, происходит его установка в состояние, и на выходе 40 устройства появляется сигнал сбоя (отказа).

Если формирование кода адреса очередной микрокоманды происходит правильно, то работа устройства продолжается .

Если в регистр 3 микрокоманд записана микрокоманда безусловного перехода третьего типа, то на третьем выходе дешифратора 7 устанавливается сигнал 1, который поступает на вход элемента И 14, который закрыт нулевым сигналом с выхода 28 блока 25 синхронизации. По синхроимпульсу, поступившему с выхода блока 25 синхронизации на вход синхронизации блока 1, на его информационных выходах устанавливается код адреса очередной микрокоманды. Если значение кода адреса, строки не равно О, это говорит о неправильном переходе к очередной микрокоманде, то на выходе эле- мента ИЛИ 12 появляется сигнал 1, который поступает на вход элемента И 14. По переднему фронту синхроимпульса, поступившего с выхода 28 блок 25 синхронизации на другой вход этого

элемента, сигнал 1 с его вьсхода поступает на вход элемента ИЛИ 26 и через него на информационный вход триггера 8. По заднему фронту этого импульса триггер 8 переходит в состоя- ние 1, и на выходе 40 устройства устанавливается сигнал 1 отказа (сбоя). В том случае, если переход- произведен правильно, то на выходе элемента ИПИ 12 vcтaнaвливaeтcя сиг-

который блокирует по-второнал О

му входу элемент И 14, и на выходе

последнего тоже устанавливается сигнал О . Работа -устройства в случае продолжается.

10 1520

0 35 0

5

Если из блока 2 считана микрокоманда безусловного перехода четвертого типа, i o работа устройства заключается в следующем. На четвертом вь1- ходе дешифратора 7 устанавливается сигнал 1, который поступает на входы элементов ИЛИ 24 и 23, на вход элемента И 20 и на управляющий вход группы элементов И 11 и открывает ее. В-результате этого на выходе элемента И 20 устанавливается сигнал О, с выходов элементов И 11 группы значения трех младших разрядов кода адреса строки поступают на информационный вход блока 9 и с его выхода - на информационный вход коммутатора 6. С выхода элемента ИЛИ 24 на управляющий вход коммутатора 6 поступает сигнал 1, который открывает его. Поскольку другой информационный вход этого коммутатора закрыт сигналом О с третьего выхода дешифратора 7, то на выходе коммутатора 6 находится пятиразрядный код, в котором два старших разряда равны О, и этот код поступает на информационный вход схемы 10 сравнения. С выходов регистра 3 микрокоманд четьфехразрядный код поступает на информационные входы, коммутатора 5. Поскольку другой информационный его вход закрыт сигналом О с третьего выхода дешифратора 7, то на вькоде коммутатора 5 присутствует пятиразрядный код, в котором два старших разряда равны О. Этот код поступает на информационный вход схемы Ш сравнения. При этом на ее выходе может находиться сигнал 1, поскольку формирование адреса микрокоманды перехода еще не произошло. Кроме того, значение старшего разряда кода адреса строки этой микрокоманды, записанной в регистре 3 микрокоманд, поступает на другой вход схемы 21 сравнения. Значение старшего разряда кода, поступающего (С выхода регистра 3, поступает на вход схемы 21 сравнения, выходной сигнал которой поступает на вход элемента И 22. Значение этого сигнала также может быть равно 1 или О, так как формирование адреса микрокоманды еще не произошло в блоке 1 . Если значение сигнала на выходе схемы 21 сравнения равно 1, то на выходе открытого по входу сигналом с четвертого выхода дешифратора 7 эле- менд-а И 22 устанавливается сигнал 1, который поступает на вход эле- мента ИЛИ 26. Если на выходе схемы 10 сравнения устанавливается сигнал 1, то он поступает на вход элемента ИЛИ 26. Сигнал 1 с выхода этого элемента поступает на информационный вход триггера 8. Однако триггер 8 в состояние 1 не переходит, поскольку синхросигнал на выходе блока 25 синхронизации отсутствует. По синхроимпульсу, поступившему с выхода 27 блока 25 синхронизации на вход блока 1 модификации адреса, на его информационных выходах устанавливается код адреса микрокоманды перехода. До появления синхроимпульса на выхо- де 28 блока 25 синхронизации в устройстве происходит контроль правильности перехода к новому адресу по описанному способу. При этом, если адрес строки соответствует адресу строки, записанному в трех младших разрядах поля управления логикой признаков, а номер разрешенной зоны не соответствует значению старшего разряда, этого кода, или, наоборот, номер разрешенной зоны соответствует а адрес строки в зоне не совпадает с требуемым его значением, то на выходах схемы 10 сравнения или элемента И 22, соответственно, устана)злива ется сигнал 1, который через эле- мент гКПИ 26 поступает на информационный вход триггера 8.

По заднему фронту синхроимпульса, поступившего с выхода 28 блока 25, триггер 8 переходит в состояние 1, и на выходе 40 устройства устанавливается сигнал 1 сбоя (отказа). В том слз. чае, если переход к очередной микрокоманде происходит правильно, работа устройства продолжается.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее блок памяти микрокоманд, блок синхронизации, буферный регистр, регистр микрокоманд, первый и второй коммутаторы, дешифратор, триггер, первьй, второЙ8 третий и четвертый элементы И, первый элемент ИЛИ и блок модификации адреса, причем выходы блока памяти

Q 0 5 Q

0

5

0

микрокоманд соединены с информационными входами регистра микрокоманд, первый выход блока синхронизации соединен с в-ходом синхронизации регистра микрокоманд, второй выход блока синхронизации соединен с входом синхронизации буферного регистра, группа выходов признака кода логических условий регистра микрокоманд соединена с группой информационных входов дешифратора, выход первого элемента ИПИ соединен с информационным входом триггера, вход пуска устройства соединен с входом пуска блока синхронизации, отличающееся тем, что, с целью повьппения достоверности контроля,, оно содержит первую и вторую схемы сравнения, второй, третий, четвертый и пятый элементы ИЛИ, первую, вторую и третью группы элементов И, блок элементов ИЛИ, пятый, шестой, седьмой, восьмой и девятый элементы И, причем второй выход бло-. ка синхронизации соединен с входом синхронизации триггера и первым входом перво.го элемента И, первая группа адресных входов блока памяти микрокоманд соединена с первой группой выходов поля адресов блока модифика- D,HH адреса и первой группой информационных входов первого коммутатора, вторая группа адресньк входов блока памяти микрокоманд соединена с второй группой выходов поля адресов бло- модификации адреса, с группой входов второго элемента ИЛИ, с информационными входами буферного регистра и первой группой информационных входов второго коммутатора, выходы признака модифицируемого адреса строки поля адресов блока модификации адреса соединены с первыми входами элементов И первой группы, выходы которых соединены с первой группой входов блока элементов ИЛИ, выходы которого соединены с второй группой информационных входов первого коммутатора, группа вьсходов которого соединена с первой группой входов схемы сравнения, выход Равно которой соединен с первьм входом первого элемента ИЛИ, группа выходов признака кода логических условий регистра микрокоманд соединена с группой входов кода логических условий блока модификации адреса, вход синхронизации которого соединен с третьим выходом блока синхронизации, первый выход дешифратора

соединен с вторым входом второго элемента И, второй выход дешифратора соединен с первым входом третьего элемента ИЖ, третий выход дешифратора соединен с первым управляющим входом второго коммутатора, первым входом четвертого элемента ИЛИ и с первыми входами элементов И второй группы, выходы которых соединены с второй группой входов блока элементов ИЛИ, четвертьш выход дешифратора соединен с вторым входом четвертого элемента ИЛИ, с вторым входом третьего элемента ИЛИ, с инверсным входом шестого элемента И, с вторыми входами элементов И первой группы и первым входом седьмого элемента И, группа вькодов дешифратора с.оединена с группой входов пятого элемента ИЛИ, выход кото- рого соединен с первыми входами второго , третьего, четвертого и пятого элементов И, выходы которых соединены с адресными входами блока модификации адреса, группа входов задания кода логической операции которого соединена с входом задания кода логической операции устройства, выход признака следующей микрокоманды регистра микрокоманд соединен с вторым входом пятого элемента И, с прямым входом шестого элемента И и первым входом второй схемы сравнения, выход Равно которой соединен с вторым входом седьмого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, выходы признака перехода к следующему адресу микрокоманды регистра микрокоманд соединены с вторыми входами второго, тр-етьего и четвертого элементов И, выход третьего элемента ИЛИ соединен с первым управляющим входом первого коммутатора и вторым управляющим входом- второго коммутатора, группа выходов которого соединена с второй группой входов первой схемы сравнения, вьрсод четвертого элемента ИЛИ соединен с вторым управляющим входом первого коммутатора, выход шестого элемента И соединен с третьим управляющим входом второго коммутатора, выходы признака немодифицируемой части адреса регистра микрокоманд соединены с второй группой информационных входов второго коммутатора, выход второго элемента ИЛИ соединен с третьим входом первого элемента И, выходы буферного регистра соединены с вторыми входами элементов И второй группы, второй вход второй схемы сравнения соединен с выходом первого элемента И первой группы, выход триггера- является выходом отказа устрой ства.

36

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1327103A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при контроле процессоров. Цель изобретения - повышение достоверности контроля. Устройство содержит блок модификации адреса, выполненный на микропроцессоре, два коммутатора, сумматор, триггер, группу элементов И, блок синхронизации, две схемы сравнения. Это позволяет повысить достоверность функционирования путем организации контроля правильности реализации пе- реходов при выполнении микрокоманд безусловных переходов за счет использования свободного поля управления логикой признаков в формате считываемых микрокоманд. 5 ил.

Фиг

L

.З

«э-.

i

Колонии

mm

Редактор Н.Рогулич

Ф(г.ё

Составитель А.Сиротская Техред Qi.ConKO

Заказ 2772/51

Тираж 671 оПодписное

ВНИИПИ Государственного комитета СССР

по депам изобр етений и .открытий 113035, Москва, Ж-35, Ра)Пцская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектушя, 4

Корректор Е.Сирохман

| Устройство микропрограммного управления | 1980 |

|

SU896621A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропроцессоры в цифровых системах, М.: Энергия, 1979, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

Авторы

Даты

1986-05-23—Публикация

1984-04-04—Подача