входом второго элемента И второй группы, выход (N-1)-ro элемента ИЛИ первой группы соединен со счетным входом перйого триггера контроля, инверсным входом второго элемента И и первым входом третьего элемента И выход (N-l)-ro элемента ИЛИ второй группы соединен со счетным входом второго триггера контроля, вторым входом третьего элемента И и инверсHbiNf входом четвертого элемента И, выход третьего элемента И соединен с вторым входом первого элемента И и инверсньм входом пятого элемента И выход которого является выходом готовности устройства и соединен с первыt i входом шестого элемента И второй вход которого является вхо-дом запуска устройства, выход шестого элемента И соединен с вторыми нулевыми входами

первого и второго триггеров контроля и входами синхронизации всех триггеров первого и второго регистров, выход первого элемента И соединен с вхдами синхронизации первого и второго триггеров контроля и вторыми прямыми входами всех элементов И второй группы, выход генератора импульсов соединен с первьми прямыми входами второго и четвертого элементов И и прямым входом пятого элемента И, прямые выходы первого и второго триггеров контроля соединены соответственно с вторыми прямыми входами второго и четвертого элементов И, выходы которых соединены с соответствующими входами элементов ИЛИ, выход которого является выходом контроля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Формирователь разновесных кодов | 1985 |

|

SU1297031A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО КОДА НА ЧЕТНОСТЬ, содержащее генератор импульсов, элемент ИЛИ, первый триггер контроля, первый элемент И, первый регистр и первую группу элементов И, причем информационные входы первого регистра образуют группу информационных входов устройства, прямые выходы триггеров первого регистра соединены с первыми прямыми входами соответствующих элементов И первой группы, выходы которых соединены с первыми нулевыми входами соответствующих триггеров первого регистра, выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен с вторыми прямыми входами всех элементов И первой группы, отличающеес я тем, что, с целью повышения быстродействия устройства, в него введены второй регистр, второй триггер контроля, вторая группа элементов И, две группы элементов ИЛИ, второй, третий, четвертый, пятый и шестой элементы И,, причем информационные входы второго регистра соединены с соответствующими входами группы информационных входов устройства, установочньш вход устройства соединен с первыми нулевыми входами первого и второго триггеров контроля, вторыми нулевыми входами триггеров первого регистра и первыми единичными входами триггеров второго регистра, инверсные выходы триггеров второго регистра соединены с первыми прямыми входами соответствующих элементов И второй группы, выходы которых соединены с вторыми единичными входами соответствующих триггеров второго регистра, прямой выход триггера каждого i-го разряда первого регистра (, где N - разрядность регистра) соединен с первым входом (i-l)-ro элемента ИЛИ первой группы, инверсный выход триггера каждого i-ro разряда второго регистра соединен с первым входом ({-1)-го элемента ИЛИ второй группы, выход каждого j-ro элемента ИЛИ первой группы

Изобретение относится к автоматике и вычислительной технике и может быть использовано для проверки на четность информации в системах передачи и обработки данных.

Известно устройство для контроля параллельного кода на четность ll, недостатком которого является низкое быстродействие.

Наиболее близким к изобретению является устройство для контроля параллельного кода на четность содержащее регистр, группу элементов И, элемент ИЛИ, элемент И, элемент И-НЕ и триггер, причем единичные входы триггеров регистра являются информационными входами устройст.ва, прямые выходы триггеров регистра соединены с первыми входами соответствующих элементов И группы, выходы которых соединены с нулевыми входами соответствующих триггеров р егистра и соответствующими входами элемента ИЛИ, выход которого соединен со счетным входом триггера, выходы которого являются выходами контроля устройства, первьй вход элемента И

является тактовым входом устройства выход элемента И соединен с вторыми входами всех элементов И группы инверсньд вькод триггера i-го разряда регистра (, где N - разрядность регистра) соединен с (i+2)-M входом (i+1)-ro элемента И группы и

5 i-M входом элемента И-НЕ, выход которого соединен с вторым входом элемента Ие инверсный выход триггера N-ro разряда регистра соединен с N-M входом элемента И-НЕ L21,

O Недостатком известного устройства является невысокое быстродействие.

Цель изобретения - повьшение быстродействия устройства.

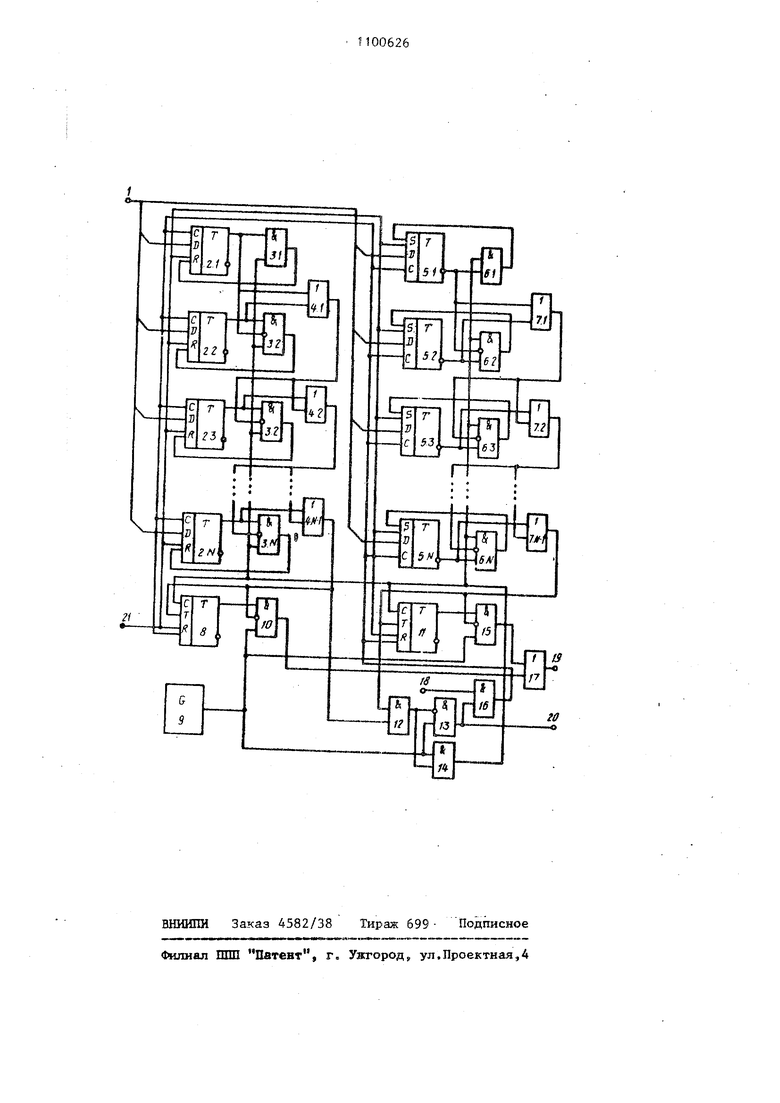

Поставленная цель достигается тем, что в устройство для контроля параллельного кода на четность, содержащее генератор импульсов, элемент ИШ, первьвч триггер контроля, первый элемент И,, первьш регистр и первую группу элементов И, причем информационные входы первого регистра образуют информационную группу входов устройства, прямые выходы триггеров первого регистра соединены с первыми прямыми входами соответствующих элементов И первой группы, вьЕкоды которьк соединены с первыми нулевыми входами соответствующих триггеров первого регистра, выход генератора шшульсов соединен с, пер3вьтм. входом первото элемента И, выход которого соедии -н с вторьми прямыми входами всех элементов И первой группы, введены второй регистр, второй триггер контроля, вторая груп па элементов И, две группы элементов ИЛИ, второй, третий, четвертый, пятьй и шестой элементы И, причем информационные входы второго регистра соединены с соответствующими входами информационной группы входов устройства, установочный вход устройства соединен с первьтми нулевыми входами первого и второго триггеров контроля, вторыми нулевыми входами всех триггеров первого-регистра и первыми единичными входами всех триггеров второго регистра, инверсные выходы триггеров второго регистра соединены с первыми прямыми входа ми соответствующих элементов И второй группы, выходы которых соединены с вторыми единичными входами соответ ствующих триггеров второго регистра, прямой выход триггера каждого t-ro разряда первого регистра (, где N - разрядность регистра) соединен с первым входом (i-l)-ro элемента ИЛИ первой группы, инверсный выход триггера каждого i-ro разряда второго регистра соединен с первым входом (l-l)-ro элемента ИЛИ второй группы, выход каждого j-ro элемента ИЛИ первой группы (1 Чн-2) соеди нен с вторым входом (j+1)-ro элемента ИЛИ первой группы и с инверсным, входом .(+2)-го элемента И первой группы, выход каждого j-ro элемента ИЛИ второй группы соединен с вторым входом (j+1)-ro элемента ИЛИ вто рой группы и с инверсным входом (j+2)-ro элемента И второй группы, второй вход первого элемента ИЛИ первой группы соединен с прямым выхо дом триггера первого разряда первог регистра и с инверсным входом второго элемента И nepBoii группы, второй вход первого элемента ИЛИ второй группы соединен с инверсным выходом триггера первого разряда второго ре гистра и с инверсным входом второго элемента И второй группы, выход (N-l)-ro элеме.нта ИЛИ первой группы соединен со счетным входом первого триггера контроля, инверсным входом второго элемента И и с первым входо третьего элемента И, выход (N-1)-ro элемента ИЛИ второй группы соединен со счетным входом второго триггера 264 контроля, вторым входом третьего элемента И и инверсным входом четвертого элемента И, выход Третьего элемента И соединен с вторьм входом первого элемента И п инверсным входом пятого элемента И, выход которого является выходом готовности устройства и соединен с первым входом шестого элемента И, второй вход которого является входом капуста устройства, выход шестого элемента И соединен с вторыми нулевыми входами первого и второго триггеров контроля и входами синхронизации всех триггеров первого и второго регистров, выход первого элемента И соединен с входами синхронизации первого и второго триггеров контроля и вторыми прямыми входами всех элементов второй группы, выход генератора импульсоь соединен с первыми прямыми входами второго и четвертого элементов И и прямым входом пятого элемента И, прямые выходы первого и второго триггеров контроля соединены соответственно с вторыми прямыми входами второго и четвертого элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом контроля устройства. На чертеже приведена функциональная схема устройства для контроля параллельного кода на четность. Схема содержит группу 1 информационных входов устройства,первый регистр 2, первую группу 3 элемёнтов И, первую группу 4 элементов ИЛИ, второй регистр 5, вторую группу 6 элементов И, вторую группу 7 элементов ИЛИ, первый триггер 8 контроля, генератор 9 импульсов, второй элемент И 10, второй триггер 1 контроля, третий элемент И 12, пятый элемент И 13, первьй элемент И 14, четвертый элемент И 15, шестой элемент И 16, элемент ИЛИ f7, вход 18 запуска устройства, выход 19 контроля устройства, выход 20 готовности уст ройства, установочный вход 21 устройства. Устройство для контроля параллельного кода на четность работает следующим образом, В исходном состоянии устройства триггеры регистров 2 и 5 и триггеры 8 и 11 контроля находятся в нулевом состоянии. Устройство приводится в исходное состояние сигналом, .поступающим на его установочный

вход 21. Тактовые импульсы с выхода генератора 9 импульсов через элемент И 13 поступают на выход 20 готовности устройства, сигнализируя о его готовности к работе.

На группу 1 информационных входов устройства поступает разрядный параллельньй код (N - четно), Каждый 1-й разряд кода подается одновременно на информационные входы триггеров t-x разрядов регистров 2 и 5. Начало работы устройства определяется моментом поступления управляющего сигнала на вход 18 запуска устройства, который свидетельствует о том, что на информационные входы регистров 2 и 5 подан код и можно начинать процесс контроля.

Управляющий сигнал, поступающий на вход 18 запуска устройства, открывает элемент И 16, и очередной тактовый импульс с выхода генератора 9 импульсов через элемент И 13 поступает на элемент И 16 и далее на входы синхронизации регистров 2 и 5 и нулевые входы триггеров контроля 8 и 11. В результате этого контролируемый код записывается в регистры 2 и 5 одновременно и подтверждается исходное состояние триггеров контроля 8 и 11. При э1ом на выходах (N-1)-x элементов ИЛИ первой 4 и второй 7 групп появляются единичные сигналы, которые поступаю на счетные входы триггеров контроля 8 и 1 1 , а также на входы элемента И 12. Единичный сигнал с выхода элемента И 12 поступает на инверсны вход элемента И 13 и вход элемента И 14. Вследствие этого очередной тактовый импульс с выхода генератора 9 импульсов проходит на выход элемента И 14 и поступает на. соответствующие входы элементов И первой 3 и второй 6 групп и входы синхронизации триггеров контроля 8 и 11. Под воздействием этого импульса триггеры 8 и 11 переключаютс в единичное состояние. Кроме того., в регистре 2 на нулевой вход самого мпадшего разряда, содержащего единицу, с выхода соответствующего элемента И первой группы 3 поступает единичный сигнал и устанавливает этот разряд в нулевое состояние. Это объясняется тем, что элементы И группы элементов И 3, номера которых меньше номера переключившегося

разряда регистра, закрыты нулевыми сигналами с выходов соответствующих им триггеров, а элементы И группы элементов И 3, номера которых больше 5 номера переключившегося разряда регистра, закрыты единичньми сигналами, поступивЕш-гми с выходов соответствующих элементов ИЛИ второй группы 4. Аналогично в регистре 5 на единич0 ный вход самого младшего разряда, содержащего ноль, поступает сигнал с выхода соответствующего элемента И второй группы 6, который переводит этот разряд из нулевого в единичное

S состояние. Таким образом, в результате поступления первого импульса с выхода элемента И 14 на входы первой 3 и второй 6 групп элементов И число единиц в коде, записанном в

0 регистре 2, и число нулей в коде,

записанном в регистре 5, уменьшается на единицу, а триггеры контроля 8 и 11 переключаются в единичное состояние . В результате поступления оче5 редкого тактового импульса с выхода эхгемента И 14 число единиц в коде, записанном в регистре 2, и число нулей в коде, записанном в регистре 5, вновь уменьшается на единицу,

0 а состояния триггеров контроля 8 и 11 изменяются на противоположные,

Работа устройства продолжается аналогичным образом до тех пор, пока в регистре 2 не окажется записанным нулевой код или в регистре 5 код.

состоящий только из единиц.

Предположим, что на вход устройства поступил код, в котором число единиц меньше, чем число нулей, и равно К. Тогда, через К тактов все триггеры регистра 2 устанавливаются в исходное (нулевое) состояние и на выходе (М-1)-го элемента ИЛИ первой группы 4 появляется нулевой сигнал. Этот сигнал поступает на вход элемента И 12;в результате чего нулевой сигнал с выхода этого элемента запрещает прохождение очередного тактового импульса на выход элемента И 14 и разрешает его прохождение через элемент И 13 на выход 20 у готовности устройства. Появлениеэтого сигнала сигнализирует об окончании цикла контроля и о появлении на выходе S устройства 19 результата контроля. Одновременно нулевой сигнал с выхода (N-1)ro элемента ИЛИ первой группы 4 поступает на инверсный вход

71

элемента И 10 и открывает элемент И 10 по входу. Тактовый импульс с выхода генератора 9 импульсов проходит на выход элемента И 10 и далее через элемент ИЛИ 17 на выход 19 контроля устройства, если триггер контроля находится в состоянии единицы. Это свидетельствует о нечетном числе единиц в контролируемом коде. В противном случае на выходе элемента И 10, а следовательно, и на выходе 19 устройства сигнал равен нулю, что свидетельствует о четном числе единиц в контролируемом коде.

Когда число нулей в коде меньше, чем число единиц, формирование сигнала на выходе 2, готовности устройства и передача на выход 19 контроля устройства состояния второго

268

триггера 11 контроля осуществляется по нулевому сигналу на в.ыходе (N-1)го элемента ИЛИ второй группы 7, После того как очередной код поступит на информационн ю группу 1 входов устройства, на установочный вход 18 поступает управляющий сигнал. Очередной тактовый импульс с выхода элемента И 16 поступает на входы регистров синхронизагни 2 и 5 и устанавливает триггеры контроля 8 и 11 в исходное состояние. После этого устройство переходит к циклу контроля очередного кода.

, Таким образом, в предложенном устройстве время контроля не превышает тактов, что повышает его быстродействие .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля параллельного кода на четность | 1979 |

|

SU883910A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1983-01-03—Подача