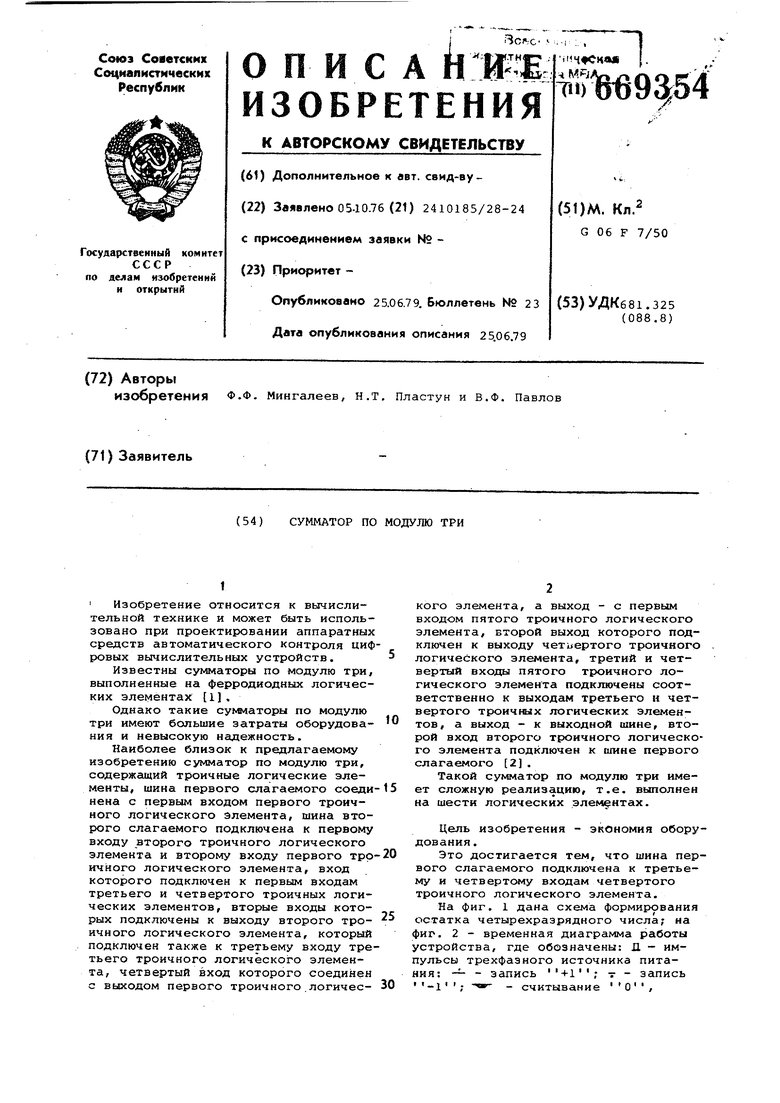

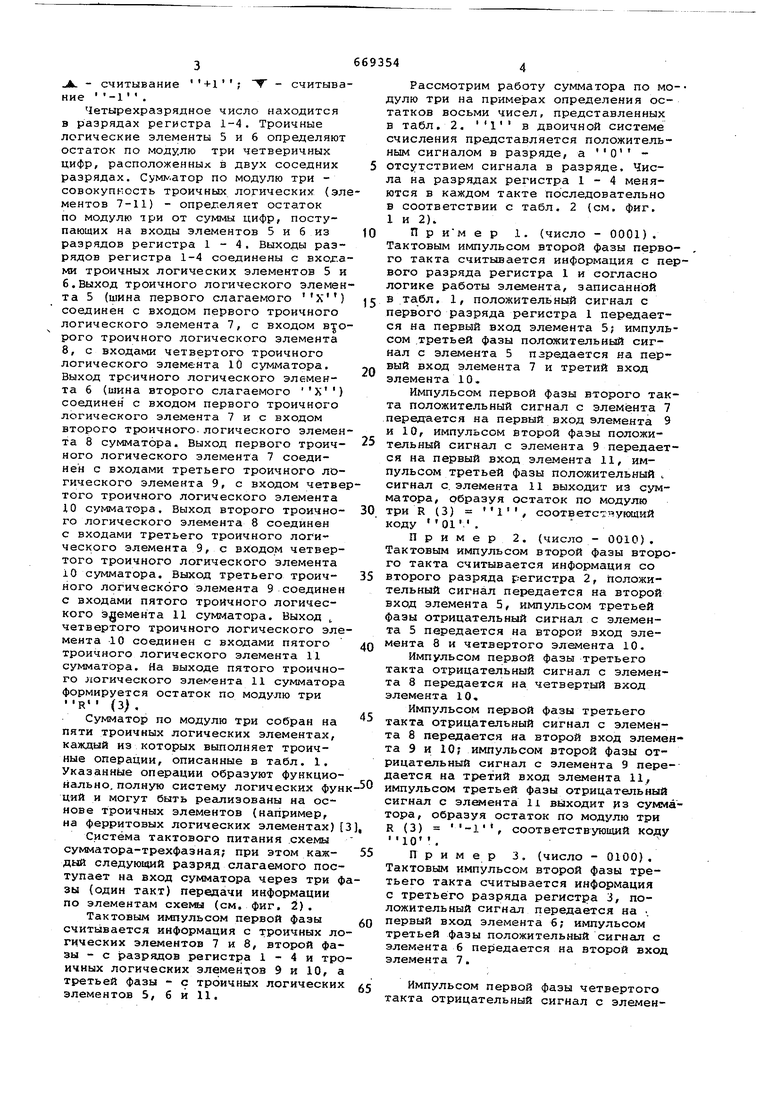

Изобретение относится к вычислительной технике и может быть использовано при проектировании аппаратных средств автоматического контроля циф ровых вычислительных устройств. Известны сумматоры по модулю три, выполненные на ферродиодных логических элементах 1. Однако такие сукматоры по МОДУ.ШО три имеют большие затраты оборудования и невысокую надежность. Наиболее близок к предлагаемому изобретению сумматор по модулю три, содержащий троичные логические элементы, шина первого слагаемого соеди нена с первым входом первого троичного логического элемента, шина второго слагаемого подключена к первому входу второго троичного логического элемента и второму входу первого трр ичного логического элемента, вход которого подключен к первым входам третьего и четвертого троичных логических элементов, вторые входы которых подключены к выходу второго троичного логического элемента, который подключен также к третьему входу тре тьего троичного логического элемента, четвертый вход которого соединен с выходом первого троичного.логического элемента, а выход - с первым входом пятого троичного логического элемента, второй выход которого подключен к выходу четвертого троичного логического элемента, третий и четвертый входы пятого троичного логического элемента подключены соответственно к выходам третьего и четвертого троичгелх логических элементов, а выход - к выходной шине, второй вход второго троичного логического элемента подключен к шине первого слагаемого 2, Такой сумматор по модулю три имеет сложную реализацию, т.е. выполнен на шести логических элементах. Цель изобретения - экономия оборудования . Это достигается тем, что шина первого слагаемого подключена к третьему и четвертому входам четвертого троичного логического элемента. На фиг. 1 дана схема формирования остатка четырехразрядного числа; на фиг. 2 - временная диаграмма работы устройства, где обозначены: Д - импульсы трехфазного источника питания: - - запись - - запись - - считывание О .А. - считывание Т - считыва ние - . Четырехразрядное число находится в разрядах регистра 1-4. Троичные логические элементы 5 и 6 определяют остаток по модулю три четверичных цифр, расположенных в двух соседних разрядах. Сум.атор по модулю три совокупность троичных логических (эл ментов 7-11) - определяет остаток по модулю 1ри от суммы цифр, поступающих на входы элементов 5 и б из разрядов регистра 1 - 4. Выходы разрядов регистра 1-4 соединены с входа ми троичных логических элементов 5 и 6.Выход троичного логического элемен та 5 (шина первого слагаемого X) соединен с входом первого троичного логического элемента 7, с входом Bjo рого троичного логического элемента 8, с входами четвертого троичного логического элемента 10 сумматора. Выход троичного логического элемента 6 (шина второго слагаемого X) соединен с входом первого троичного логического элемента 7 и с входом второго троичного, логического элемен та 8 сумматора. Выход первого троичного логического элемента 7 соединен с входами третьего троичного логического элемента 9, с входом четве того троичного логического элемента 10 сумматора. Выход второго троичного логического элемента 8 соединен с входами третьего троичного логического элемента 9, с входом четвертого троичного логического элемента 10 сумматора. Выход третьего троичного логического элемента 9 соедине с входами пятого троичного логического элемента 11 сумматора. Выход четвертого троичного логического эле мента 10 соединен с входами пятого троичного логического элемента 11 сумматора. На выходе пятого троично го логического элемента 11 сумматор формируется остаток по модулю три R (3), Сумматор по модулю три собран на пяти троичных логических элементах, каждый из которых выполняет троичные операции, описанные в табл. 1. Указанные операции образуют функцио нально, полную систему логических фу ций и могут быть регшизованы на основе троичных элементов (например, на ферритовых логических элементах) Система тактового питания .схемы сумматора-трехфазная; при этом каждьЕй следующий разряд слагаемого пос тупает на вход сумматора через три зы (один такт) передачи информации по элементам (см. фиг. 2). Тактовым иишульсом первой фазы считывается информация с троичных л гических элементов 7 и 8, второй фа зы - с разрядов регистра 1 - 4 и тр ичных логических элементгов 9 и 10, третьей фазы - с троичных логически элементов 5, б и 11. Рассмотрим работу сумматора по мо- улю три на примерах определения остатков восьми чисел, представленных в табл. 2. в двоичной системе счисления представляется положительным сигналом в разряде, а О отсутствием сигнала в разряде. Числа на разрядах регистра 1-4 меняются в каждом такте последовательно в соответствии с табл. 2 (см, фиг. 1 и 2). П р им е р 1. (число - 0001) . Тактовым импульсом второй фазы первого такта считывается информация с первого разряда регистра 1 и согласно логике работы элемента, записанной в табл. 1, положительньгй сигнал с первого разряда регистра 1 передается на первый вход элемента 5; импульсом .третьей фазы положительный сигнал с элемента 5 паредается на первый вход элемента 7 и третий вход элемента 10. Импульсом первой фазы второго такта положительный сигнал с элемента 7 передается на первый вход элемента 9 и 10, импульсом второй фазы положительный сигнал с элемента 9 передается на первый вход элемента 11, импульсом третьей фазы положительный . сигнал с. элемента 11 выходит из сумматора, образуя остаток по модулю три R (3) , соответс-:-дующий Пример 2. (число - 0010) . Тактовым импульсом второй фазы второго такта считывается информация со второго разряда регистра 2, положительный сигнал передается на второй вход элемента 5, импульсом третьей фазы отрицательный сигнал с элемента 5 передается на второй вход элемента 8 и четвертого элемента 10. Импульсом первой фазы третьего такта отрицательный сигнал с элемента 8 передается на четвертый вход элемента 10, Импульсом первой фазы третьего такта отрицательный сигнал с элемента 8 передается на второй вход элемента 9 и 10; импульсом второй фазы отрицательный сигнал с элемента 9 передается на третий вход элемента 11, импульсом третьей фазы отрицательный сигнал с элемента 11 выходит из сумматора , образуя остаток по модулю три R (3) , соответствующий коду 10, Пример 3. (число - 0100). Тактовым импульсом второй фазы третьего такта считывается информация с третьего разряда регистра 3, положительный сигнал передается на . первый вход элемента 6; импульсом третьей фазы положительный сигнал с элемента б передается на второй вход элемента 7. Импульсом первой фазы четвертого такта отрицательный сигнал с элемен та 7 передается на четвертый вход элемента 9, импульсом второй фазы положительными сигнал с элемента 9 передается на первый вход элемента импульсом третьей фазы положительный сигнал с элемента 11 выходит из сумматора, образуя остаток по модул три R (3) +1 соответствующий 546 Аналогично, в соответствии со схемой (см. фиг. J) и временной диаграммой (см. фиг. 2), происходит выполнение последуклдих примеров, приведенных в табл. 2. Предлагаемый сумматор обеспечивает экономию одного троичного логического элемента по сравнению с известным техническим решением. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1977 |

|

SU734684A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Троичный сумматор | 1978 |

|

SU953637A1 |

| Двоичный сумматор | 1976 |

|

SU638960A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Троичный реверсивный п-разрядный счетчик импульсов | 1977 |

|

SU733109A1 |

Формула изобретения Сумматор по модулю три, содержащий троичные логические элементы,ши- 65

Таблица2 на первого слагаемого соединена с первым входом первого троичного логического элемента,шина второго слагаемо Д 4- : ГО подключена к первому входу второг Чфоичного логического элемента и вто рому входу первого троичного логичес когр. элемента выход которого подключён к первьол входам третьего и четвертого троичных логических элементов, вторые входы которых подключены к выходу второго троичного логического элемента, который подключен также к третьему входу третьего троичного логического элемента, четвертый вход которого соединен с выходом, первого троичного логического элемента, а выход - с первым входом пятого троичного логического элемента, второй выход которого подключен к выходу четвертого троичного логического элемента, третий и четвертый входы пятого троичного логическог 2 элемента подключены соответственно 4 к выходам третьего и четвертого тро-ичных логических элементов, а выход к выходной шине, второй вход второго троичного логического элемента подключен к шине первого слагаемого, отличающийс я тем, что, C. целью экономии оборудования, шина первого слагаемого подключена к третьему и четвертому входам четвертого троичного логического элемента. Источники информации, принятые .во внимание при экспертиэе 1.Авторское свидетельство СССР 441564, кл.С 06 F 7/50, 1974. 2.Кузнецов В.Ф. и др. Ферритовые логические элементы. М,,Энергия, 197%, с. 54-66, рис. 3-15. . 3.Авторское свидетельство СССР № 208347, кл. 42 га 14, 29.12.67.

Авторы

Даты

1979-06-25—Публикация

1976-10-05—Подача