СП

оо

о

00

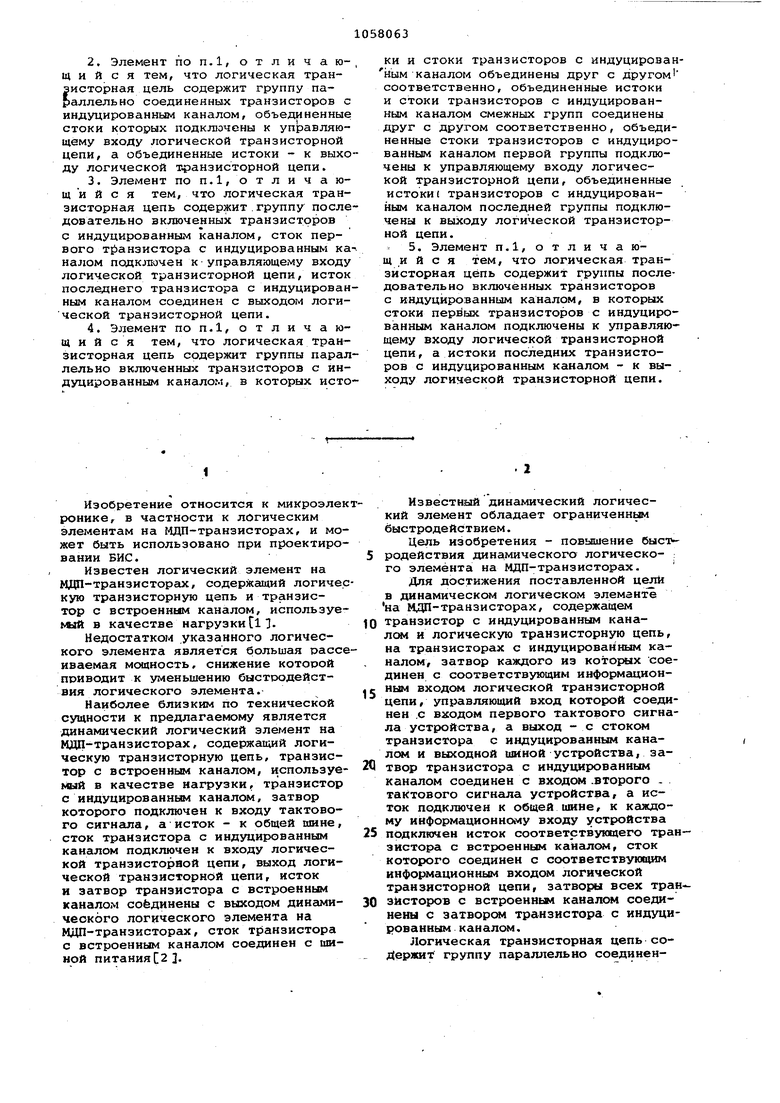

2.Элемент по п.1, отличаю1Д и и с я тем, что логическая транзисторная цель содержит группу параллельно соединенных транзисторов с индуцированнью«1 каналом, объединенные стоки которых подкл}очены к управляющему входу логической транзисторной цепи, а объединенные истоки - к выходу логической Еранзисторной цепи.

3.Элемент поп.1,отличающ и и с я тем, что логическая транзисторная цепь содержит.группу последовательно включенных транзисторов

с индуцированным каналом, сток первого т Ьанзистора с индуцированным ка налом подключен к управляющему входу логической Транзисторной цепи, исток последнего транзистора с индуцированным каналом соединен с выходом логической транзисторной цепи.

4.Элемент по п.1, отличающий с я тем, что логическая транзисторная цепь содержит группы параллельно включенных транзисторов с индуцированным каналом, в которых истоки и стоки транзисторов с индуцированным каналом объединены друг с другом соответственно, объединенные истоки и стоки транзисторов с индуцированным каналом смежных групп соединены друг с другом соответственно, объединенные стоки транзисторов с индуцированным каналом первой группы подключены к управляющему входу логической транзисторной цепи, объединенные истокиI транзисторов с индуцированным каналом последней группы подключены к выходу логической транзисторной цепи.

5. Элемент п.1, о тли ч а ющ и и с я тем, что логическая транзисторная цепь содержит группы последовательно включенных транзисторов с индуцированным каналом, в которых стоки nepriiax транзисторов с индуцированным каналом подключены к управляющему входу логической транзисторной цепи, а истоки последних транзисторов с индуцированным каналом - к выходу логической транзисторной цепи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| Устройство сопряжения биполярных и МДП логических устройств | 1974 |

|

SU591091A1 |

| Формирователь импульса по включению напряжения питания | 1985 |

|

SU1272496A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

| Логическое устройство | 1986 |

|

SU1378047A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

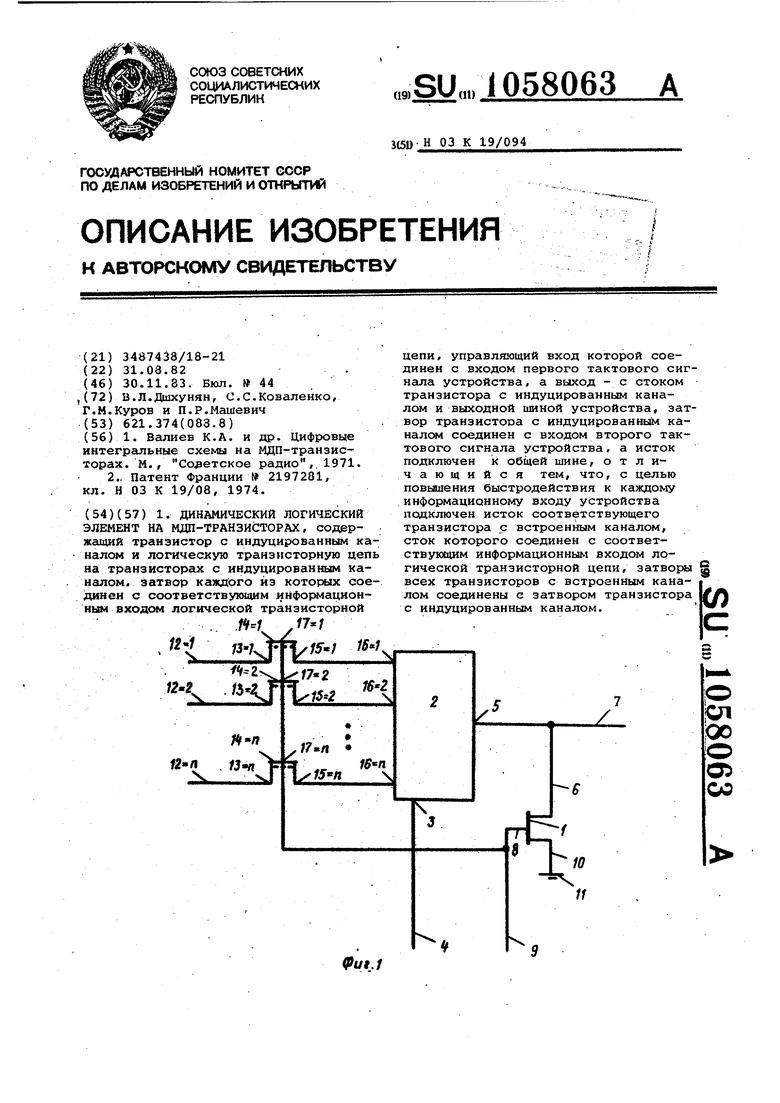

1. ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА Мда-ТРАНЗИСТОРАХ, содержащий транзистор с индуцированным ка налом и логическую транзисторную цепь на транзисторах с индуцированным каналом, затвор каждого из которых соединен с соответствующим информационным входом логической транзисторной цепи, управляющий вход которой соединен с входом первого тактового сигНсша устройства, а выход - с стоком транзистора с индуцированным каналом и выходной имной устройства, затвор транзистора с индуцированным каналсяу соединен с входом второго тактового сигнала устройства, а исток подключен к общей шине, отличающийся тем, что, с целью повышения быстродействия к каждому информационному входу устройства подключен исток соответствующего транзистора с встроенным каналом, сток которого соединен с соответствуквдим информахшонным входом логической транзисторной цепи, затворы всех транзисторов с встроенным кана(Л лом соединены с затвором транзистора с индуцированным каналом.

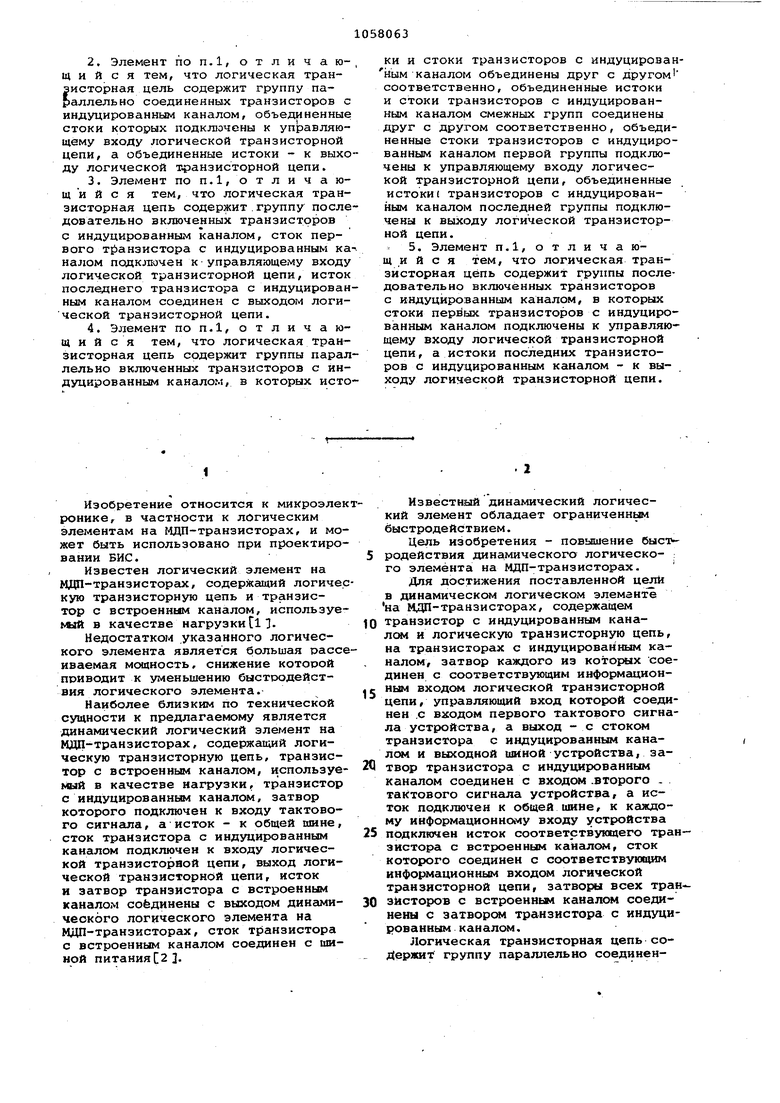

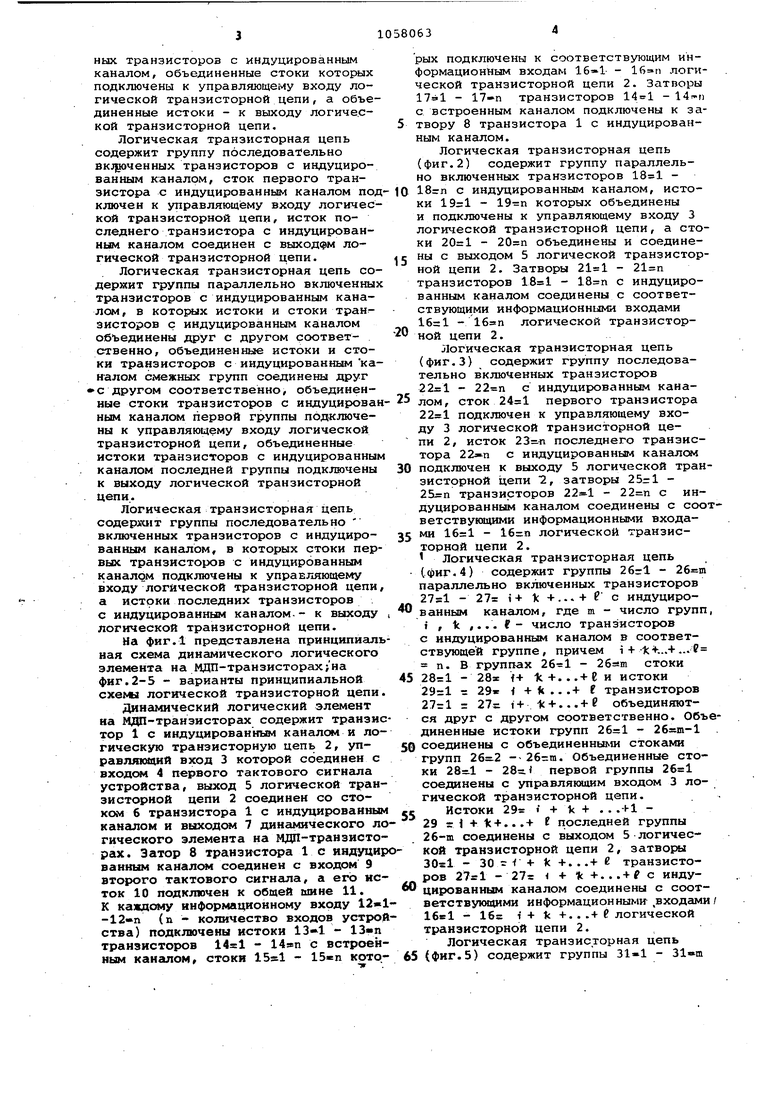

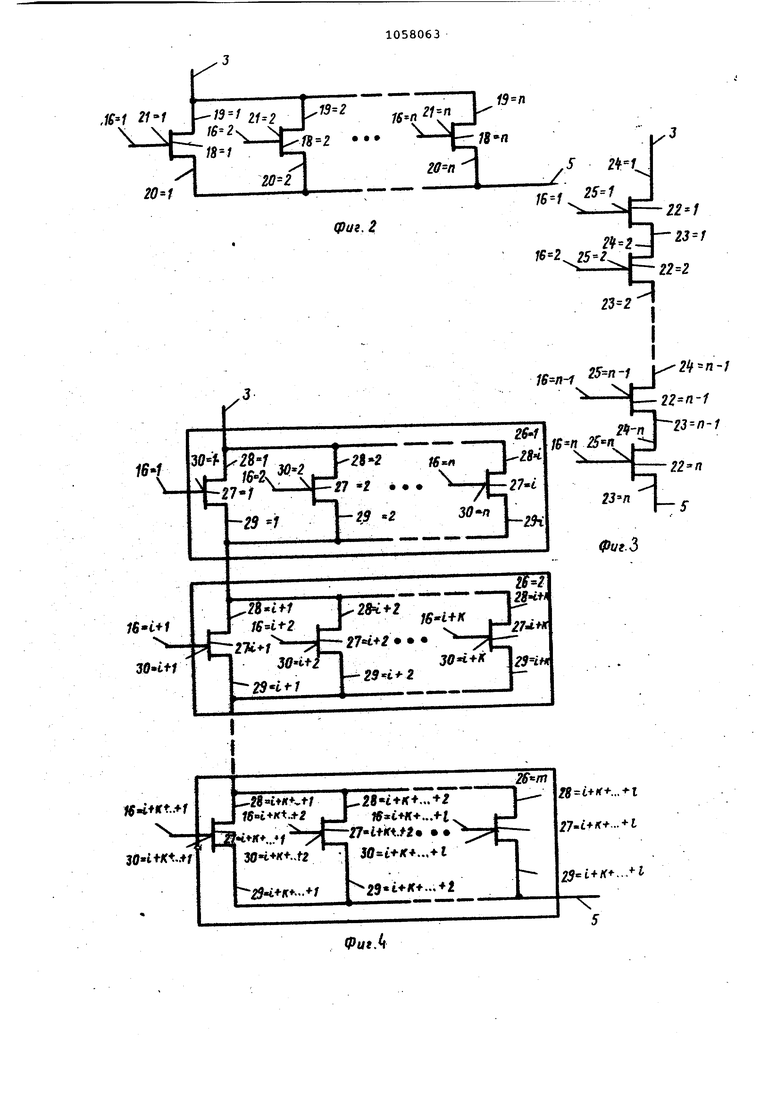

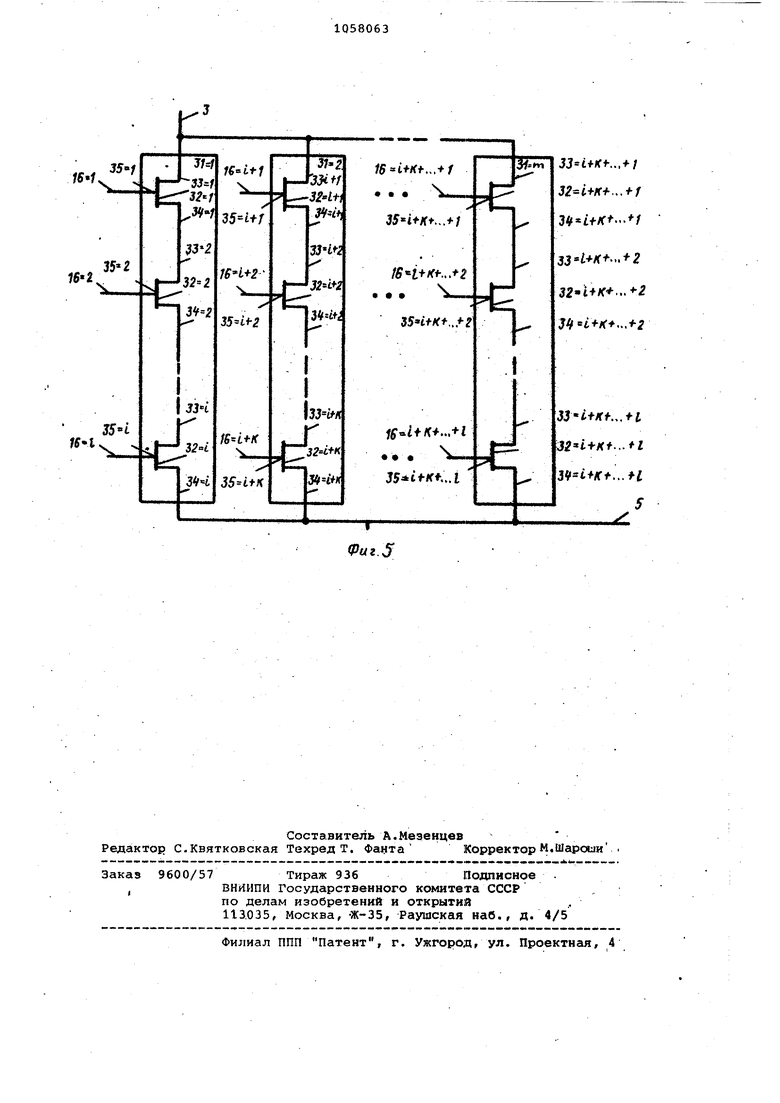

Изобретение относится к микроэле ронике, в частности к логическим элементам на ВДП-транзисторах, и мо жет быть использовано при проектиро вании БИС. Известен логический элемент на МДП-транзисторс1Х, содержащий логиче кую транзисторную цепь и транзистор с встроенным каналом, используе мый в качестве нагрузкиtl1. Недостатком указанного логического элемента является большая расс иваемая мощность, снижение которой ПРИВОДИТ к уменьшению быстродействия логического элемента.Наиболее близким по технической сущности к предлагаемому является динамический логический элемент на МДП-транзисторах, содержащий логическую транзисторную цепь, транзистор с встроенным каналом, используе мый в качестве нагрузки, транзистор с индуцированным каналом, затвор которого подключен к входу тактового сигнёша, а исток - к общей шине, сток транзистора с индуцированным каналом подключен к входу логической транзисторвой цепи, выход логической транзисторной цепи, исток и затвор транзистора с встроенным каналом соединены с выходом динамичеокого логического элемента на МДП-транзисторах, сток транзистора с встроенным каналом соединен с шиной питанияС23. Известн ый динамический логический элемент обладает ограниченньвл быстродействием. Цель изобретения - повышение быст родействия динамического логическо- : го элемента на МДП-транзисторах. Для достижения поставленной цели в динамическом логическом элементе на МДП-транзисторах, содержащем транзистор с индуцированным каналс 1 и логическую транзисторную цепь, на транзисторах с индуцированным каналом, затвор каждого из KOTOI«X соединен с соответствующим информационным входом логической транзисторной цепи, управляющий вход которой соединен .с входом первого тактового сигнала устройства, а выход - с стоком транзистора с индуцированным каналом и выходной имной устройства, затвор транзистора с индуцированным каналом соединен с входом .второго . тактового сигнала устройства, а исток подключен к общей шине, к каждому информационному входу устройства подключен исток соответствующего транзистора с встроенным канале, сток которого соединен с соответствующим информационным входснл логической транзисторной цепи, затворы всех транзисторов с встроенным каналом соединены с затворсж транзистора с индуцированным каналом. Логическая транзисторная цепь содержит группу параллельно соединенных транзисторов с индуцированным каналом, объединенные стоки которых подключены к управляющему входу логической транзисторной цепи, а объединенные истоки - к выходу логиче.ской транзисторной цепи, Логическая транзисторная цепь содержит группу последовательно вкJgoчeнныx транзисторов с индуцированным каналом, сток первого транзистора с индуцированным каналом под ключей к управляющему входу логической транзисторной цепи, исток последнего транзистора с индуцированным каналом соединен с выходам логической транзисторной цепи. Логическая транзисторная цепь содержит группы параллельно включенных транзисторов с иидуцированным каналом, в которых истоки и стоки тран зисторов с иидуцированным каналом объединены друг с другом соответственно, объединенные истоки и стоки транзисторов с иидуцированным каналом смежных групп соединены друг с другом соответственно, объединенные стоки транзисторов с индуцирован ным каналснл первой группы подключены к управляющему входу логической транзисторной цепи, объединенные истоки транзисторов с индуцированным каналом последней группы подключены к выходу логической транзисторной цепи. Логическая транзисторная цепь содержит группы последовательно включенных транзисторов с индуцированным каналом, в которых стоки первых транзисторов с индуцированным каналом подключены к управляющему входу логической транзисторной цепи а истоки последних транзисторов с индуцированным каналом.- к выходу логической транзисторной цепи. На фиг.1 прюдставлена принципиаль ная схема динамического логического элемента на МДП-транзисторах}на фиг.2-5 - варианты принципиальной схемл логической транзисторной цепи Динамический логический элемент на МДП-транзисторгис содержит транзи тор 1 с индуднрованньм каналом и ло гическую транзисторную цепь 2, управляющнй вход 3 которой соединен с входам. 4 первого тактового сигнаша устройства, выход 5 логической тран зисторной цеПи 2 соединен со стоком 6 транзистора 1 с индуцированным кансшом и выходом 7 динамического л гического элемента на МДП-транзисто рах. Затор 8 транзистора 1с индуци ванным каналом соединен с входом 9 второго тактового сигнгша, а его не ток 10 подключен к общей шине 11. К каждому информационному входу 12i-12 п (п - количество входов устро ства) подключены истоки 13«1 - 13«п транзисторов - 14вп с встроен ным каналом стоки 15sl - кото рых подключены к соответствующим информационным входам 16-1 - логической транзисторной цепи 2. Затворы - 17-п транзисторов 14 1 - 14-п с встроенным каналом подключены к затвору 8 транзистора 1 с индуцированным каналом. Логическая транзисторная цепь (фиг.2) содержит группу параллельно включенных транзисторов с индуцированным каналом, истоки - которых объединены и подключены к управляющему входу 3 логической транзисторной цепи, а стоки - объединены и соединены с выходом 5 логической транзисторной цепи 2. Затворы - транзисторюв - с индуцированным каналом соединены с соответствующими информационными входами - логической транзисторной цепи 2. Логическая транзисторная цепь (фиг.З) содержит группу последовательно включенных транзисторов - с индуцированным каналом, сток первого транзистора подключен к управляющему входу 3 логической транзисторной цепи 2, исток последнего транзистора с индуцированным каналом подключен к выходу 5 логической транзисторной цепи 2, затворы транзисторов - с индуцированным каналом соединены с соответствукнцими информационными входами - логической транзисторной цепи 2. Логическая транзисторная цепь (.фиг«4) содержит группы 26г1 - параллельно включенных транзисторов 27sl - 27 i+ k +...+ f с индуцированным каналом, где m - число групп, t , 1с ,... f- число транзисторов с индуцированным каналом в соответствующей группе, причем i .-b... Р п. В группах - стоки - 28х i+ It+...+ и истоки 29 i +fc...+ е транзисторов 27 1+ IC + ...+ P объединяются друг с другом соответственно. Объединенные истоки групп - соединены с объединенными стоками групп 26.2 -- . Объединенные стоки 28. - 28. первой группы соединены с управляющим входом 3 логической транзисторной цепи. Истоки 29 1 + k -ь . . .-И 29 г 1 1с + ...+ f последней группы 26-т соединены с выходом 5 логической транзисторной цепи 2, затворы - 30 - + k +...+ и транзисторов - 27 i + +...+ с индуцированным каналом соединены с соответствуинцими информационными .входами/ - 16 i + k +...+ Р логической транзисторной цепи 2. Логическая транзисторная цепь (фиг.5) содержит группы 31-1 - 31«т

последовательно включенных транзисторов 32jrl - 32 1 + ...+ с индуиированньвл каналом, В каждой группе хгтоки 33sl - 33 1 + 1с +,.,+1 первых транзисторов - 32- f + ...+ 1 с индуцированным каналом подключены к управляющему входу 3 логической транзисторной цепи 2, а истоки - 34 1+ k +...+ Р последних транзисторов 32 i - 32г I + . +... + с индуцированным каналом - к выходу 5 логической транзисторной цепи 2. Затворы - 35- 1 + ...+ б транзисторов 32г1 - 32 1 4-,-k+...+ с индуцированным каналом соединены с соот ветствующими информационными бходами - 16 1+ 1с +...+ Й логической транзисторной цепи 2.

Динамический логический элемент на МДП-транзисторах работает следующим образом.

При подаче на вход 4 первого тактового сигнала устройства логического нуля, а на вход 9 второго тактового сигнала логической единицы транзистор 1 с индуцированным канале открыт и йа выходе 7 устройства устанавливается уровень логического нуля. Затем на информационные входы поступ ает заданная комбинация логических переменных X , X,j, , ... ,Х ; на входе 4 первого тактового сигнала формируется логическая единица, а на входе 9 второго тактового сигнала - логический нуль. .

Если комбинация входных переме нных содержит хотя бы одну логическую единицу для параллельного включения транзисторов происходит переключение сигнала на выходе динамического логического элемента из состояния лот гического нуля в состояние логической единицы, если все входные переменные Х, Х2,... ,Х,.,равны нулю, то состояние выхода динамического логического элемента не изменяется.

Поскольку функционирование рассматриваемого динамического логического элемента на МДП-транзисторах идентично при реализации логической транзисторной цепи согласно принципиальным схемам (фиг.2-5J, то рассмотрим работу устройства при peaлизации логической транзисторной це.пи 2 согласно принципиальной схеме, приведенной на фиг.2.

Пусть комбинация входных переменных включает хотя бы одну логическую 1, предположим Х . Тогда на затворе 21. транзистора с индуцированным каналом формируется напряжение , С1эответствук1дее логической 1 и этот транзистор открыт. При подаче логического нуля на вход 9 второго тактового сигнала закрываются транзистор 1 с индуцированным каналом и транзистор с встроенным каналом. Сигнал логической 1 с входа 4 первого тактового сигнала через открытый транзистор 18г1 с индуцированны1«1 каналом передается на выход 5 логической транзисторной цепи. Причем, так как транзистор 12г1 с встроенным каналом закрыт, то на затворе транзистора, с индуцированным каналом формируется напряжение, соответствующее удвоенному напряжению логической единицы. Поскольку при этом переключение сигнала на выходе устройства из состояния логического нуля в состояние логической единицы происходит под действием большего тока через транзисто)р с индуцированнам каналом, то быстродействие динамического логического элемента повышается.

Если все переменные во входной комбинации равны нулю, хо на затворе транзистора 18sl с индуцированньлл каналом формируется напряжение логического О и транзистор 18аг1 закрыт. При подаче логического О на вход 9 второго тактового сигнала закрывается транзистор с индуцированным каналом. При подаче логической 1 на вход 4 первого тактового сигнала (поскольку транзистор .18-1 с индуцированным каналом закрытJ на стоке 2Or1 при выходе 5 логической транзисторной цепи.и выходе 7 динамического логического элемента на МДП-транзисторах сохраняется уровень логического нуля. Подключение открытого транзистора 14 с встроенным каналом к затвору транзистора с индуцированным каналом снижает уровень помехи на выходе 5 логической транзисторйой цепи .

,1S1 21-1

.

..,

vj

.

.,.t

.../

32-l+K+.. + f .

(Puz.S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Валиев К.А | |||

| и др | |||

| Цифровые интегральные схемы на МДП-транэисторах | |||

| М., Советское радио, | |||

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| РЕГУЛИРОВАНИЕ ПОДАЧИ ГАЗА ИЛИ ЛЕКАРСТВЕННОГО ПРЕПАРАТА ПАЦИЕНТУ | 1997 |

|

RU2197281C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-11-30—Публикация

1982-08-31—Подача