Изобретение относится к вычислительной технике и электронике и может быть использовано при постро ении микромощных интегральных запо минающих устройств (ЗУ). Известны параллельные дешифраторы на одноканальных МДП-транзисторах статического и динамического типа, содержащее логические ячейки, состоя щие из параллельной группы транзисто ров и нагрузочного транзистора, на отношение размеров которых наложено ограничение tl и 2. Однако эти дешифраторы потребляют значительную мсяцность в статическом режиме и непригодны для ЗУ на дополн ющих МДП-транзисторах. Наиболее близким к предлагаемому является параллельный дешифратор на дополняющих МДП-транзисторах, содерж ИИй логические ячейки, состоящие из группы параллельно соединенных транзисторов и коммутирующего транзистора р-типа,управляющего транзистора и транзистора обратной связи п-типа , ja логического элемента ИЛИ-НЕ,инвертор, сщновходовой логический элемент ИЛИ (схему повторения) с задержкой причем стоки управляющего транзистора, транзистора обратной связи, груп пы параллельно соединенных транзисторов под-кл1.ачены к первому входу логического элемента ИЛИ-НЕ, вторые входыкоторых и затворы управляющих транзисторов объединены во всех ячейках и подключены ко входу логического элемента И.ПИ с задержкой, вход которого подключен к выходу инвертора и к объединенньм во всех ячейках затворам коммутирующих транзисторов, истоки которых подключены к шине питания, а стоки - к истокам параллельно соединенной группы транзисторов, истоки транзисторов обратной связи и управ.ляющих транзисторов подключены к шине нулевого потенциала, затворы транзисторов обратной связи подключены к выходам логических элементов HJM-HE, затворы транзисторов параллельной группы, объединенные по дешифраторной схеме, подключены к прямым или инверсным адресным шинам дешифратора,вход инвертора - к стробирующей шине дешифратора 3. Недостатком известного дешифратора является низкая надежность его работы, что связано с возможностью выборки в нем ложных адресов, пониженное быстродействие и сложная структура топологического чертежа, что

бусловлвно наличием последовательюго соединения KOhiMyTHpyromero транiHCTOpa и группы параллельно соеди1енных траизксторов. Кроме того, в динамическом режиме при отсутствии разрешающего строб-сигнала, дешифрато ютребляет значительную мощность, :вязанную с перезарядом больших емсостей адресных шин.

Цель предлагаемого изобретения снижение потребляемой мощности, повыпение быстродействия и надежности ра5оты дешифратора и его упрощение.

Поставленная цель достигается тем, JTO параллельный дешифратор на до10ЛНЯЮЩЙХ МДП-транзисторах, содержадий логические ячейки, состоящие из группы параллельно соединенных транзисторов р- типа ,. управляющего транэистора п-типа, транзистора обратной связи П-типа и логического элемента ИЛИ-НЕ, логический элемент ИЛИ с зацержкой и первый инвертор, причем стоки всех транзисторов логической ячейки подключены к первому входу логического элемента ИЛИ-НЕ, истоки обоих транзисторов п-тйпа в логических ячейках - к шине нулевого потенциала, а затвор транзистора обратной связи п-типа - к выходу логического элемента ИЛИ-НЕ, вторые входы логических элементов ИЛИ-НЕ объединены во всех логических ячейках и подключены к выходу логического элемента ИЛИ с задержкой, шину питания, адресные и стробирующие шины, дополнительно co держит в.торой инвертор с задержкой и адресные логические элементы И-НЕ, причем затворы управляющих транзисторов, п-типа всех логических ячеек объединены и подключены к выходу первого инвертора и к первому входу логического элемента ИЛИ с задержкой, истоки паргшлельно соединенных транзисторов группы р-типа подключены к шине питания, затворы, объединенные соответственно и подключены к выходам адресных логических элементов И-НЕ, .первые входы которых подключены соответственно к прямым или инверсным адресным шинам дешифратора, вторые входы объединены и подключены к выходу второго инвертора с задержкой и ко входу первого инвертора, вход второго инвертора с задержкой и второй вход логического элемента ИЛИ с задержкой подключены к стробирующей шине дешифратора.

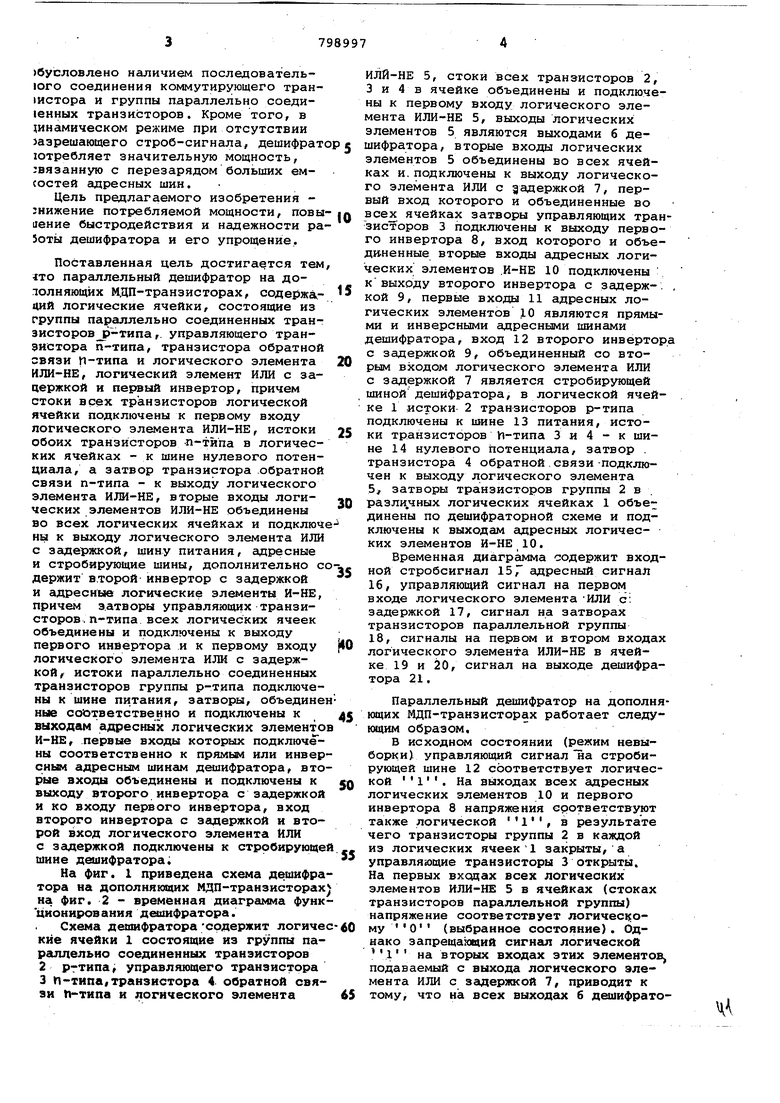

На фиг. 1 приведена схема дешифратора на дополняющих МДП-транзисторах) на фиг. 2 - временная диаграмма функционирования дешифратора.

Схема дешифратора -содержит логичес кие ячейки 1 состоящие из группы параллельно соединенных транзисторов

2рттипа, управляющего транзистора

3П-типа,транзистора 4 обратной связи П-типа и логического элемента

ИЛЙ-НЕ 5, стоки всех транзисторов 2, 3 и 4 в ячейке объединены и подключены к первому входу логического элемента ИЛИ-НЕ 5, выходы логических элементов 5 являются выходами б дешифратора, вторые входы логических элементов 5 объединены во всех ячейках и.подключены к выходу логического элемента ИЛИ с дадержкой 7, первый вход которого и объединенные во всезс ячейках затворы управляющих транзисторов 3 подключены к выходу первого инвертора 8, вход которого и объединенные вторые входы адресных логических элементов .И-НЕ 10 подключены : к выходу второго инвертора с задерж-. кой 9, первые входы 11 адресных логических элементов 10 являются прямыми и инверсными адресными шинами дешифратора, вход 12 второго инвертор с задержкой 9, объединенный со вторым входом логического элемента ИЛИ с задержкой 7 является стробирующей шиной дешифратора, в логической ячейке 1 истоки 2 транзисторов р-типа подключены к шине 13 питания, истоки транзисторов И-типа 3 и 4 - к шине 14 нулевого потенцисша, затвор . транзистора 4 обратной связи-подключен к выходу логического элемента 5, затворы транзисторов группы 2 в . разли.чных логических ячейках 1 объединены по дешифраторной схеме и подключены к выходам адресных логических элементов И-НЕ 10.

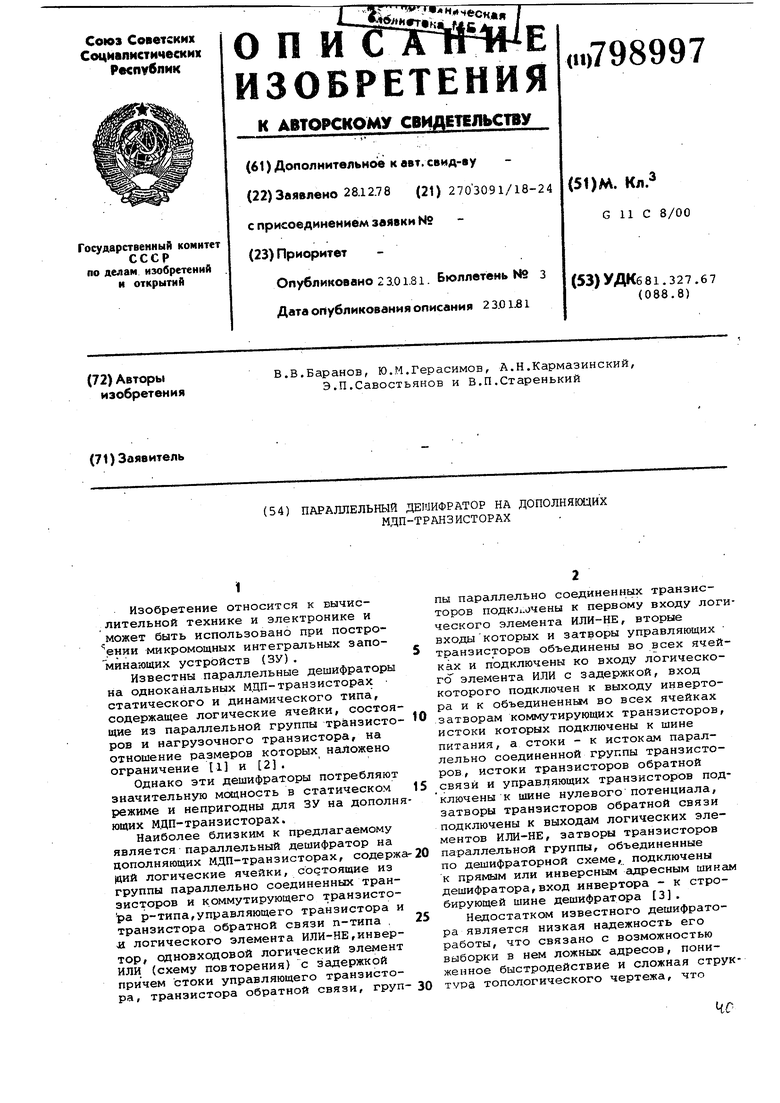

Временная диаграмма содержит входной стробсигнал 157 адресный сигнал 16, управляющий сигнал на первом входе логического элемента -ИЛИ с: задержкой 17, сигнал на затворах транзисторов параллельной группы 18, сигналы на первом и втором входах логического элемента ИЛИ-НЕ в ячейке 19 и 20, сигнал на выходе дешифратора 21.

Параллельный дешифратор на дополняющих МДП-транзисторах работает следующим образом.

В исходном состоянии (режим невыборки) управляющий сигнал на стробирующей шине 12 соответствует логической . На выходах всех адресных логических элементов 10 и первого инвертора 8 напряжения соответствуют также логической , в результате чего транзисторы группы 2 в каждой из логических ячеек1 закрыты,а управляющие транзисторы 3 открыты. На первых входах всех логических элементов ИЛИ-НЕ 5 в ячейках (стоках транзисторов параллельной группы) напряжение соответствует логичес1{ому О (выбранное состояние). Однако запрещаххций сигнал логической 1 на вторых входах этих элементов подаваемый с выхода логического элемента ИЛИ с задержкой 7, приводит к тому, что на всех выходб1х 6 дешифратоpa напряжения соответствуют режиму невыборки - логическому О. Транзисторы 4 обратной связи во всех яче ках дешифратора закрыты. В режиме выборки на стробируюадую шину 12 подается сигнал, соответству щий логическому О. Управляющие транзисторы во всех ячейках закрываются. На вторых входах адресных ло гических элементов И-НЕ 10 потенциал изменяется на логическую Ч и половина шин дешифратора, связанных 1/с затворами транзисторов параллельно гpyппы, изменяет свой потенциал с логической V1 на логический О В результате чего во всех ячейках дешифратора 5, кроме одной вь1бракной откЕялвается хотя бы одйй из транзисторов параллельной группы и потенциал на первом входе элементов ИЛИНЕ 5 этих ячеек устанавливается равиазл логической (невыбранное сое тояние). В ОДНОЙ выбранной ячейке транзисторы группы 2,управляюпи1й тр зистор 3,транзистор 4 обратной связи закрыты и напряжение логического . .О на первом входе элемента ИЛИНЕ 5 сохраняется. После появления разрешающего сигнала, соответствующе логическому , на выходе элемента ИЛИ с задержкой 7 (вторых входах элементов 5) на выходе б выбранной ячейки устанавливается потенциал логической , а транзистсчр 4 обрат ной связи откраавается, поддерживая . выбранное состояние ячейки. Для предотвращения появления ложных адресов необходимо, чтобы в невыбранных ячей ках напряжение, соответствующее логической Ч, на первс 1 входе элем нтов 5 установилось раньше, чем появится разрешающий сигнал логического О на вторых входах этих элёме тов. Это условие обеспечивается выбо ром требуемой задержки логического элемента ИЛИ с задержкой 7. После подачи на стробирующую шину 12 сигнала, соответствующего логичес кой (режим невыборки), в каяодо из невыбранных ячеек транзисторы параллельной группы закрывается, а управляющий транзистор 3 открывается. В результате чего на всех первых , входах элементов ИЛИ-НЕ 5 устанавливается напряжение,соответствующее вы бранному состоянию - логический О Для предотвращения появления ложных адресов необходимо, чтобы запрещающий сигнал логической Ч пришел на вторые входы элементов 5 раньше чем разрешающий сигнал логического О иа .их первые входы. Это условие обеспечивается, во-первых, подключением второго входа элемента ИЛИ с задержкой 7 к стробирующей шине 12 и, во-вторых, вцбором-требуемой , задержки второго инвертора с задержкой 9.Правильный выбор задержки элемента ИЛИ 7 и инвертора 9 предотвращает появление ложных адресов и гарантирует высокую надежность работы дешифратора. На практике логический элемент ИЛИ с задержкой реализуется последовательным соединением элемента ИЛИ-НЕ и инвертора, инвертор с задержкой 9 - в виде последовательного соединения нечетного числа обычных инверторов (не больше трех). Снижение динамической потребляемой мощности в дешифраторе по сравнению с известным обусловлено следующим . Во-первых, в режиме невыборки при изменении адреснь1х сигналов в дешифраторе перезаряжаются только входные емкости адресных элементов И-НЕ 10, KOTOF«e значительно меньше, чем емкости шин дешифратора, связанные с затворами транзисторов группы 2. Во-вторых, в режиме выборки в дешифраторе добиваются того, чтобы управляющие сигналы на затворы транзисторов группы 2 и управлякицих транзисторов 3 приходили практически одновременно, устранив тем самым состав ляющую динамической мощности, связанную с протеканием сквозного тока через эти транзисторы. В предлагаемой схеме дешифратора в логических ячейках отсутствуют последовательно соединенные однотипные транзисторы р-типа. В результате чего при заданной площади ячейки время ее переключения в состояние логической единицы уменьшается приблизительно в 3 раза, что приводит к повышению быстродействия схемы в целом на 15-30%. Логические ячейки предлагаемого дешифратора имеют более простую структуру топологического чертежа, а дешифратор в целом при числе выходов более 32 содержит меньше, транзисторов, чем известный. Формула изобретения Параллельный дешифратор на дополняющих МДП-транзисторах, содержащий логические ячейки, состоящие из группы параллельно соединенных транзисторов р-типа, управляющего -транзистора п-типа, транзистора обратной связи -типа и логического элемента ИЛИНЕ, логический элемент ИЛИ с задержкой и первый инвертор, причем стоки транзисторов логической ячейки подклюены к первому входу логического элеента ИЛИ-НЕ, истоки обоих транзистоов п-типа в логических ячейках - к ине нулевого потенцигша, а затвор ранзистора обратной связи п-типа - к выходу логического элемента ИЛИ-НЕ торые входы логических элементов ИЛИЕ подключены к выходу логического лемента ИЛИ с задержкой, шину питаия, адресные и стробирующие шины, тличающийся, тем, что, с елыр снижения потребляемой мощност.

повышения быстродействия и надежности работы дешифратора, он содержит второй инвертор с задержкой и адресные логические элементы И-НЕ, причем, .затворы управляющих транзисторов птипа логических ячеек подключены к выходу первого инвертора и к первому входу логического элемента ИЛИ с задержкой,истоки параллельно соединенных транзисторов группы р-типа подключены к шине питания,затворы ПОД ключены соответственно к выходам адресных логических элементов И-НЕ, первые входы которых подключены соответственно к прямым и инверсным адресным шинам дешифратора,вторые

входы подключены к выходу второго инвертора с задержкой и ко входу первого инвертора,вход второго инвертора с задержкой и второй вход логического элемента ИЛИ с задержкой подключены к стробирующей шине дешифратора.

Источники информации, принятые во внимание при экспертизе

1.Патент США 4048629, кл. 340-173, опубли :. 1977.

2.Патент США 3679911, кл. 307-251, опублик. 1972.

3.Onoyama А. at аС., CMOS 4К Static RAM, Toshiba iReview, 110,

Tut..- ang.,

1977, p. 24, fig. 4 fпрототип).

,J J J г TJ

flE

П5

}

+n

UflE

i..J

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор на КМДП-транзисторах | 1983 |

|

SU1180974A1 |

| Дешифратор на КМДП-транзисторах | 1982 |

|

SU1113853A1 |

| Параллельный дешифратор | 1981 |

|

SU1014030A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Дешифратор | 1982 |

|

SU1081790A1 |

I I r t I t I I I I I I t I I

и III I

10

-I 1

tt

I T

1У

Фи.1

V

Г9

HI llL

-I-P, III

I |i I 11

Авторы

Даты

1981-01-23—Публикация

1978-12-28—Подача