pa и со стоком опорного транзистора, затвор которого соединен с затвором третьего нагрузочного транзистора и подключен к информационному входу

усилителя, при зтом опорный и разрядньй транзисторы вьшолнены на транзисторах с индуцированным каналом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Элемент памяти | 1984 |

|

SU1163356A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ содержащий узел смещения напряжения, состоящий из транзистора блокировки мощности с нулевым порогом, сток которого соединен с шиной питания, затвор - с шиной управления, исток со стоком первого нагрузочного транзистора, исток которого соединен со стоком опорного транзистора, исток опорного транзистора подключен к шине нулевого потенциала, второго и третьего нагрузочных транзисторов, стоки которых соединены с шиной питания, истоки - со стоками зарядного и разрядного транзисторов соответственно, истоки которых объединены и подключены к информационному входу усилителя, а затворы соединены с истоком первого нагрузочного транзистора, узел усиления, состоящий из трех нагрузочных транзисторов затворы и истоки первого и второго нагрузочных транзисторов объединены и подключены соответственно к стокам первого и второго ключевых транзисторов, истоки которых объединены, затвор первого ключевого транзистора подключен к стоку разрядного, дтранзистора и истоку третьего нетрузочного транзистора узла смещения, затвор второго ключевого транзистора соединен с истоком третьего нагрузочного транзистора и со стоком разрядного транзистора, исток которого подключен к шине нулевого потенциала, отличающийся тем, что, с целью повыщения быстродействия и уменьшения потребляемой мощности усилителя, в узел усиления введены четыре транзистора блокировки мощности с нулевым порогом, четвертый нагрузочный транзистор и третий ключевой транзистор, при зтом стоки транзисторов блокировки мощности соединены с шиной питания, затворы - с шиной управления, истоки первого, второго и третьего транзисторов блокировки мощности соединены соответственно со стоками первого, ВТОРОГО и третьего нагрузочных Tpaji;;зисторов, исток четвертого транзистора блокировки мощности соединен со стоком четвертого нагрузочного .транзистора, затвор которого соедиСО нен с истоком третьего нагрузочного j; ;о X ел транзистора, а исток - со стоком третьего ключевого транзистора, затвор которого соединен со стоком второго ключевого транзистора, ис;ток - с шиной нулевого потенциала, затвор третьего нагрузочного транзистора соединен со стоком разрядного транзистора, затвор которого соединен со стоком первого ключево- . го транзистора, истоки первого и второго ключевых транзистород соединены с шнной нулевого потенциала, затвор первого нагрузочного транзистора узла смещения соединен с затвором второго нагрузочного транзисто

Изобретение относится к электрон ной и вычислительной технике и пред назначено для использования, в частности, в интегральных полупостоянных ЗУ. Известен усилитель считывания, содержащий узел смещения напряжения состоящий из пяти транзисторов с нулевым порогом, причем первый и второй транзисторы соединены последовательно между шиной питания и шиной нулевого потенциала, их затворы объединены и подключены к шине питания, сток второго транзистора соединен с затворами третьего и пятого транзисторов, истоки которых объединены и подключены к инфор мационному входу усилителя, сток третьего транзистора соединен с шиной питания, сток пятого транзистора соединен с истоком четвертого транзистора, сток и затвор которого подключен к шине питания, узел усиления, представляющий собой дифференциальный усилитель, состоящий из первого и второго нагрузочных транзисторов, стоки которых соединены с шиной питанияj затворы и истоки объединены и соединены со стоками первого и второго ключевых транзисторов соответственно истоки которых объединены и подключены к стоку разрядного транзистора исток которого соединен с шиной нулевого потенциала, а затвор - с шиной управления, затвор первого клю чевого транзистора соединен со стоком пятого транзистора с нулевым порОгом узла смещения напряжения, затвор второго ключевого транзистора соединен с источником опорного на пряжения ГЛ . Однако данный усилитель характеризуется недостаточно высокой чувствительностью, равной 100 мВт, отсутствием обратной связи в цепи узла смещения напряжения, приводящим к увеличению времени заряда и разряда емкостной нагрузки информационного входа усилителя, что не позволяет получить высокое быстродействие в ЗУ большой инффрмационной емкости. Схемотехническое решение отключения мощности в узле усиления, реализованное включением разрядного транзистора между истоками первого и второго ключевых транзисторов и шиной нулевого потенциала, требует значительного увеличения крутизны этих транзисторов, что приводит к увеличению площади данных узлов на кристалле. Кроме того, ранная схема усиления требует дополнительных цепей формирования опорного напряжения, что увеличивает площадь функционального узла на кристалле. Наиболее близким по технической сущности к предлагаемому является усилитель считывания, содержащий узел смещения напряжения, состоящий из транзистора блокировки мощности с нулевым порогом, сток которого соединен с шиной питания, затвор с шиной управления, исток - со стоком первого нагрузочного транзисто- ра, исток которого соединен со стоком опорного транзистора со встроенньм каналом, исток опорного транзистора подключен к шине нулевого потенциала, с (Которой соединены также затворы первого нагрузочного и опорного транзисторов, второго и третьего нагрузочных транзисторов, стоки которых соединены с шиной питания, истоки,- со стоками первого зарядного и разрядного транзисторов соответственно, истоки которых объединены и подключены к информационному входу усилителя, а затворы объединены с затворами третьего нагрузочного и второго зарядного транзисторов

3

и подключены к истоку первого нагрузочного транзистора, сток второго зарядного транзистора подключен к шине питания, исток - к информационному .входу усилителя, затвор второго нагрузочного транзистора соединен с шиной нулевого потенциала, узел усиления, представляющий собой дифференциальный каскад, содержащий три нагрузочных транзистора, стоки которых соединены с шиной питания, затворы и истоки первого и второго нагрузочных транзисторов объединены и подключены соответственно, к стокам первого и второго ключевых транзисторов, истоки которых объединены и подключены к стоку разрядного транзистора со встроенным каналом, исток и затвор кот зрого соединены с шиной нулевого потенциала, затвор первого ключевого транзистора подключен к истоку третьего нагрузочного транзистора узла смещения, затвор второго ключевого транзистора соединен с истоком третьего нагрузочного транзистора и, со стоком третьего ключевого транзистора, затвор и исток которого объединены с затвором третьего нагрузочного транзистора и подключены к шине нулевого потенциала 2.

Данному усилителю характерны недостатки усилителя LlJ . Кроме того в схеме усилителя отсутствует возможность блокировки мощности, что при многоразрядной организации ЗУ приводит к значительному увеличению суммарной потребляемой мощности.

Цель изобретения - повышение быстродействия при использовании в ЗУ большой информационной емкости и уменьшение потребляемой мощности.

Доставленная цель достигается тем, что в усилитель считывания, содержащий узел смещения напряжения, состоящий из транзистора блокировки мощности с нулевым порогом, сток которого соединен с шиной питания, затвор - с шиной управления, исток со стоком первого нагрузочного транзистора, исток которого соединен со стоком опорного транзистора, исток опорного транзистора подключен к шине нулевого потенциала, второго и третьего нагрузочных транзисторов, стоки которых соединены с шиной пи49654

тания, истоки - со стоками зарядного и разрядного транзисторов соответственно, истоки которых объединены и подключены к информационному входу усилителя, а затворы соединены с истоком первого нагрузочного транзистора j узел усиления, состоящий из трех нагрузочных транзисторов, затворы и истоки первого и второго нагрузочных транзисторов объединены и подключены соответственно к стокам первого и второго ключевых транзисторов, истоки которых объединены, затвор первого ключевого транзистора подключен к стоку разрядного транзистора и истоку треть.его нагрузочного транзистора смещения, затвор второго ключевого транзистора соединен с истоком третьего нагрузочного транзистора и со стоком разрядного транзистора, исток которого подключен к шине нулевого потенциала, дополнительно в узел усиления введены четыре транзистора блокировки мощности с нулевым

порогом, четвертый нагрузочный транзистор и третий ключевой транзистор, при этом стоки транзисторов блокировки мощности соединены с шиной питания, затворы - с шиной управления, истоки первого, второго и третьего транзисторов блокировки мощности соединены соответственно со стоками первого, второго и третьего нагрузочных транзисторов, исток четвертого транзистора блокировки мощности соединен, со стоком четвертого нагрузочного транзистора, затвор которого соединен с истоком третьего нагру-

0 зочного транзистора, а исток - со стоком третьего ключевого транзистора, затвор которого соединен со стоком второго ключевого транзистора, исток - с шиной нулевого потенциала,

5 затвор третьего нагрузочного транзистора соединен со стоком разрядного транзистора, затвор которого соетдинен со стоком первого ключевого транзистора, истоки первого и второго ключевых транзисторов соединены с шиной нулевого потенциала, затвор первого нагрузочного транзистора узла смещения соединен с затвором второго .:iipy3очного транзистора и

5 со сточен опорного транзистора,

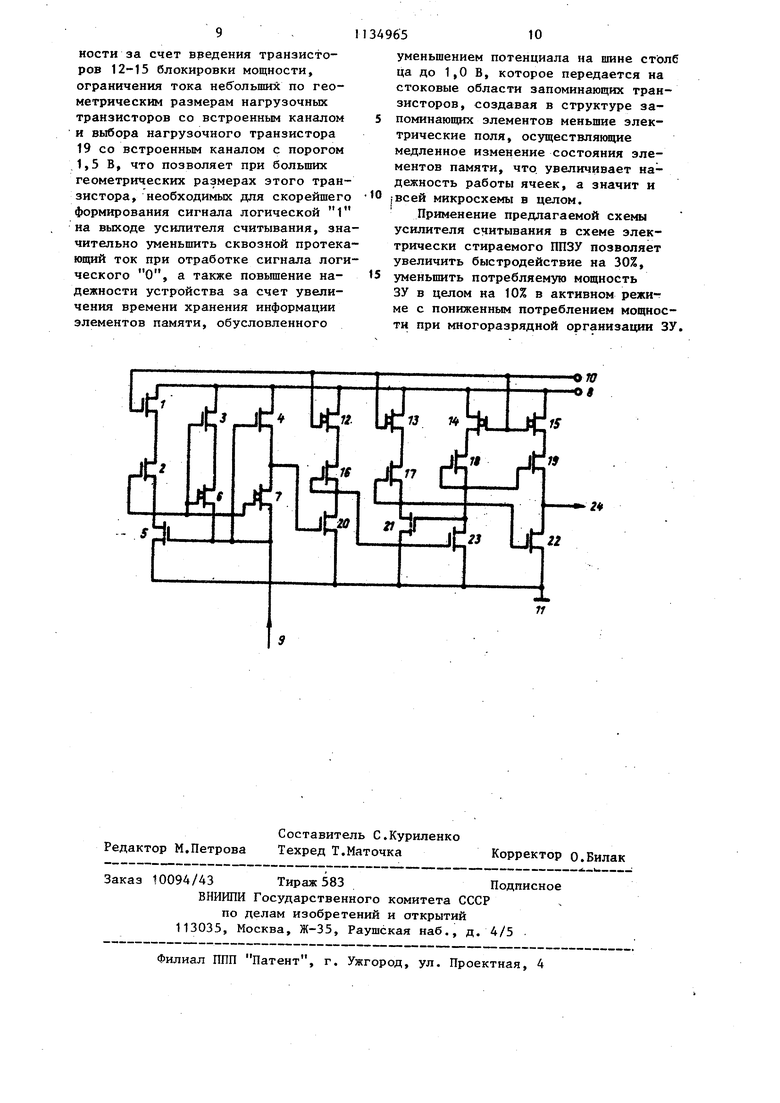

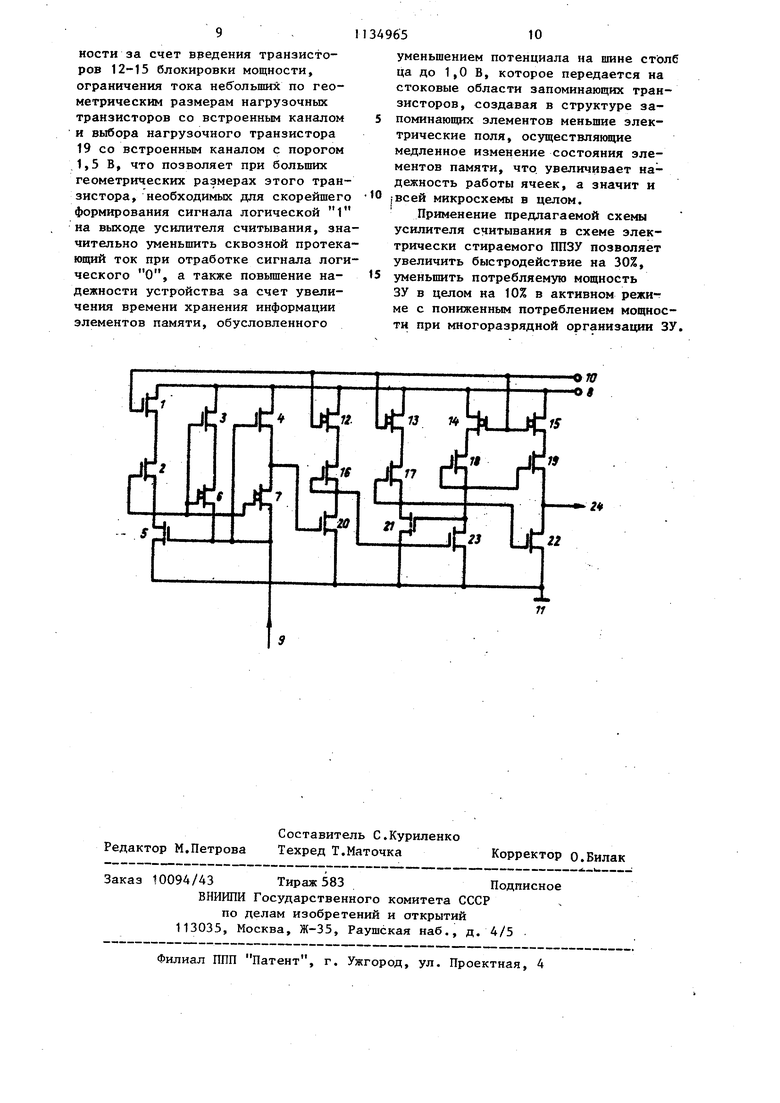

затвор которого соединен с затвором третьего нагрузочного транзистора и подключен к информационному входу усилителя, при этом опорный и разрядный транзисторы вьтолнены на транзисторах с индуцированным каналом. На чертеже представлена электрическая схема предлагаемого усилителя. Усилитель считывания включает уз лы смещения напряжения и усиления. Узел смещения напряжения содержит ЦЩ1-транзистор 1 блокировки мощности с нулевым порогом, три нагрузочных ВДП-транзистора 2,3 и 4 со встр енным каналом, опорный ЩЩ-транзистор 5 с индуцированным каналом, зарядный МДП-траизистор б с нулевьм порогом, разрядный ВДП-транзистор 7 с нулевым порогом, нишу 8 питания, информационный вход 9 усилителя, ши ну 1О управления, шину 11 нулевого потенциала. Узел усипенйя содержит четыре ЩП-тpaнзиcтopa 12, 13, 14 и 15 блокировки мощности с нулевым порогом, четыре нагрузочных МДП-транзистора 16, 17,,18 и 19 со встроенным каналом три ключевых МДП- -транзистора 20, 21 и 22 с индуцированным каналом, разрядный МДП-транзистор 23 с индуцированным каналом. выход 24 усилителя считывания. Усилитель считывания работает в двух режимах: активном и пассивном. В активном режиме на шину 10 управления подается потенциал логической 1, открывающий транзисторы 1,12-15 блокировки М01ЦНОСТИ, которы выбраны с нулевьм порогом для умень шения потерь при передаче напряжения питания. К информационному входу 9 усилителя считывания подключается шина выбранного столбца, которая подсоединяется к выбранной ячей ке. Если ячейка находится в непрово дящем состоянии, т.е. состоянии логической 1, то в начальньй момент нулевой потенциал шины столбца 9, поступающий на затвор опорного тран зистора 5, способствует формировани на стоке этого транзистора потенциа ла, близкого к напряжению источника питания, открывающего транзисторы 3, 6 и 7, через которые идет быстры заряд емкости шины столбца. При это открывается транзистор 4 и начинает ся формирование высокого уровня на стоке разрядного транзистора 7. По мере увеличения напряжения на ши не столбца 9 за счет обратной связи приоткрывается опорный транзистор 5, потенциал на его стоке падает до напряжения примерно 1 , 6 В и зарядный 6 и разрядный 7 транзисторы закрываются, ограничивая потенциал заряда шины столбца на уровне примерно 1,0 В. В результате на стоке разрядного транзистора 7 формируется потенциал, превышающий потенциал на шине столбца на величину одного порогового напряжения нагрузочного транзистора 4, т.е. примерно 3,6 В при пороговом напряжении транзистора 4-3,0 В Если шина столбца 9 подключ ется к проводящей ячейке, т.е. находящейся в состоянии логического О, - то потенциал этой шины уменьшается за счет разряда емкости шины столбца через выбранную ячейку. Уменьшение напряжения шины столбца прийодит к тому, что нагрузочный транзистор 4 подзапирается, а разрядный транзистор 7 открывается и на стоке этого транзистора устанавливается потенциал, близкий к напряжению на истоке данного транзистора, т.е. примерно 1,3В. В предлагаемом усилителе считывания как и в прототипе за счет разной длины канала порог разрядного транзистора 7 на 0,1 В меньше порога зарядного транзистора 6 независимо от технологических разбросов. Это приводит к тому, что зарядньй транзистор 6 может открываться только тогда, когда потенциал на шине столбца упадет на 0,1 В по отношению к начальной величине 1,0 В. Ток заряда через нагрузочный транзистор 3 и зарядный транзистор 6 вызывает ограничение тока разряда шины столбца 9 на величину, не более чем на 0,1 В. Ток заряда через открытые нагрузочньй транзистор 4 и разрядный транзистор 7 незначителен из-за малых геометрических размеров нагрузочного транзистора 4 и обеспечивает только заряд емкостной нагрузки на стоке разрядного транзистора 7. В предлагаемом усилителе благодаря наличшо обратной связи уменьшение напряжения на шине столбца 9 на 0,02 В вызывает подзапирание опорного .транзистора 5, что приводит к увеличению напряжения на стоке этого транзистора на величину 0,2 В, т.е. примерно 1,8В. Таким образом, десятикратно увеличенное изменение напряжения на шине столбца 9 поступает на затвор разря ного транзистора 7, открывает его и тем самым способствует скорейшему формированию на стоке этого транзис тора потенциала, соответствующего считанному логическому О, а также поступает на затвор зарядного транзистора 6, открывает его намного раньше, не дожидаясь уменьшения напря сения на шине столбца на величину 0,1 В, вызывая ограничение тока разряда и тем самым способствуя скорейшему завершению процесса считывания логического О. В результа те перепад на стоке разрядного тран зистора 7 находится между 1,3 и 3,6 В, который поступает на узел усиления, преобразующий перепад 1,3 - 3,6 В в перепад 0,2-5,0 В. Если на затвор ключевого транзистора 20 поступает потенциал 1,3 который соответствует считанному ло гическому О, то благодаря выбору геометрических размеров транзисторов 12, 16 и 20 на стоке ключевого транзистора 20 формируется потенциа логической 1 2,5 В, поступающий на затвор разрядного транзистора 23 на стоке которого благодаря выбору геометрических размеров транзисторо 14, 18 и 23 устанавливается потенци ал логического О 0,2 В, закрываюпщй ключевой транзистор 21 и нагрузочцый транзистор 19. Вследствие эт го на выходе усилителя считывания формируется потенциал логического 0,2 В, соответствующий считываемому состоянию логического О. Если на затвор ключевого транзис тора 20 поступает потенциал 3,6 В, соответствующий считываемому состоянию логической 1, то на стоке ключевого транзистора 20 устанавливается уровень логического О 0,2 В, закрывающий разрядный транзистор 23, на стоке которого формиру тся потенциал, близкий к напряже нию источника питания, открывающий транзистор 19, который работает в крутой области и тем самым обеспечивает максимальный ток заряда емкостной нагрузки усилителя считывания . Для уменьшения сквозных протекающих токов геометрические размеры нагрузочных транзисторов 2, 16, 17 и 18 выбраны минимальными, кроме того, при отработке сигнала логического О на выходе 24 усилителя считывания нагрузочный транзистор 19 взят с порогом - 1,5 В. Таким образом, в схеме усилителя считывания в активном режиме обеспечивается малая величина потребляемой мощности. В пассивном режиме на шину 10 управления подается потенциал логического О, запирающий транзисторы 1,12-15 блокировки мощности. На стоке опорного транзистора 5 устанавливается напряжение, близкое к логическому О, закрьшающее зарядный 6 и разрядный 7 транзисторы. На стоке разрядного транзистора 7 формируется потенциал 1,5 или 2,8 iB в зависимости от того, выбрана ячейка или невыбрана. Данный потенциал, поступая на затвор ключевого транзистора 20, в пассивном режиме обеспечивает на стоке этого транзистора формирование уровня логического О. При этом на стоках ключевого 21 и разрядного 23 транзисторов также устанавливаетСя уровень логического О. Таким образом, в момент переключения схемы в пассивный режим информация на выходе 24 усилителя считывания не изменяется. В результате благодаря введению транзисторов блокировки мощности и отсечке зарядного 6 и разрядного 7 транзисторов полностью исключаются сквозные протекающие токи, что приводит к .тому, что схема в пассивном режиме практически не потребляет мощности. Преимуществами предлагаемого усилителя считывания по сравнению с известными являются повышение быстродействия при использовании в ЗУ большой информационной емкости за счет введения обратной связи в цепи узла смещения напряжения, позволявшей увеличить чувствительность усилителя до 20 мВт, что приводит к значительному сокращению времени заряда и разряда емкостной нагрузки информационного входа усилителя, и введения в узел усиления цепи из трех транзисторов 15, 19 и 22 и такого вкпючениг нагрузочного транзистора 19, работающего в крутой области, который обеспечивает крутой фронт при формировании сигнала логической 1, уменьшение потребляемой мощ9ности за счет введения транзисторов 12-15 блокировки мощности, ограничения тока небольших по геометрическим размерам нагрузочных транзисторов со встроенным каналом и выбора нагрузочного транзистора 19 со встроенным каналом с порогом 1,5В, что позволяет при больших геометрических размерах этого транзистора, необходимых для скорейшего формирования сигнала логической 1 на выходе усилителя считывания, зна чительно уменьшить сквозной протека ющий ток при отработке сигнала логи ческого О, а также повьппение надежности устройства за счет увеличения времени хранения информации элементов памяти, обусловленного 510 уменьшением потенциала на шине стЬлб ца до 1,0 В, которое передается на стоковые области запоминающих транзисторов, создавая в структуре запоминающих злементов меньшие электрические поля, осуществляющие медленное изменение состояния элементов памяти, что. увеличивает надежность работы ячеек, а значит и всей микросхемы в целом. Применение предлагаемой схемы усилителя считывания в схеме электрически стираемого ППЗУ позволяет увеличить быстродействие на 30%, уменьшить потребляемую мощность ЗУ в целом на 10% в активном режиме с пониженным потреблением мощности при №огоразрядной организации ЗУ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4223394, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США И 4266283, | |||

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1985-01-15—Публикация

1983-04-07—Подача