блока, соединены с входами последующих разрядов третьего и четвертого регистров сдвига через третий и четвертый элементы запрета/ а выходы четвертого арифметического сумматора являются выходами декодера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Пороговый декодер сверточного кода | 1981 |

|

SU1046958A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

КОДЕК .СВЕРТОЧНОГО КОДА ДЛЯ КАНАЛА С ДВУКРАТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ, содержащей на передающей стороне регистр сдвига, выход последнего разряда которого подключен к входу сумматора по модулю два, а на приемной стороне первый и второй регистры сдвига, выходы последних разрядов которых подключены к входам сумматора по модулю два, а также пороговый блок, отличающийся тем, что, с целью повышения помехоустойчивости, на передакадей суороне введены второй регистр сдвига и два арифметических сумматора, причем входы первого и второго регистров сдвига являются информационными входами кодека и объединены с первым и третьим входами первого арифметического сумматора, к второму и четвертому входам которого подключены выходы соответствующих разрядов первого и второго регистров сдвига, выход последнего разряда второго регистра сдвига подклю1чен к второму входу сумматрра по модулю два и к третьему входу второго арифметического сумматора, к первому, второму и четвертому входам которого подключены выходы сукматора по модулю два и первого арифметического сумматора, причем выходы второго арифметического сумматора являются проверочными входами кодера, а на приемной стороне введены четыре арифметических сумматора, третий и четвертый регистры сдвига, два элемента И, четыг ре элемента запрета, при этом информационными вхЬдами декодера являются входы первого и второго регистров сдвига, а также второй и четвертый входы первого арифметического сумматора, к первому, и третьему входам которого подключены выходы соответствунядих разрядов первого и второго регистров сдвига, выходы первого арифметического сумматора подключены к второму и четвертому входам второго арифметического сукматора, к первому и треть.ему входам которого подi (слючены выходы сумматора по модулю Цва и последнего разряда второго (Л регистра сдвига соответственно, выкоды второго арифметического сумматора подключены к первому и второму входам третьего арифметического сумматора, первый и второй инверсные входы которого являются проверочными входами декодера, выходы Третьего арифметического сумматора сд подключены к соответствующим входампорогового блока и через первый и втосо да рой элементы запрета к входам третьего и четвертого регистров сдвига,выходы lOO определенных разрядов которых подключены к соответствующим входам порогоМ вого блока, выход которого подключен к 5Т1равляк1цим входам каждого элемента запрета и к первым входам элементов И,к вторым входам которых подключены выходытретьего и четвертого pefifCTров сдвига, выходы элементов И подключены к первому и второму инверсньм входам четвертого ари етического сум-матора, к первому и второму входам которого подключены выходы первого и второго регистров сдвига, -причем выходы разрядов третьего и четвертоiro регистров сдвига, подключенные к соответствующим входг1м порогового

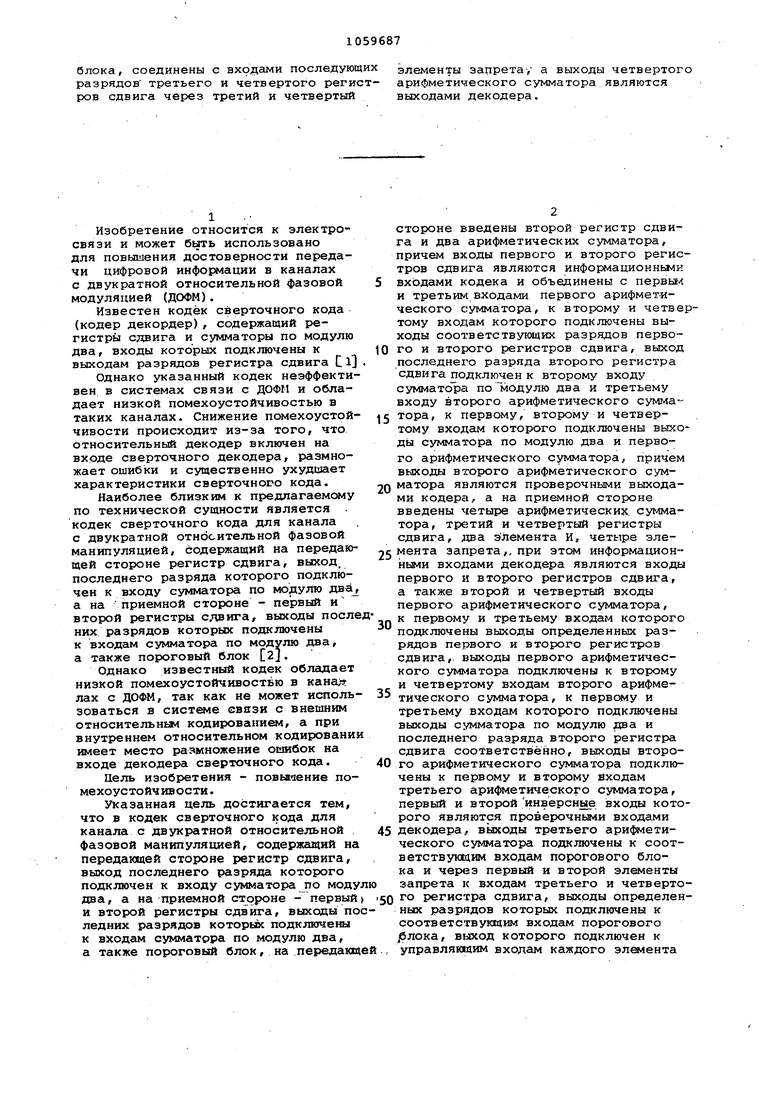

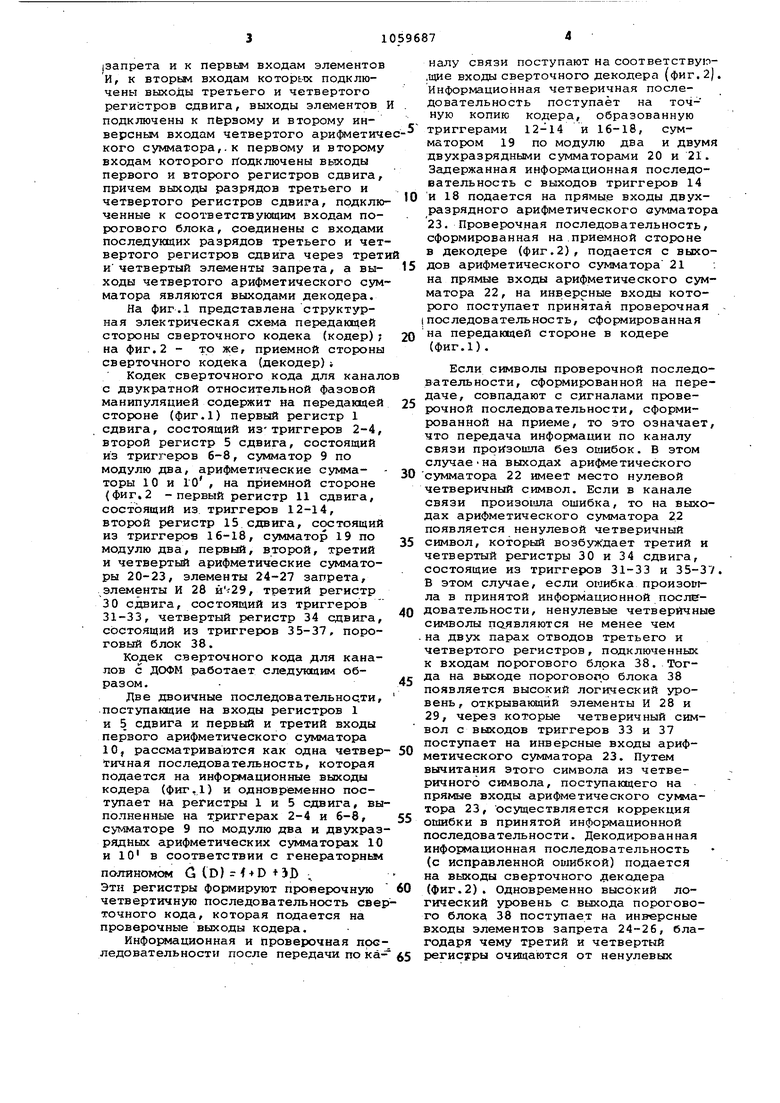

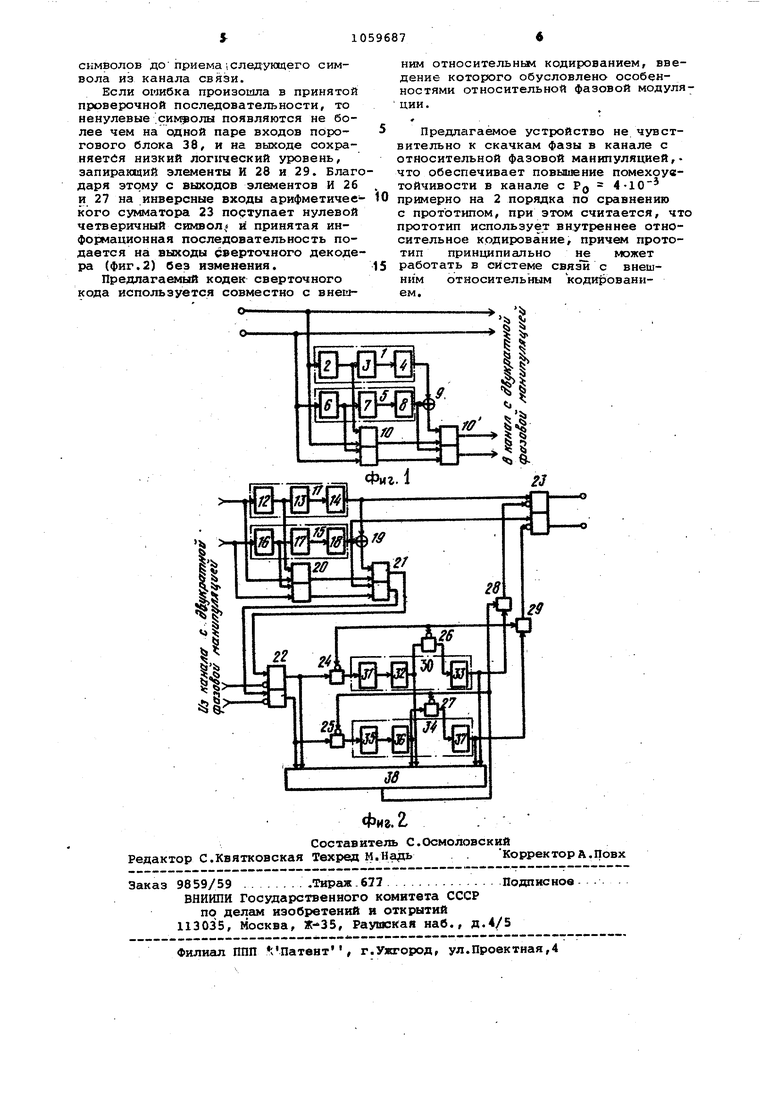

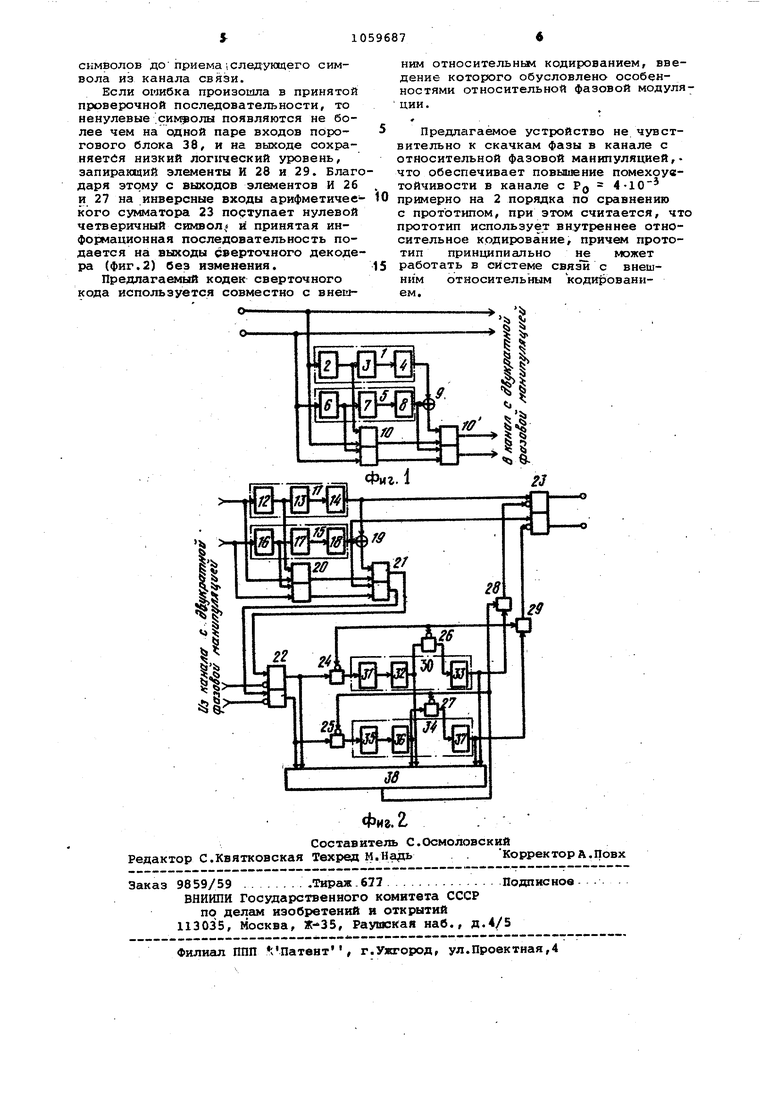

Изобретение относится к электросвязи и может быть использовано для повытения достоверности передачи цифровой информации в каналах с двукратной относительной фазовой модуляцией (ДОФМ). Известен кодек сверточного кода (кодер декордер), содержащий регистры сдвига и сумматоры по модулю два, входы которых подключены к выходам разрядов регистра сдвига Сl Однако указанный кодек неэффекти вен в системах связи с ДОФМ и обладает низкой помехоустойчивостью в таких каналах. Снижение помехоустой чивости происходит из-за того, что относительный декодер включен на входе сверточного декодера, размножает ошибки и существенно ухудшает характеристики сверточного кода. Наиболее близким к предлагаемсму по технической сущности является кодек сверточного кода для канала с двукратной относительной фазовой манипуляцией, содержащий на передаю щей стороне регистр сдвига, выход, последнего разряда которого подключен к входу сумматора по модулю два а на приемной стороне - первый и второй регистры сдвига, выходы посл них разрядов которых подключены к входам сумматора по модулю два, а также пороговый блок 2. Однако известный кодек обладает низкой помехоустойчивостью в канад лах с ДОФМ, так как не может исполь зоваться в cиcтйvIe связи с внешним относительным кодированием, а при внутреннем относительном кодировани имеет место размножение ошибок иа входе декодера сверточного кода. Цель изобретения - повЕЯ ение помехоустойчивости. Указанная цель достигается тем, что в кодек сверточного кода для канала с двукратной относительной фазовой манипуляцией, содержащий на передающей стороне регистр сдвига, выход последнего разряда которого подключен к входу сумматора по моду два, а на приемной стороне - первый и второй регистры сдвига, выходы по ледних разрядов KOTOpiK подключены к входам сумматрра по модулю два, а также пороговый блок, на передающ стороне введены второй регистр сдвига и два арифметических сумматора, причем входы первого и второго регистров сдвига являются информационньми входами кодека и объединены с первьг и третьим входами первого арифметического сумматора, к второму и четвертому входам которого подключены выходы соответствукяцих разрядов первого и ВТО1ХЭГО регистров сдвига, выход последнего разряда второго регистра сдвига подключен к второму входу сумматора подмодулю два и третьему входу второго арифметического сумматора, к первому, второму и четвертому входам которого подключены ВЕЛХОды сумматора по модулю два и первого арифмегтического сумматора, причем выходы второго арифметического сумматора являются проверочными выходами кодерс1, а на приемной стороне введены четыре арифметических, сумматора, трегтий и четвертый регистры сдвига, два элемента И, четыре элемента запрета,, при этсяи информационньми входами декодера являются входы первого и второго регистров сдвига, а также второй и четвертый входы первого с1рифметического сумматора, к первому и третьему входам которого подключены выходы определенных разрядов первого и второго регистров сдвига,- выходы первого арифметического сумматора подключены к второму и четвертому входам второго арифметического сумматора, к первому и третьему входам которого подключены выходы сумматора по модулю два и последнего разряда второго регистра сдвига соответственно, выходы второго арифметического сумматора подключены к первому и второму входам третьего арифметического сумматора, первый и второй инверсные входы которого являются проверочньми входами декодера, выходы третьего арифметического сумматора подключены к соответствующим входам порогового блока и чер«гз первый и второй элементы запрета к входам третьего и четвертого регистра сдвига, выхрды определенных разрядов которых подключены к соответствующим входам порогового блока, выход которого подключен к управляющим входам каждого элемента |3апрета и к первым входам элементов и, к вторым входам которь-тх подключены выходы третьего и четвертого регистров сдвига, выходы элементов подключены к первому и второму инверсным входам четвертого ари |метич кого сумматора,.к первому и второму входам которого подключены выходы первого и второго регистров сдвига, причем выходы разрядов третьего и четвертого регистров сдвига, подклю ченные к соответствукмцим входам порогового блока, соединены с входами последующих разрядов третьего и чет вертого регистров сдвига через трет ичетвертый элементы запрета, а выходы четвертого арифметического сум матора являются выходами декодера. На фиг.1 представлена структурная электрическая схема передагацей стороны сверточного кодека (кодер); на фиг.2 - то же, приемной стороны сверточного кодека (декодер)t Кодек сверточного кода для канал с двукратной относительной фаэовой манипуляцией содержит на передающей стороне (фиг.1) первый регистр 1 сдвига, состоящий изтриггеров 2-4, второй регистр 5 сдвига, состоящий из триггеров 6-8, сумматор 9 по модулю два, арифметические сумматоры 10 и 10 , на приемной стороне (фиг,2 -первый регистр 11 сдвига, состоящий из. триггеров 12-14, второй регистр 15 сдвига, состоящий из триггеров 16-18, сумматор 19 по модулю два, первый, второй, третий и четвертый арифметические сумматоры 20-23, элементы 24-27 запрета, элементы И 28 , третий регистр 30 сдвига, состоящий из триггеров 31-33, четвертый регистр 34 сдвига, состоящий из триггеров 35-37, пороговый блок 38. Кодек сверточного кода каналов с ДСХ&М работает следукшим образом. Две двоичные последовательности, поступагадие на входы регистров 1 и 5 сдвига и первый и третий входы первого арифметического сумматора 10, рассматриваются как одна четвер тичная последовательность, которая подается на информационные выходы кодера (фиг.1) и одновременно поступает на регистры 1 и 5 сдвига, вы полненные на триггерах 2-4 и 6-8, сумматоре 9 по модулю два и двухраз рядных арифметических сумматорах 10 и 10 в соответствии с генераторньм ПОЛИНОМОМ G ID) - I + D + ЗВ . Эти регистры формируют проверочную четвертичную последовательность свер точного кода, которая подается на проверочные выходы кодера. Информационная и проверочная последовательности после передачи по каналу связи поступают на соответствую,щие входы сверточного декодера (фиг. 2). Информационная четверичная последовательность поступает на точную копию кодера, образованную триггерами 12-14 и 16-18, сумматором 19 по модулю два и двумя двухразрядными сумматорами 20 и 21. Задержанная информационная последовательность с выходов триггеров 14 и 18 подается на прямые входы двухразрядного арифметического сумматора 23. Проверочная последовательность, сформированная на.приемной стороне в декодере (фиг.2), подается с выходов арифметического сумматора 21 ; на прямые входы арифметического сумматора 22, на инверсные входы которого поступает принятая проверочная (последовательность, сформированная на передагацей стороне в кодере (фиг.1). Если символы проверочной последовательности, сформированной на передаче, совпадают с сигналами проверочной последовательности, сформированной на приеме, то это означает, что передача информации по каналу связи произошла без ошибок. В этом случае на выходах ари етического сумматора 22 имеет место нулевой четверичный символ. Если в канале связи произошла ошибка, то на выходах арифметического сумматора 22 появляется ненулевой четверичный символ, который возбуждает третий и четвертый регистры 30 и 34 сдвига, состоящие из триггеров 31-33 и 35-37. В этом случае, если ошибка произошла в принятой информационной последовательности, ненулевые четверичные символы псгявляются не менее чем на двух парах отводов третьего и четвертого регистров, подключенных к входам порогового блока 38. Тогда на выходе порогового блока 38 появляется высокий логический уровень, от.крывакиций элементы И 28 и 29, через которые четверичный символ с выходов триггеров 33 и 37 поступает на инверсные входы арифметического сумматора 23. Путем вычитания этого символа из четверичного символа, поступающего на прямые входы арифметического сумлатора 23, осуществляется коррекция ошибки в принятой информационной последовательности. Декодированная информационная последовательность (с исправленной ошибкой) подается на выходы сверточного декодера (фиг.2). Одновременно высокий логический уровень с ВЕлхода порогового блока 38 поступает на инверсные входы элементов запрета 24-26, благодаря чему третий и четвертый регистры очищаются от ненулевых

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Касами Т | |||

| и др | |||

| Теория кодирования | |||

| М., Мир, 1978, с | |||

| Приспособление для нагрузки тендеров дровами | 1920 |

|

SU228A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, стр | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

Авторы

Даты

1983-12-07—Публикация

1982-09-16—Подача