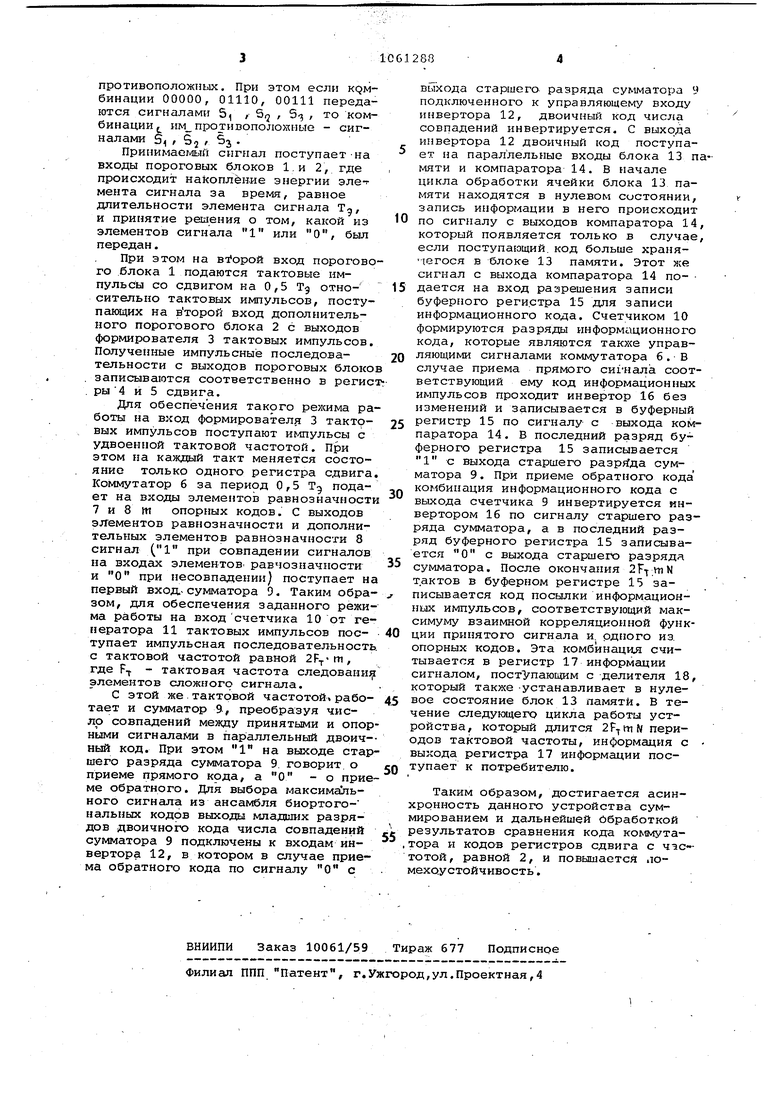

Изобретение ОТЕЮСИТСЯ к электросвязи . По осЕЮВНому авт. ев, № 853819, :1звестио устройство для приема многопозиционных сложных сигналов,содержащее последовательно соединенны генератор тактовых импульсов и счет чик, выход1.а которого подключены ко входам коммутатора, выходы которого подключены к первь1м входам элемент равнозначности, вторые входы и выходы которых соединены соответствен с выxoдa и регистра сдвига и входам сумматора, а также блок памяти и по роговый блок, выход которого подклю чен к первому входу регистра сдвига два инвертора, буферный регистр, делитель, регистр информации и компаратор, входы которого соединены с входами и вЕлходами блока памяти и выходаг и первого инвертора, к инфор мационным входам которого подключен выходы сумматора, соответствующий выход которого соединен с управляющими входаь1и инверторов и буферного регистра, выходы которого подклю чены к входам регистра информации, соответствующие входы которого соединены с дополнительны.м входом блок памяти, вторым выходом генератора тактовых импульсов и выходом делителя, вход которого соединен с соот ветствувощим выходом счетчика, входо порогового блока и вторым входом ре гистра сдвига, при этом выходы сче чика подключены к информационным входам второго инвертора, выходы которого соединены с входами буферного регистра, управляющий вход которого соединен с выходом компаратора и управляющим входом блока памяти l . Однако известное устройство имеет высокие энергетические потери при работе в асинхронном режиме по тактовой частоте. Цель изобретения - повышение помехоустойчивости °при работе в асинхронном режиме. Дпя этого в устройство для приема многопозицио п1ых сложных сигналов, содержащее последовательно сое диненные генератор тактовых импульсов и счетчик, выходы которого подключены к входам коммутатора, выходы которого подключены к первым входам элементов равнозначности, вторые входы и выходы которых соеди нены соответственно с вьоходами регистра сдвига и входами сумматора, а также блок памяти и пороговый бло выход, которого подключен к первому входу регистра сдвига, два инвертора, буферный регистр, делитель, регистр информации и компаратор, вход которого соединены с входами и выхо дами блока памяти и выходами первого инвертора, к информационным вхог дам которого подключены выходы сумматора , соответствующий выход которого соединен с управляющими входами инвесторов и буферного регистра, выходы которого подключены к входам регистра информации, соответствующие входы которого соединены с дополнительным входом блока памяти, вторым выходом генератора тактовых импульсов и выходом делителя, вход которого соединен с соответствующим выходом счетчика, входом порогового блока и вторым входом регистра сдвига, при этом выходы счетчика подключены к информационным входам второго инвертора, выходы которого соединены с входами буферного регистра, управляющий вход которого соединен с выходом компаратора и управляющим входом блока памяти, введены дополнительные пороговый, блок, регистр сдвига и элементы равнозначности, а также формирователь тактовых импульсов, причем вход делителя соединен с одним входом порогового блока через формирователь тактовых импульсов, другой выход которого соединен с одним входом дополнительного порогового блока, другие входы пороговых блоков объединены и являются входом устройства, выход дополнительного порогового блока соединен с первым входом дополнительного регистра сдвига, второй вход которого соединен с другим выходом формирователя тактовых импульсов, а выходы - с первыми входами дополнительных элементов равнозначности, вторые входы которых соединены с вкходами коммутатора, а выходы - с дополнительными входами сумг атора. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство содержит пороговые блоки 1 и 2 , формирователь 3 тактовых импульсов,регистры 4 и 5 сдвига коммутатор 6, элементы равнозначности 7 и 8, сумматор 9, счетчик 10, генератор 11 тактовых импульсов, инвертор 12, блок 13 памяти, компаратор 14, буферный регистр 15, инвертор 16, регистр 17 информации делитель 18. Устройство работает следующим образом. Входной сигнал, несущий информацию, представляет собой многопозиц-ионный биортогональный код дликоторый строят так, чтобы свести к минимуму ошибки в информационной последовательности. Например, для передачи информации паучками по пять информационных символов требуется 2 2т 32 сигнала, из которых 16.прямых и 16

противоположных. При этом если KQMбинации 00000, 01110, 00111 передаются сигналами 5, / 5 , 5- , то комбинации им противоположные - сигналами 5, , Sj л 5з .

Принимаег-/1ьш сигнал поступает -на входы пороговых блоков 1,и 2, где происходит накопление энергии элемента сигнала за время, равное длительности элемента сигнала Тд, и принятие решения о том, какой из элементов сигнала 1 или О, был передан.

При этом на второй вход порогового блока 1 подаются тактовые импульсы со сдвигом на 0,5 Тд относительно тактовых импульсов, поступающих на второй вход дополнительного порогового блока 2 с выходов формирователя 3 тактовых импульсов. Получеш ые импульсные последовательности с выходов пороговых блоков записываются соответственно в регист. ры 4 и 5 сдвига.

Дпя обеспечения такого режима работы на вход формирователя 3 тактрвых импульсов поступают и шyльcы с удвоенной тактовой частотой. При этом на каждый такт меняется состояние только одного регистра сдвига. Коммутатор 6 за период Of5 Tg подает на входы элементов равнозначности 7 и 8 tti опорных кодов. С выходов элементов равнозначности и дополнительных элементов равнозначности 8 сигнал (1 при совпадении сигналов на входах элементов равнозначности и О при несовпадении) поступает на первый вход.-сумматора 9. Таким образом, для обеспечения заданного режима работы на вход счетчика 10 от генератора 11 тактовых импульсов поступает импульсная последовательность, с тактовой частотой равной , где Ff - тактовая частота следовани) элементов сложного сигнала.

С этой же тактовой частотой, работает и сумматор 9, преобразуя число совпадений между принятыми и опорными сигналами в параллельный двоич-ньлй код. При этом 1 на выходе старшего разряда сумматора 9. говорит, о приеме прямого кода, а О - о приеме обратного. Для выбора максимального сигнала из ансамбля биортогональных кодов выходы младших разрядов двоичного кода числа совпадений сумматора 9 подключены к входам инвертора 12, в котором в случае приема обратного кода по сигналу О с

выхода старшего разряда сумматора У подключенного к управляющему входу И 1вертора 12, двоичный код числа совпадений инвертируется. С выхода инвертора 12 двоичный код поступает на параллельные входы блока 13 пмяти и компаратора 14. В начале цикла обработки ячейки блока 13 памяти находятся в нулевом состоянии, запись информации в него происходит по сигналу с выходов компаратора 14 который появляется только в случае если поступающий, код больше хранящегося в блоке 13 памяти. Этот же сигнал с выхода компаратора 14 по- дается на вход разрешения записи буферного реги.стра 15 для записи информационного кода. Счетчиком 10 формируются разряды информационного кода, которые являются также управляющими сигналами коммутатора 6. В случае приема прямого си1нала соответствующий ему код информационных импульсов проходит инвертор 16 без изменений и записывается в буферный регистр 15 по сигналу с выхода компаратора 14. В последний разряд буферного регистра 15 записывается 1 с выхода старшего разряда сумматора 9. При приеме обратного кода комбинация информационного кода с выхода счетчика 9 инвертируется инвертором 16 по сигналу старшего разряда сумматора, а в последний разряд буферного регистра 15 записывается О с выхода старшего разряда сумматора. После окончания 2Ff.niN т.актов в буферном регистре 15 записывается код посылки информационных импульсов, соответствующий максимуму взаимной корреляционной функции принятого сигнала и. одного из. опорных кодов. Эта комбинация считывается в регистр 17 информации сигналом, поступающим с делителя 18 который также -устанавливает в нулевое состояние блок 13 памяти. В течение следующего цикла работы устройства, который длится 2FfmH( периодов тактовой частоты, информация с выхода регистра 17 информации поступает к потребителю.

Таким образом, достигается асинхронность данного устройства суммированием и дальнейшей Обработкой результатов сравнения кода коммутатора и кодов регистров сдвига с чэс тотой, равной 2, и повышается ломехоустойчивость.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема многопозиционныхСлОжНыХ СигНАлОВ | 1979 |

|

SU853819A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для приема многопозиционных дискретных частотно-фазоманипулированных сигналов | 1987 |

|

SU1501301A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для сжатия и обработки информации | 1990 |

|

SU1742842A1 |

| Датчик испытательных текстов | 1988 |

|

SU1571786A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОПОЗИЦИОННЫХ: СЛОЖНЫХ СИГНАЛОВ по авт. св. 853819, о т л и ч а- юц е е с я тем, что, с целью повышения помехоустойчивости при работе в асинхронном режиме, введены дополнительные пороГОВЕЛИ блок, регистр сдвига н элементы равнозначности, а также формирователь тактовых импульсов, причем вход делителя соединен с одним входом порогового блока через формирователь тактовых импульсов, другой выход которого соединен с одним входом дополнительного порогового блока, другие входы пороговых блоков объединены и являются входом устройства, ВЫХОД дополнительного порогового блока соединен с первым входом дополнительного регистра сдвига, второй вход которого соединен с другим выходом формирователя такювых импульсов, а выходы - с первыми входами дополнительных элементов равнозначности, вторые входы которых соединены с выходами ког 1мутато-§ ра, а выходы - с дополнительными (Л входами- сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для приема многопозиционныхСлОжНыХ СигНАлОВ | 1979 |

|

SU853819A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| , | |||

Авторы

Даты

1983-12-15—Публикация

1982-08-11—Подача