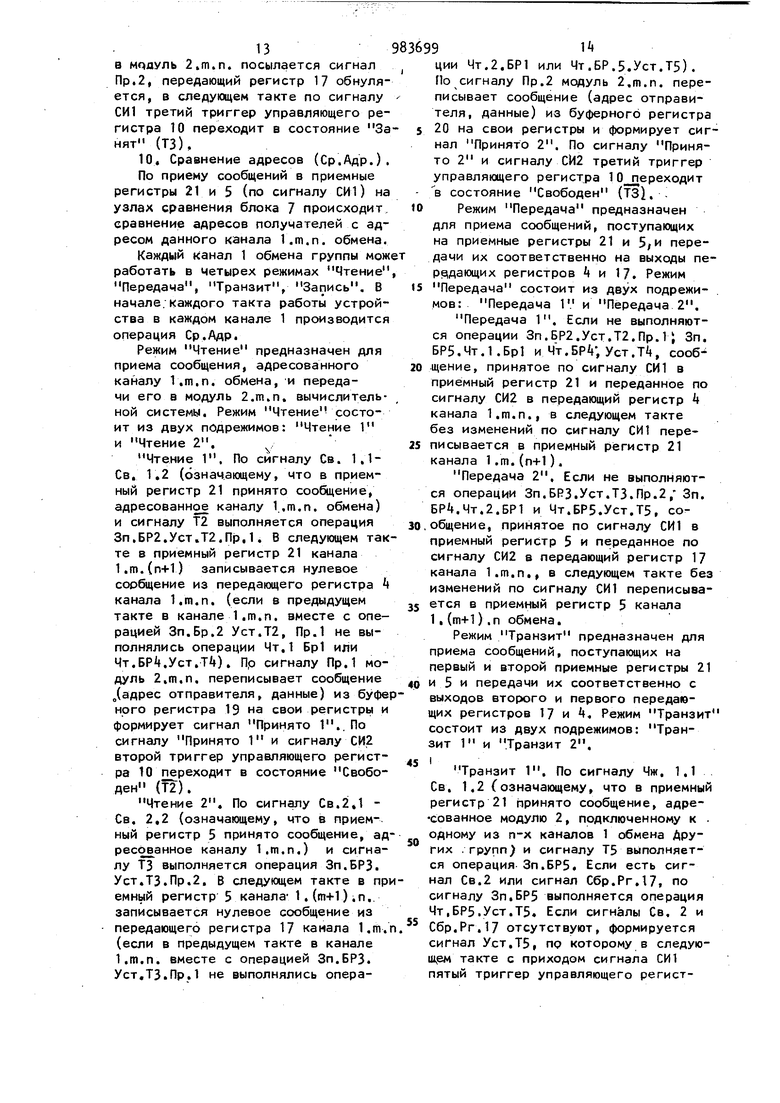

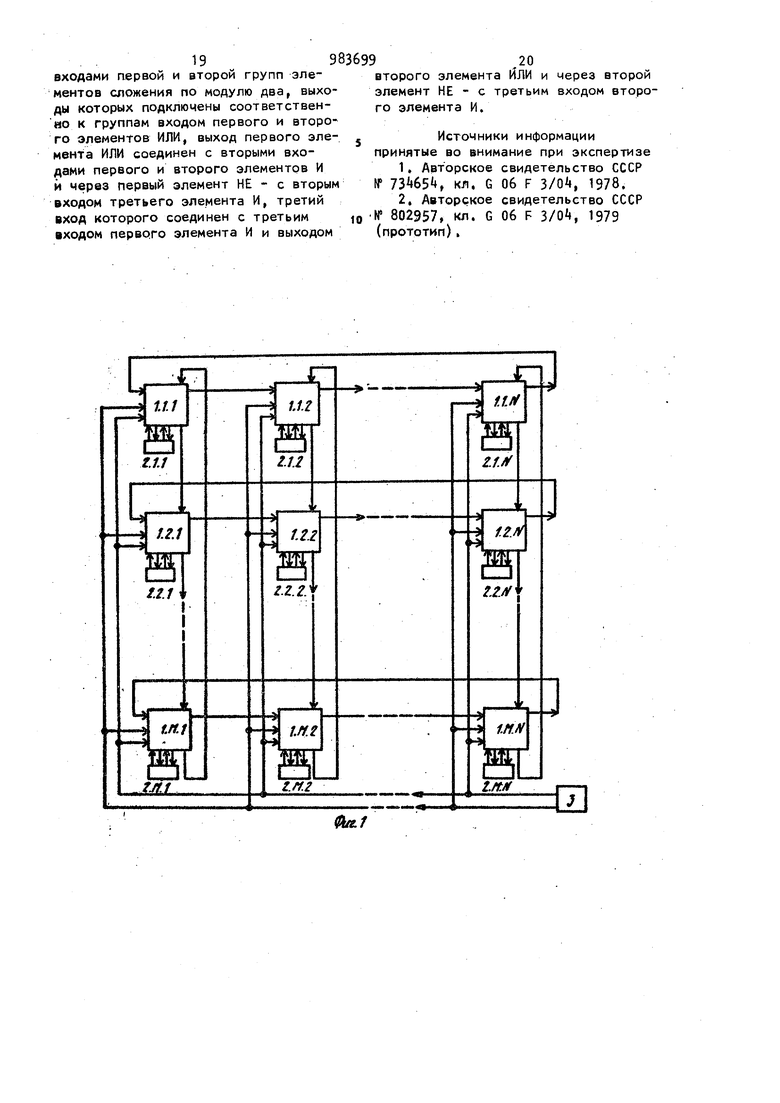

Изобретение относится к вычислительной технике и может быть использовано при проектировании ЭВМ и муль типроцессорных вычислительных систем Известны устройства связи для вычислительной системы, содержащие блок синхронизации и группу каналов, каждый из которых включает приемный и передающий регистры, элемент ИЛИ, управляющий регистр, регистр адреса, распределитель импульсов, узел синхронизации, Йлок сравнения, буферный регистр и узел коммутации управляющих сигналов l . , Недостаток этих устройств состоит в низком быстродействии. Наиболее близким к изобретению по технической сущности является уст ройство .связи для вычислительной системы, содержащее блок синхронизации и М блоков сопряжения, каждый из которых включает приемный и передающий регистры, распределитель импульсов. управляющий регистр, узец коммутации управляющих сигналов,схему сравнения, узел синхронизации, первый, второй и третий буферные регистры, элементы ИЛИ, регистр адреса, регистр сосостояния и коммутатор информации, причем, выход передающего регистра , К-го блока сопряжения (К 1, М) соединен с информационным входом приемного регистра (к + 1)-го блока сопряжения, выход передающего регистра М-го блока сопряжения соединен с информационным входом приемного регистра первого блока српряжения, а в каждом блоке сопряжения выход приемного регистра подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом первого буферного регистра, а выход - с информационным входом передающего регистра, выход которого подключен к первому входу . схемы сравнения, первый управляющий вход - к первому выходу блока синхро. низации, а второй управляющий вход39к первому выходу узла коммутации управляющих сигналов, второй выход которого связан с управляющим входом первого буферного .регистра, первый и второй входы - соответственно с выхо дом распределителя импульсов и узла синхронизации, а первый и второй входы-выходы - соответственно с выходами-входами схемы сравнения и управляющего регистра, выход регистра адреса соединен с вторым входом схем сравнения и первым информационным входом первого буферного регистра, вход распределителя импульсов подклю чен к управляющему входу приемного регистра и второму выходу блока синхронизации , груп,пы информационных и управляющих входов коммутатора инфор мации являются соответственно группа ми информационных и управляющих входов устройства, а первый и второй управляющие выходы коммутатора информации соединены соответственно с первым управляющим входом узла синхронизации и входом регистра состояния, вход-выход которого подключен к выход-входу узла коммутации управ- ляющих сигналов, седьмой выход которого связан с входом коммутатора информации, первым и вторым информационными входами подключенного сЬотве ственно к выходу из первой группы инфор мационных выходов устройства и второму информационйому входу пер во гобуферно го регистра , третий выход узла коммута ции управг яющих сигналов является выходом из второй группы управляющих выходов устройства, четвертый и пятый выход подключены соответственно к управляющим входам второго и третьего буферных регистров, информационные входы которых соединены с выходом передающего регистра, а выходы соответственно с вторым входом элемента ИЛИ и с выходом из второй груп пы информационных выходов устройства второй управляющий вход узла синхронцзации соединен с входом управляюще го регистра и первым управляющим входом передающего регистра, а трети управляющий вход - с шестым выходом узла коммутации управляющих сигналов Недостаток этого устройства состоит в снижении быстродействия по мере увеличения числа подключаемых модулей, в результате чего увеличи.вается время обмена сообщениями меж ду модулями. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство связи для вычислительной системы, содержащее блок формирования тактовых импульсов и первую группу каналов обмена, причем п-ый канал обмена первой группы (п 1, N) содержит первые приемный и передающий .регистры, первый элемент ИЛИ, блок-сравнения, регистр адреса, управляющий регистр, блок коммутации управляющих сигналов и три буферных регистра, управляющие входы которых соединены соответственно с первым, вторым и третьим выходами блока коммутации управляющих сигналов, четвертым и пятым выходами соединенного соответственно с первым управляющим входом первого передающего регистра и первым входом управляющего регистра, второй вход которого соединен с первым входом блока коммутации управляющих сигналов, управляющим входом первого приемного регистра и первым выходом блока формирования тактовых импульсов, второй выход которого соединен с вторым управляющим входом первого передающего регистра и третьим входом управляющего регистра, выход которого подключен к второму входу блока коммутации управляющих сигналов, второй и третий выходы и второй вход которого являются п-ым управляющим выходом первой группы устройства, четвертый вход управляющего регистра и.третий вход блока коммутации управляющих сигналов являются п-ым управляющим входом первой группы устройства, четвертый вход блока коммутации управляющих сигналов подключен к выходу блока сравнения, первым входом подключенного к выходу регистра адреса и первому информационному входу первого буферного регистра, второй информационный вход которого связан сП|-ым информационным входом первой группы устройства, выходы второго и третьего буферных регистров являются п-ым информационным выходом первой группы устройства, информационный вход второго буферного регистра связан с вторым входом блока сравнения, первым входом первого элемента ИЛИ и выходом первого приемного регистра, информационный вход которого подключен к выходу первого передающего регистра (n-l)-ro канала обмена первой группы, информационный вход первого передающего регистра соединен с выходом первого элемента ИЛИ, выход первого передающего регистра N-ro канала обмена первой группы соединен с информационным входом первого приемного регистра первого канала обмена первой группы, введены М-1 группа каналов обмена по N каналов в каждой группе, а в каждый кана обмена введены вторые приемный и передающий регистры, второй элемент ИЛИ, четвёртый и пятый буферные регистры, первмй и второй элементы И, блок выбора магистрали и регистр при знака передачи, причем в п-ом канале обмена т-ой группы (т 1, М) первый и второй входы регистра признака передачи соединены соответственно с пероым и третьим входами управляющего регистра, а третий вход - с выходом блока выбора магистрали,, управля ющий вход которого связан с шестым выходом блока коммутации управляющих сигналов, пятым входом соединенного с выходом регистра признака передачи, а седьмым и восьмым выходами соответственно с управлякяцими входам первого и второго элементов И, инфор мационные входы которых подключены к информационному выходу первого буферного регистра и первому информаци онному входу блока выбора магистрали вторым информационным входом связанного с информационным выходом регистра адреса, информационные выходы первого и второго элементов И соединены соответственно с вторым входом первого элемемента ИЛИ и первым входом второго-элемента ИЛИ, третий зход первого элемента ИЛИ и второй вход второго элемента ИЛИ соединены соответственно с выходамичетвертого И пятого буферных регистров, первые и вторые управляющие входы которых подключены соответственно к девятому двенадцатому выходам блока коммутации управляющих сигналов, тринадцатый выход которого соединен с первым управляющим входом второго передающего регистра, вторым управляющим входом связанного с вторым управляющим входом первого передающего регистра, а выходом - с информационным входом второго приемного регистра п-го канала обмена (т+1)-ой группы, информационный вход второго приемноГО регистра п-го канала обмена гп-ой группы подключен к выходу второго передающего регистра п-го канала обмена (т-1)-ой группы, информационный вход второго приемного регистра п-го канала обмена первой группы соединен с выходом второго передающего регистра п-го канала обмена М-ой . группы, в каждом канале обмена управляющий вход второго приемного регистра соединен с управляющим входом первого приемного регистра, выход которого подключен к информационному входу пятого буферного регистра, выход второго элемента ИЛИ связан с информационным входом второго передающего регистра, а третий вход - с выходом второго приемного регистра, информационными входами третьего и четвертого буферных регистров и третьим входом блока сравнения, второй информационный вход первого буферного регистра, выходы второго и третьего буферных регистров, второй вход и второй и третий выходы блока коммутации управляющих сигналов, третий вход блока коммутации управляющих сигналов и. четвертый вход управляющего регистра п-го канала т-ой группы являются соответственно п-ми информационными входом и выходом, п-ми управляющими выходом и входом т-ой группы устройства. Кроме того, блок выбора магистрали содержит две группы элементов сложения по модулю два, два элемен- та ИЛИ, два элемента НЕ и три элемента И, причем выходы элементов И подключены к выходу блока, а первые входы - к управляющему входу блока, первый и второй информационные входы которого связаны соответственно с первыми и вторыми входами первой и второй групп элементов сложения по модую два, выходы которых подключены соответственно к группам входов первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с вторыми входами первого и второго элементов И и через первый элемент НЕ.- с вторым входом третьего элемента И, третий вход которого соединен с третьим входом первого элемента И и выходом второго элемента ИЛИ и через второй элемент НЕ с третьим входом второго элемента И. На фиг. 1 представлен а структура вычислительной системы; на фиг. 2 -: блок-схема канала обмена, на фиг.З и k - функциональные схемы блока коммутации управляющих сигналов и блока выбора магистрали. Вычислительная система состоит (фиг. 1) из каналов 1 обмена, модулей 2 вычислительной системы и блок 3 формирования тактовых импульсов. Каналы 1 обмена организованы в матр цы из М строк и N столбцов и обозна чены через 1. m п, где m - номер строки (группы), а п - номер столбц (канала в группе), причем ,N, ,M. Каждый канал 1 обмена содержит (фиг. 2) первый передающий регистр k, второй приемный регистр 5, четвертый буферный регистр 6, блок::7 сравнения, пятый буферный регистр В, регистр 9 адреса, управляющий регистр 10, блок 11 коммутации упра ляющих сигналов, второй элемент ИЛИ 12, блок 13 выбора магистрали,. регистр 14 признака передачи, элементы И 15 и 16, второй передающий регистр 17, первый, второй и третий буферные регистры 18-20, первый при . емный регистр 21 и первый элемент ИЛИ 22. Блок 7 сравнения содержит два уз

ла сравнения, в первом узле сравнения блока 7 происходит сравнение разрядов поля адреса получателя и инвертирование разряда поля СвободноУ /Занято формата сообщения, принято го в первйй приемный регистр 21 (в поПе адреса старшие разряды предста ляют номер группы (строки) в двоичном представлении, а младшие разряды - номер канала обмена (столбца) в группе (строке) в двоичном представлении), соответственно с разряда ми адреса данного канала обмена, хранящегося в регистре 9 адреса. На выходе первого узла сравнения блока 7 формируются сигналы Чужой 1.1 1,.2 (Чж. 1.1 - Св. 1.2) , Свой 1. V - Свой 1.2 (Св. 1.1 Св. 1.2), Свободно 1 (Св. 1). Во втором узле, сравнения блока 7 происходит аналогичное сравнение поля адреса получателя и инвертирование разряда поля СвободНо / Занято фор мата сообщения, принятого во второй приемный pefMCtp 5, с адресом данного канала обмена, хранящегося в регистре 9 адреса. На выходе второго узла сравнения блока 7 формируютс .сигналы Свой 2.1 - Чужой 2.2

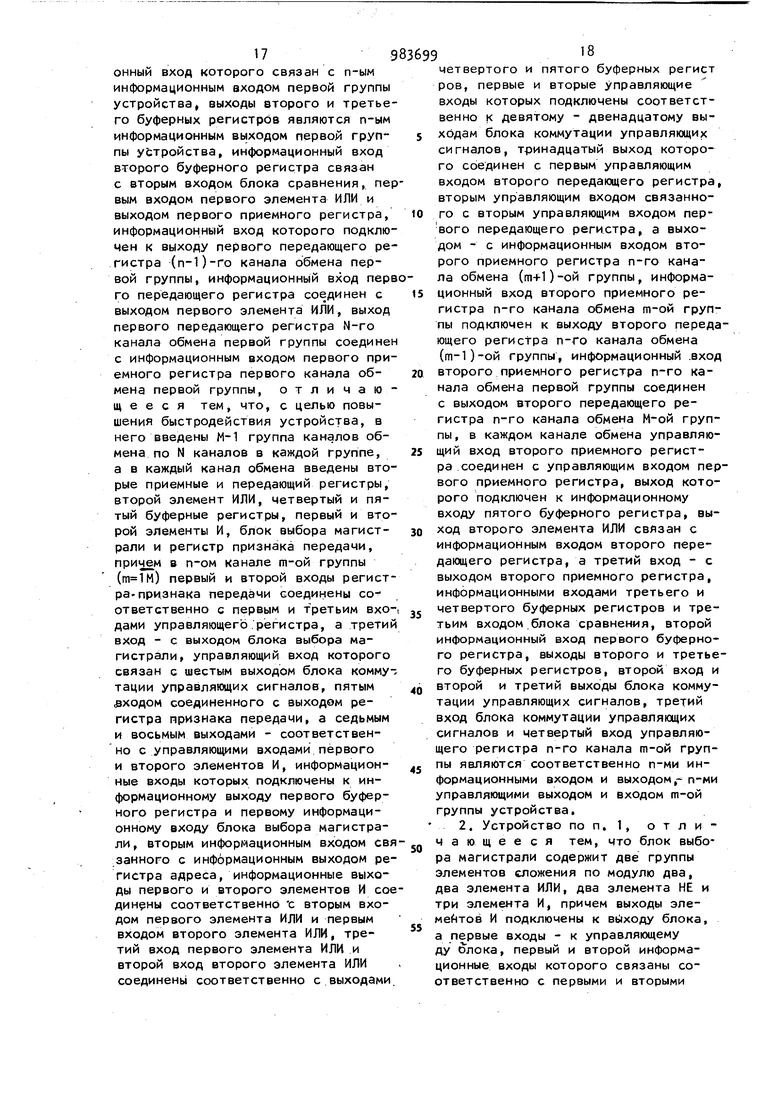

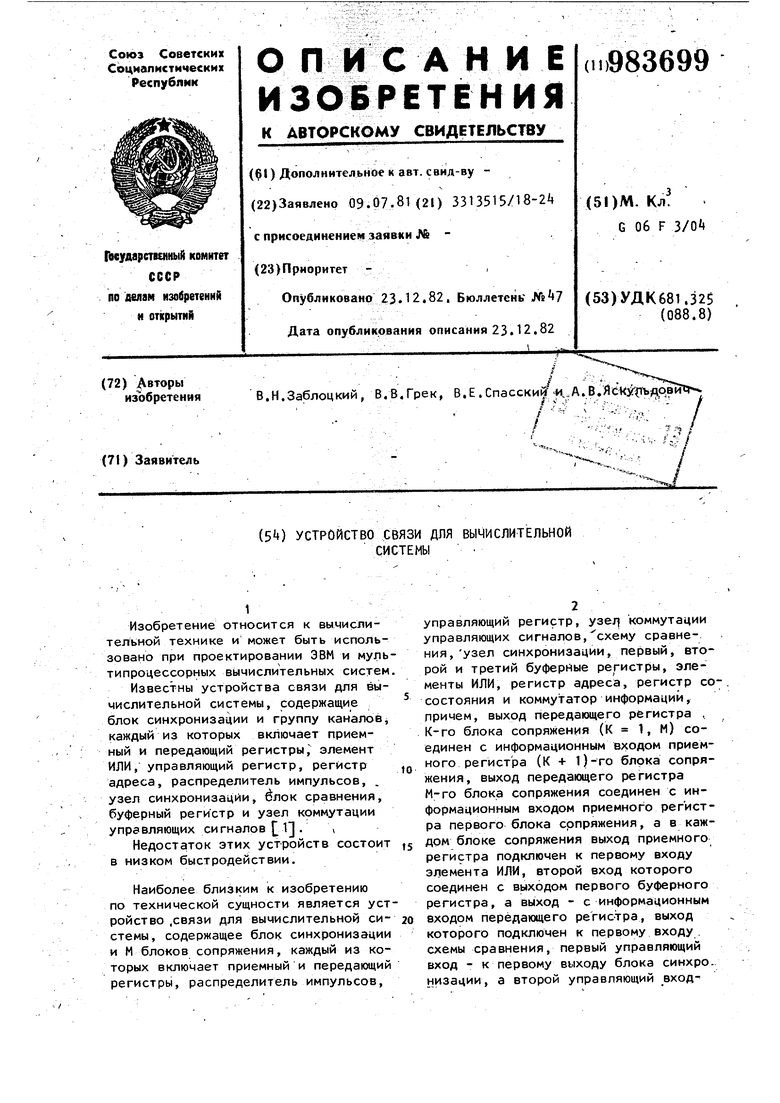

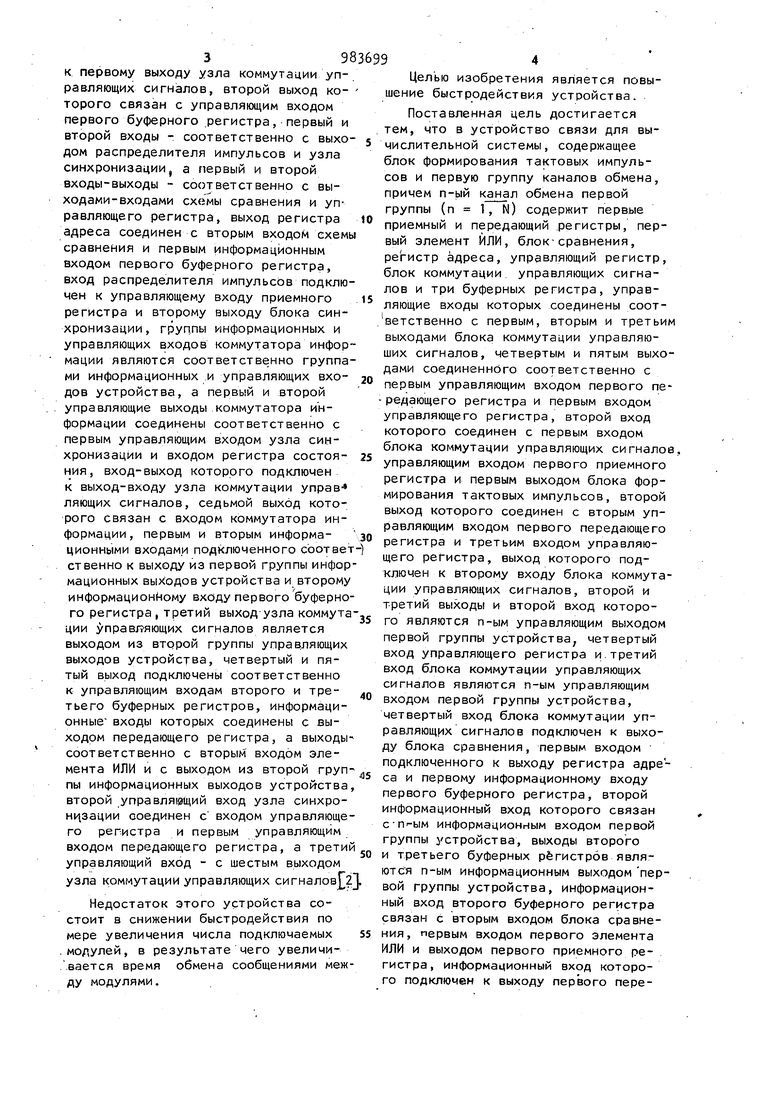

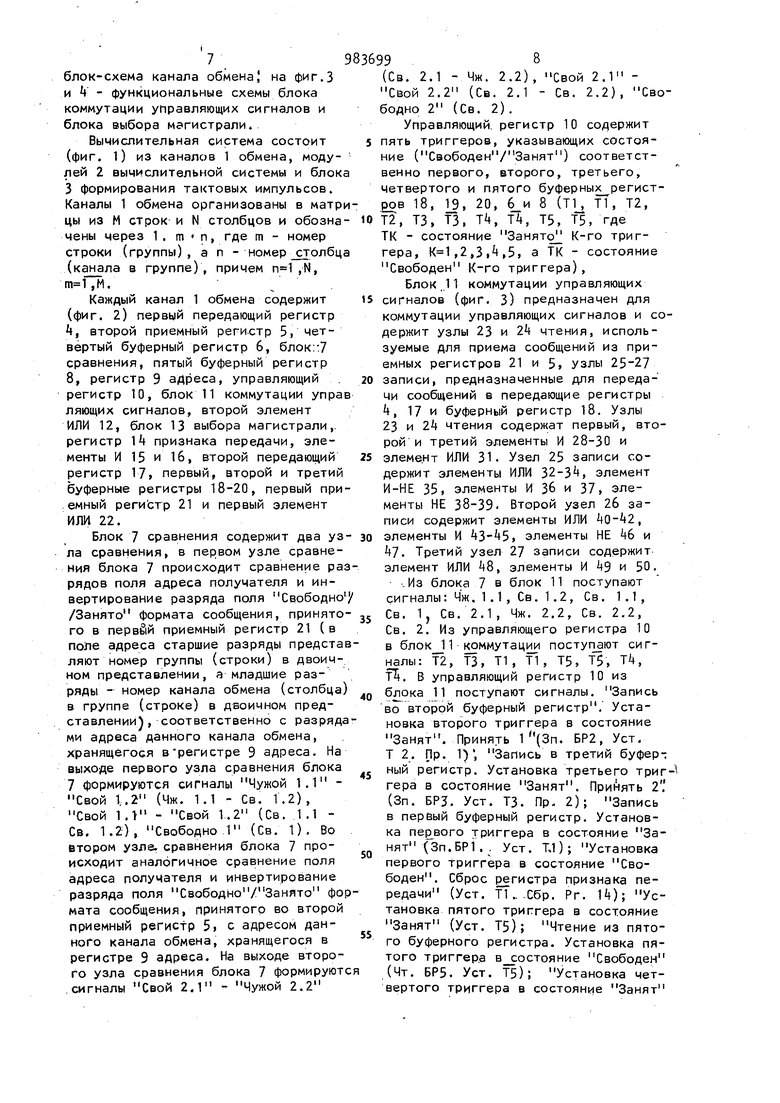

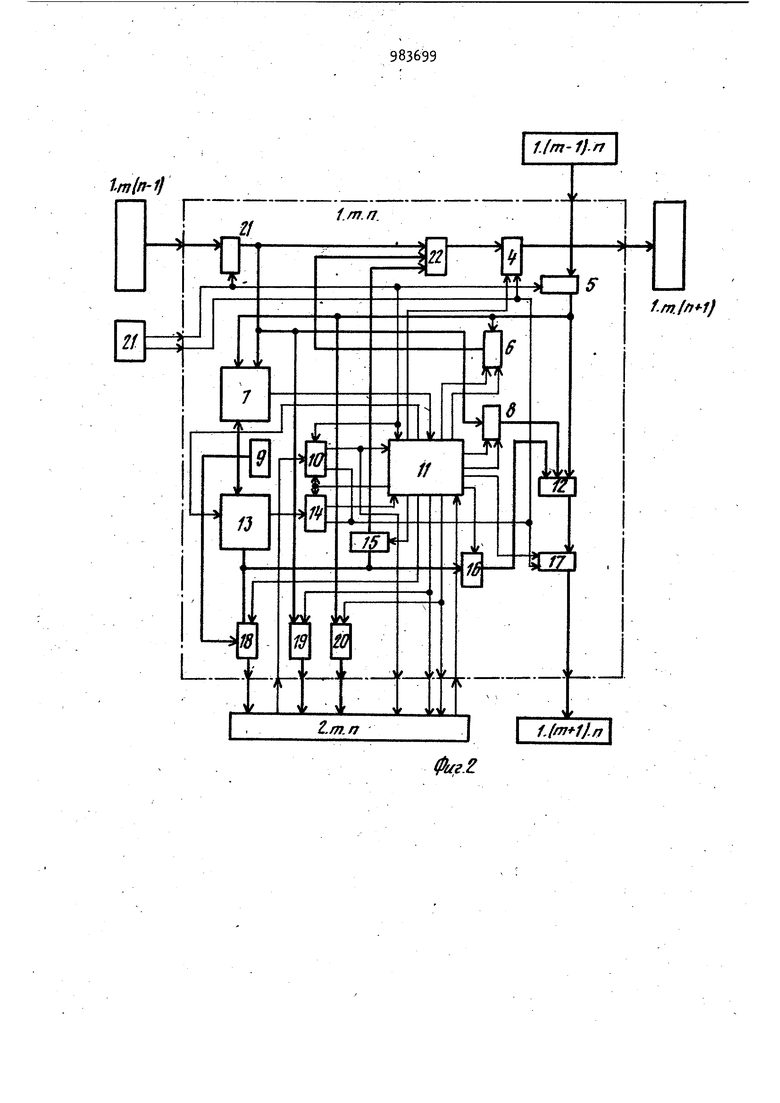

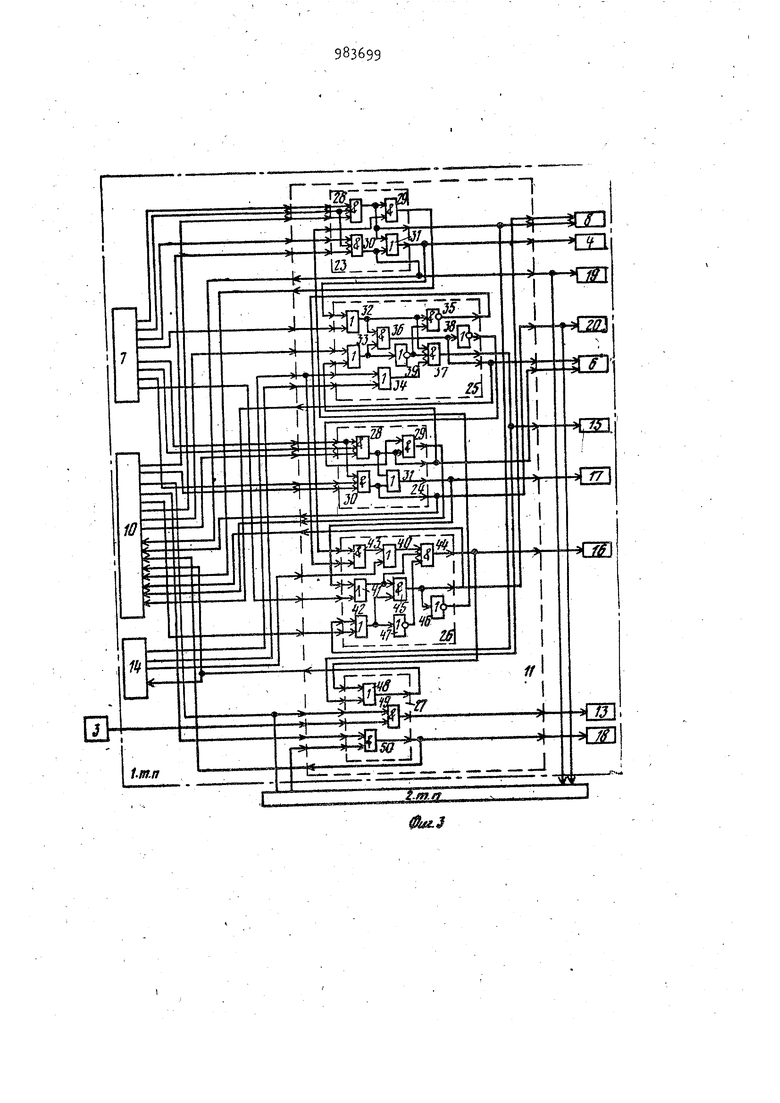

47. Третий узел 27 записи содержит элемент ИЛИ 48, элементы И 49 и 50. --Из блока 7 в блок 11 поступают сигналы: Чж. 1.1, Св. 1.2, Св. 1.1, 98 (Св. 2.1 - Чж. 2.2), Свой 2.1 2.2 (Св. 2.1 - Св. 2.2), Свободно 2 (Св. 2). Управляющий, регистр 10 содержит пять триггеров, указывающих состояние (Свободен / 3анят) соответственно первого, второго, третьего, четвертого и пятого буферных регистgoB 18, 19, 20, 8 (Т1, Т1, Т2, . - - . . Т2, ТЗ, ТЗ, Т4, Т4, Т5, fs, где ТК - состояние Занято К-го триггера, ,2,3,,5, а ТК - состояние Свободен К-го триггера) , коммутации управляющих сигналов (фиг. 3) предназначен для коммутации управляющих сигналов и содержит узлы 23 и 2k чтения, используемые для приема сообщений из приемных регистров 21 и 5, узлы 25-27 записи, предназначенные для передами сообщений в передающие регистры k, 17 и буферный регистр 18. Узлы 23 и 24 чтения содержат первый, второй и третий элементы И 28-30 и элеме.нт ИЛИ 31. Узел 25 записи содержит элементы ИЛИ 32-34, элемент И-НЕ 35, элементы И Зб и 37, элементы НЕ 38-39. Второй узел 2б записи содержит элементы ИЛИ 40-42, элементы И 43-45, элементы НЕ 46 и Св. 1j Св. 2.1, Чж. 2.2, Св. 2.2, Св. 2. Из управляющего регистра 10 в коммутации постугтают сигналы: Т2, ТЗ, Т1, Т1 , Т5, Т5, Т4, . В управляющий регистр 10 из блока 11 поступают сигналы. Запись во второй буферный регистр. Установка второго триггера в состояние Занят. Принять 1 (Зп. БР2, Уст. Т 2. Пр. 1), ;3апись в третий буферный регистр. Установка третьего триггера в состояние Занят. Принять 2. (Зп. БРЗ. Уст. ТЗ. Пр- 2); Запись в пербый буферный регистр. Установка перового триггера в состояние Занят (Зп.БР.. Уст. TJ); Установка первого Триггера в состояние Свободен. Сброс регистра признака передачи (Уст. Т1.. .Сбр. Рг. 14); Установка пятого триггера в состояние Занят (Уст. Т5); Чтение из пятого буферного регистра. Установка пятого триггера в состояние Свободен (Чт. БР5. Уст. Т5); Установка четвертого триггера в состояние Занят (УСТ. Т); Чтение из четвертого буферного регистра. Установка четве того триггера в состояние Свободен (Чт. BPk. Уст. Tit). Из регистра 1 признака передачи в блок 11 поступают сигналы: состоя ние Передать первого триггера (П.Т1); состояние Передать 1 вто рого триггера (п.1.Т2); состояние Передать 2 третьего триггера {П.2 ТЗ), В регистр 1Ц из блока 11 сигнал Установка первого триггера в состояние Свободен. Сброс регис ра признака передачи (Уст. Т1. Сбр. Рг. И). Из блока 3 в блок 11 поступает тактовый импульс СИ2. Из модуля 2 вычислительной системы в блок 11 поступает сигнал Запрос на передачу (З. пер.). Из блока 11 поступают сигналы: Чт. БР5. Уст.Т5. Запись в пятый буферный регистр. (Зп. БР5); Сброс первого передающего регистра (Сбр. Рг.); Зп.БР2. УСТ.Т2. Пр. 1; Зп. БРЗ. Уст. ТЗ. Пр.2; Чтение из четвертого буферного регистра. Установка четвертого триггера в состояние Свободен (Чт. БР4. Уст. Т1{), Запись в четвертый буферный регистр (Зп. БР); Чтение 1 из первого буферного регистра (Чт. 1, БР1); Сброс второго передающего регистра (Сбр, Рг.1 Чтение 2 из первого буферного регистра (Чт. 2. БР1); Опрос блока выбора магистрали (Опр. БВМ) Зп. БР1. УСТ.Т1. Блок 13 выбора магистрали предназначен для выбора либо первой магистрали, образованной первыми пр емными и передающими регистрами 21 и 4, либо второй магистрали, образо ванной вторыми приемными и передающ ми регистрами 5 и 17. Выбор мaгиctрали осуществляется на сравнении разрядов поля адреса получателя сообщения, принятого из модуля 2 вычислительной системы в буферный регистр 18 с разрядами адреса данного канала,обмена, хранящегося в регист ре 9. Блок 13 выбора магистрали ( фиг. ) содержит первую группу 51 и вторую группу 52 элементов сложения по модулю 2, элементы ИЛИ 53 и 5, элементы И , элементы НЕ 58 и 59. На первой группе 51 элементов сл жения по модулю 2 происходит сравне ние группы старших разрядов адресов 9910 на второй группе 52 элементов сложения по модулю 2 происходит сравнение группы младших разрядов адресов. Если старшие и младшие разряды не совпали, то по сигналу Опр. БВМ на выходе элементов И 55 формируется сигнал, по которому первый триггер регистра Н устанавливается в состояние Передать (П.Т.1). Если старшиеразряды совпали, а младшие нет, по сигналу Опр. БВМ на выходе элемента И 56 формируется сигнал, по которому второй триггер регистра И устанавливается в состояние Передать 1 (П.1,Т2). Если младшие разряды совпали, а старшие нет, по сигналу Опрос блока 13 выбора магистрали на выходе элемента И 57 формируется сигнал, по которому третий триггер регистра Н устанавливается в состояние Передать 2 .2.ТЗ). Регистр признака передачи содержит три триггера. Состояние П.Т1 означает, что адресуемый модуль 2 вычислительной системы не подключен к каналам 1 обмена, т.е. соо&цение из буферного регистра 18 необходимо передать либо в передающий регистр kf либо в передающий регистр 17. Состояние П,1.Т2 означает, что адресуемый модуль 2 подключен к одному из каналов обмена данной т-группы каналов обмена, т,е. сообщение из буферного регистра 18 необходимо перадать в передающий регистр Ц, Состояние П,2.ТЗ означает, что адресуемый модуль 2 подключен к одному из каналов 1 обмена одной из других групп, т.е. сообщения из буферного регистра 18 необходимо передать в передающий регистр 17. Блок 3 формирования тактовых импульсов содержит генератор тактовых импульсов и элемент задержки и предназначен для синхронизации работы устройства. В качестве модулей 2 вычислительной системы могут исполь зоваться процессоры, блоки памяти и т.д. Формат сообщения, передаваемого ежду каналами 1 обмена, содержит следующие поля: адрес получателя, дрес отправителя, признак занятоти сообщения (Свободно / 3анято); анные (адрес ячейки памяти, признак. Запрос / 0твет, признак Чтение / Запись, собственно данные). Устройство работает следующим бразом. В исходном состоянии все триггеры управляющих регистров 10 находят ся в состоянии Свободен, а тригге ры регистров 1 в нулевом состоянии. По пуску устройства регистр Н начинает вырабатывать серии тактовы импульсов СИ1 и СИ2 под управлением которых между каналами 1 начинают циркулировать инф1эрма14ионные сообще ния. Периоды повторения обеих серий одинаковы, но серия СИ2 сдвинута от носительно серии СИ1 на одну треть такта. По каждому тактовому импульс СИ1 сообщение из передающего регистра канала l.m.n передается в приемный регистр 21 канала 1.т.(п+1), а сообщение ий передающего регистра 17 канала 1,т.п. передается в приемный регистр 5 канала l.{m+l).n. По каждому тактовому импульсу СИ2 сообщение из приемных регистров 21 и 5 канала 1,га,п,передается соответ ственно в приемные регистры k и 17 данного канала l.m.n. Работу устройства рассмотрим на примере работы канала l.m.n. Работа остальных каналов обмена аналогична Работа канала 1,m.n. обмена осуществляется с помощью следующего набора основных операций: 1,Запись в четвертый буферный регистр 6 (Зп.БР). В буферный регистр 6 записывает ся сообщение иа приемного регистра 5, передающий регистр 17 обнуляется 2,Чте(ие из четвертого буферного регистра 6. Установка четвертого триггера в состояние Свободен (Чт, БР, Уст,П). Сообщение из буферного регистра 6 переписывается в передающий регистр , в следующем такте по сигна лу СИ1 четвертый триггер управляю. щего регистра 10 переходит в состояние Свободен (Т4). 3,Запись в пятый буферный регистр 8 (Зп,БР5) . В буферный регистр 8 записывается сообщение из приемного регистра 21, Передающий .регистр k обнуляется Ц Чтение из пятого буферного ре гистра 8, Установка пятого триггера в состояние Свободен (Чт. БР5, Уст,Т5). Сообщение из буферного регистра 8 переписывается в передающий регистр 17, в следующем такте по сигналу СИ1 пятыйтриггер управляюще ГО регистра 10 переходит в состояние Свободен (Т5). 5,Запись в первый буферный регистр 18, Установка первого триггера в состояние Занят (Зп.БР1, Уст,Т1). В буферный регистр 18 записывается сообщение ( адрес получателя, данные) из модуля 2.т.п., адрес отправителя из регистра 9 и разряд поля занятости сообщения устанавливается в единицу (Занято) в следующем такте по сигналу СИ1 первый триггер управляющего регистра 10 переходит в состояние Занят (Т1) ив модуль 2.т.п. посылается сигнал Запрос удовлетворен (З.уд,), по которому модуль 2,т.п. снимает сигнал З.пер, и сообщение со своего информационного выхода. 6,Чтение 1 из первого буферного регистра 18 (Чт.1.БР1) Сообщение из буферного .регистра 18 переписывается в передающий регистр k, в следующем такте по сигналу БИТ первый, второй и третий триггеры регистра 1 признака передачи сбрасываются, а первый триггер управляющего регистра 10 устатавливается в состояние Свободен (Т1). 7,Чтение 2 из первого буферного регистра 18 (Чт. 2,БР1) Сообщение из буферного регистра 18 переписывается в передающий регистр 17, в следующем такте по сигналу СИ1 первый, второй и третий триггеры регистра 14 признака передачи сбрасываются, а первый триггер управляющего регистра Q устана|и1ивается в состояние Свободен (Т1). 8,Запись во второй буферный регистр 19, Установка второго триггера в состояние Занят. Принять 1 (Зп. БР2, Уст,Т2, Пр,1). В буферный регистр 19 записыва- i ется сообщение из приемного регистра 21, в модуль 2,т.п. посылается сигнал Пр, 1, передающий регистр 4 обнуляется, в следующем такте по сигналу СИ1 второй триггер управляющего регистра 10 переходит в состояние Занят (Т2), 9,Запись в третий буферный регистр 20, Установка третьего триггера в состояние Занят, Принять 2 (Зп. БРЗ, Уст,ТЗ, ПрЛ). В буферний регистр 20 записывается сообщение из приемного регистра 5, в модуль 2.т.п. посылается сигнал Пр.2, передающий регистр 17 обнуляется, в следующем такте по сигналу СИ1 третий триггер управляющего регистра 10 переходит в состояние За нят (тз), 10. Сравнение адресов (Ср.Адр.), По приему сообщений в приемные регистры 21 и 5 (по сигналу СИ1) на узлах сравнения блока 7 происходит сравнение адресов получателей с адресом данного канала l.m.n. обмена. Каждый канал 1 обмена группы мож работать в четырех режимах Чтение Передача, Транзит, Запись. В начале/каждого такта работы устройства в каждом канале 1 производится операция Ср.Адр. Режим Чтение предназначен для приема сообщения, адресованного каналу l.m.n. обмена, и передачи его в модуль 2.т.п. вычислительной системы. Режим Чтение состоит из двух подрежимов: Чтение 1 и Чтение 2. Чтение 1. По сигналу Св. 1.1Св, 1,2 (означающему, что в приемный регистр 21 принято сообщение, адресованное каналу 1..т.п. обмена) и сигналу Т2 выполняется операция Зп.БР2.Уст.Т2.Пр,1. В следующем так те в приемный регистр 21 канала 1.m.(n+1) записывается нулевое сообщение из передающего регистра 4 канала l.m.n. (если в предыдущем такте в канале l.m.n. вместе с операцией Зп.Бр.2 Уст.Т2, Пр.1 не выполнялись операции Чт,1 Бр1 или Чт.БР.Уст.Т). Пр сигналу Пр.1 модуль 2.т.п. переписывает сообщение адрес отправителя, данные) из буфе ного регистра 19 на свои регистрь и формирует сигнал Принято 1.. По сигналу Принято 1 и сигналу СИ2 второй триггер управляющего регистра 10 переходит в состояние Свободен (Т2). Чтение 2. По сигналу Св.2.1 Св. 2.2 (означающему, что в приемный регистр 5 принято сообщение, ад ресо анноа каналу l.m.n.) и сигналу ТЗ выполняется операция Зп.БРЗ. Уст.ТЗ.Пр.2, В следующем такте в пр емный регистр 5 канала- 1.(m+1).n.. записывается нулевое сообщение из передающего регистра 17 канала l.m. (если в предыдущем такте в канале l.m.n. вместе с операцией Зп.БРЗ. Уст,ТЗ.Пр.1 не выполнялись опера91ции ЧТ.2.БР1 или Чт.БР.5.Уст.Т5). По сигналу Пр.2 модуль 2,т.п. переписывает сообщение (адрес отправителя, данные) из буферного регистра 20 на свои регистры и формирует сигнал Принято 2. По сигналу Принято 2 и сигналу СИ2 третий триггер управляющего регистра 10 переходит в состояние Свободен (ТЗ). Режим Передача предназначен для приема сообщений, поступающих на приемные регистры 21 и 5/и передачи их соответственно на выходы пеРйдающих регистров 4 и 17. Режим Передача состоит из двух подрежимов: Передача 1 и Передача 2. Передача 1. Если не выполняются операции Зп.БР2.Уст.Т2.Пр.1J Зп. БР5.Чт.1.Бр1 и Чт. Уст.Т , сообдцение, принятое по сигналу СИ1 в приемный регистр 21 и переданное по сигналу СИ2 в передающий регистр 4 канала l.m.n., в следующем такте без изменений по сигналу СИ1 переписывается в приемный piaгиcтp 21 канала 1.т.(п+1). Передача 2. Если не выполняются операции Зп.БРЗ.Уст.ТЗ.Пр.2, Зп. БР4.ЧТ.2.БР1 и Чт.БР5.Уст.Т5, сообщение, принятое по сигналу СИ1 в приемный регистр 5 и переданное по сигналу СИ2 в передающий регистр 17 канала l.m.n., в следующем такте без изменений по сигналу СИ1 переписывается в приемный регистр 5 канала 1,(т+1).п обмена. Режим Транзит предназначен для приема сообщений, поступающих на первый и второй приемные регистры 21 и 5 и передачи их соответственно с выходов второго и первого переданщих регистров 17 и 4. Режим Транзит состоит из двух подрежимов: Транзит 1 и Транзит 2. Транзит 1. По сигналу Чж. 1.1 Св. 1.2 (означащему, что в приемный регистр 21 принято сообщение, адресованное модулю 2, подключенному к . одному из п-х каналов 1 обмена Других .групп) и сигналу Т5 выполняется операция Зп.БРБ. Если есть сигнал Св.2 или сигнал Сбр.Рг.17, по сигналу Зп.БРЗ выполняется операция Чт,БР5.Уст.Т5. Если сигналы Св. 2 и Сбр.Рг.17 отсутствуют, формируется сигнал Уст.ТБ, по которому в следуюш,ем такте с приходом сигнала СИ1 пятый триггер управляющего регистpa 10 переходит в состояние Занят (Т5)I а в приемный регистр 21 канала l.m.(n+l) обмена переписывается нулевое хообщение из передающего регистра k канала l.m.n. обмена (еели в последнем в предыдущем такте вместе с операцией Зп.БР5 одноврейенно не выполнялись операции Чт.1 . БР1 или Чт.БР.Уст.Т ). По сигналу Т5, если есть сигналы Св.2 или Сбр.Рг.17 выполняется операция Чт.БР5.Уст.Т5. Транзит 2. По сигналу Св.2.1 Чж.2.2 (означающему,, что в Приемный регистр 5 принято сообщение, ад ресованное модулю 2,. подключенному к одному из каналов 1 обмена данной ттой группы) и сигналу выполняется операция Зп.БР. Если есть сиг нал Св.1 или сигнал Сбр.Рг., по сигналу Зп.БР выполняется операция Чт.БР,Уст.Т4. Если сигналы Св.1 и Сбр.Рг.4 отсутствуют,формируется сигнал Уст.Т4, по которому в следую щем такте с приходом сигнала СИ1 четвертый триггер управляющего регистра 10 переходит в состояние Занят (Т), а в приемный регистр 5 канала 1.(m+l).n. обмена переписы вается нулевое сообщение из передающего регистра 17 канала l.m.n, обмена (если в последнем в предыдуiщем такте вместе с операцией Зп.БР одновременно не выполнялись операци Чт.2. БР1 или Чт,БР5.Уст.Т5;. По сигналу Т4, если есть сигналы Св.1 или Сбр,Рг,А, выполняется операция Чт.БР. Уст.Т. Режим Запись предназначен для приема сообщения из модуля 2.т.п. в канал l.m.n. обмена и передачи егс с выходов первого либо второго передающих регистров 4 и 17. Когда модулю 2.т.п. необходимо пе редать сообщение, он посылает сигнал З.пер., поступающий на вход блока .1 и выставляет сообщение на своем информационном выходе. По сигналу З.пе и сигналу Т1 выполняется операция Зп.БРТ. Уст.Т1. По сигналу СИ2 и си налу Т1 формируется сигнал Опр. БВМ по которому.в зависимости от резуль тата сравнения адресов в блоке 13 устанавливается один из триггеров регистра И признака передачи. Если не выполняется операция Чт.БР4, Уст ТТГ, но есть сигналы Св.1 или Сбр, сигналу ПЛ1 или сигналу П;1.Т2 выполняется операция Чт.1,БР выполняется операция Чт.БР5. Уст.Т5, но есть сигналы Св.2 или Сбр.Рг.17, по сигналу П,2.ТЗ или сигналу П.Т1 (в отсутствии операции ЧТ.1.БР1) выполняется операция .Чт.2. БР,1 . Таким образом, предлагаемое уст,ройство обладает более высоким быстродействием, чем известное,обеспечивая обмен, сообщениями между модулями вычислительной системы по бо-лее коротким путям. Формула изобретения 1, Устройство связи для вычислительной системы, содержащее блок формирования тактовых импульсов и первую группу каналов обмена, причем п-ый канал обмена первой группы (,N) содержит первые приемный и передающий регистры, первый элемент ИЛИ, блок сравнения, регистр адреса, управляющий регистр, блок коммутации управляющих сигналов и три буферных регистра, управляющие входы которых соединены соответственно с первым, вторым и третьим выходами блока коммутации управляющих сигналов, четвертым и пятым выходами соединенного соответственно с первым управляющим входом первого передающего регистра и первым входом управляющего регистра, второй вход которого соединен с первым входом блока коммутации управляющих сигналов, управляющим входом первого приемного регистра и первым выходом блока формирования тактовых импульсов, второй выход которого соединен с вторым управляющим входом перёого передающего регистра и третьим-входом управляющего регистра, выход которого подключен к второму входу блока коммутации управляющих.-сигналов, второй и третий выходы и втор1ой вход которого являются 1Г-ЫМ управляющим выходом первой . группы устройства, четвертый вход управляющего регистра и дретий вход блока коммутации управляющих сигналов являются п-ым управляющим входом первой группы устройства, четвертый вход блока коммутации управляющих сигналов подключен к выходу блика сравнения, первым входом подключенного к выходу реги стра адреса и первому информационному входу первого буферного региатра, второй информационный вход которого связан с п-ым информационным входом первой группы устройства выходы второго и третье го буферных регистрсзв являются п-ым информационным выходом первой группы устройства, информационный вход второго буферного регистра связан с вторым входом блока сравнения, пе вым входом первого элемента ИЛИ и выходом первого приемного регистра, информационный вход которого подклю чен к выходу первого передающего ре гистра (n-l)-ro канала обмена первой группы, информационный вход пер го передающего регистра соединен с выходом первого элемента ИЛИ, выход первого передающего регистра N-ro канала обмена первой группы соедине с информационным входом первого при емного регистра первого канала обмена первой группы, отличаю щееся тем, что, с целью повышения быстродействия устройства, в него введены М-1 группа каналов обмена по N каналов в каждой группе, а в каждый канал обмена введены вторые приемные и передающий регистры, второй элемент ИЛИ, четвертый и пятый буферные регистры, первый и второй элементы И, блок выбора магистрали и регистр признака передачи, в п-ом канале т-ой группы () первый и второй входы регистра-признака передачи соединены со ответственно с первым и третьим входами управляющего.регистра, а третий вход - с выходом блока выбора магистрали, управляющий вход которого связан с шестым выходом блока коммутации управляющих сигналов, пятым входом соединенного с выходом регистра признака передачи, а седьмым и восьмым выходами - соответственно с управляющими входами , первого и второго элементов И, информационные входы которых подключены к информационному выходу первого буферного регистра и первому информационному входу блока выбора магистраЛИ, вторым информационным входом свя занного с информационным выходом регистра адреса, информационные выходы первого и второго элементов И сое ДИН9НЫ соответственно с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, третий вход первого элемента ИЛИ и второй вход второго элемента ИЛИ соединены соответственно с выходами четвертого и пятого буферных регист ров, первые и вторые управляющие входы которых подключены соответственно к девятому - двенадцатому выходам блока коммутации управляющих сигналов, тринадцатый выход которого соединен с первым управляющим входом второго передающего регистра, вторым управляющим входом связанного с вторым управляющим входом первого передающего регистра, а выходом - с информационным входом второго приемного регистра п-го канала обмена (т+1)-ой группы, информационный вход второго приемного регистра п-го канала обмена т-ой группы подключен к выходу второго передающего регистра п-го канала обмена (т-1)-ой группы, информационный .вход второго приемного регистра пто канала обмена первой группы соединен с выходом второго передающего регистра п-го канала обмена М-ой группы, в каждом канале обмена управляющий вход второго приемного регистра .соединен с управляющим входом первого приемного регистра, выход которого подключен к информационному входу пятого буферного регистра, выход второго элемента ИЛИ связан с информационным входом второго передающего регистра, а третий вход - с выходом второго приемного регистра, информационными входами третьего и четвертого буферных регистров и третьим входом блока сравнения, второй информационный вход первого буферного регистра, выходы второго и третьего буферных регистров, второй вход и второй и третий выходы блока коммутации управляющих сигналов, третий вход блока коммутации управляющих сигналов и четвертый вход управляющего регистра п-го канала т-ой группы являются соответственно п-ми информационными входом и выходом,- п-ми управляющими выходом и входом т-ой группы устройства, 2. Устройство по п. 1, о т л и чающееся тем, что блок выбора магистрали содержит две группы элементов сложения по модулю два, два элемента ИЛИ, два элемента НЕ и три элемента И, причем выходы элемейтов И подключены к вЬ1ходу блока, а первые входы - к управляющему ду Олока, первый и второй информационные входы которого связаны соответственно с первыми и вторыми 19 9 входами первой и второй групп элементов сложения по модулю два, выходы которых подключены соответственно к группам входом первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с вторыми входами первого и второго элементов И и через первый элемент НЕ - с вторым входом третьего элемента И, третий вход которого соединен с третьим входом первого элемента И и выходом второго элемента ИЛИ и через второй элемент НЕ - с третьим входом второго элемента И. Источники информации принятые во внимание при экспертизе 1,Авторское свидетельство СССР № кл. G об F з/О, 1978. 2,Авторское свидетельство СССР № 802957, кл. G 06 F З/О, 1979 (прототип),l.m.rj.

Й

f

и

J S

/

1.{m-1).rt IЛ

4-

czi i

f.m.)

Ш

//

jKS

Сш

/J

L.Jl.

1Ls

Z.fn.fj

/jfV

A

J I /Y/ ///y|

%.f

лг