ы

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Многоканальное устройство связи для вычислительной системы | 1982 |

|

SU1083174A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

Изобретение относится к области вычислительной техники и может быть использовано при проектировании электронных вычислительных машин (ЭВМ) и мультипроцессорных вычислительных систем. Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности селекторного обмена между каналами связи. Поставленная цель достигается тем, что устройство содержит канал свчзи 1, коммутатор управляющих сигналов 2, блок синхронизации 3. модули 4, элемент ИЛИ

О

го

Изобретение относится к вычислительной технике и может быть использовано при проектировании электронных вычислительных машин (ЭВМ) и мультипроцессорных вычислительных систем.

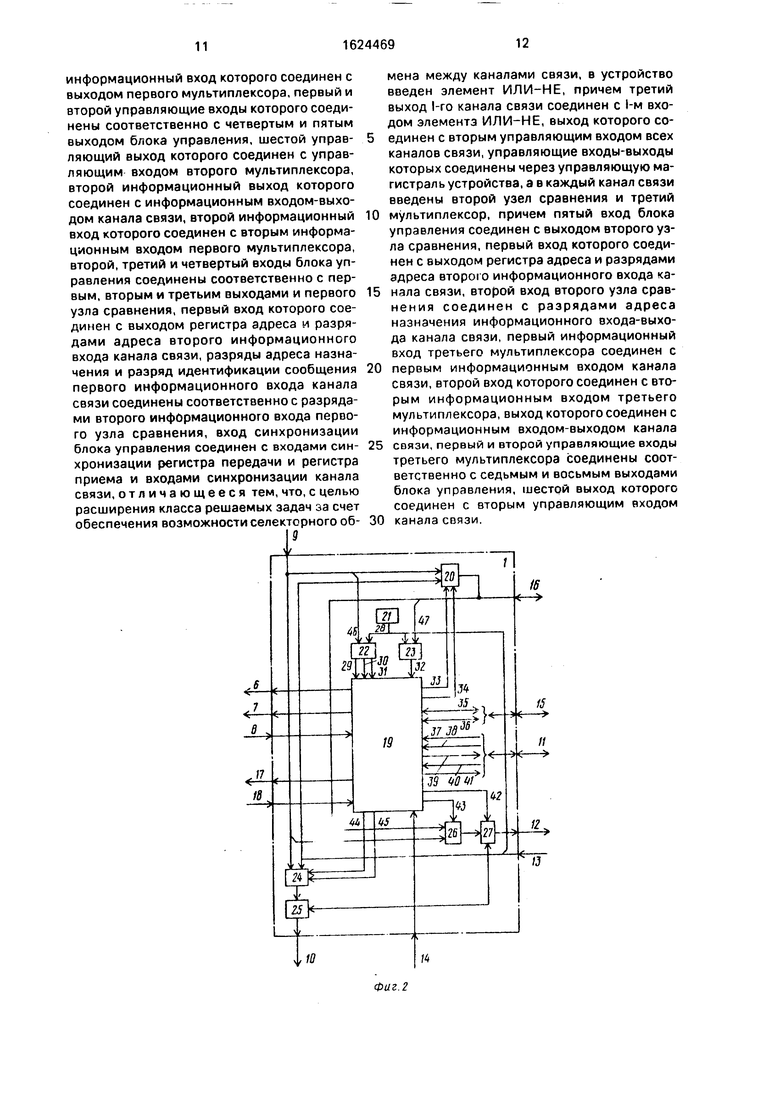

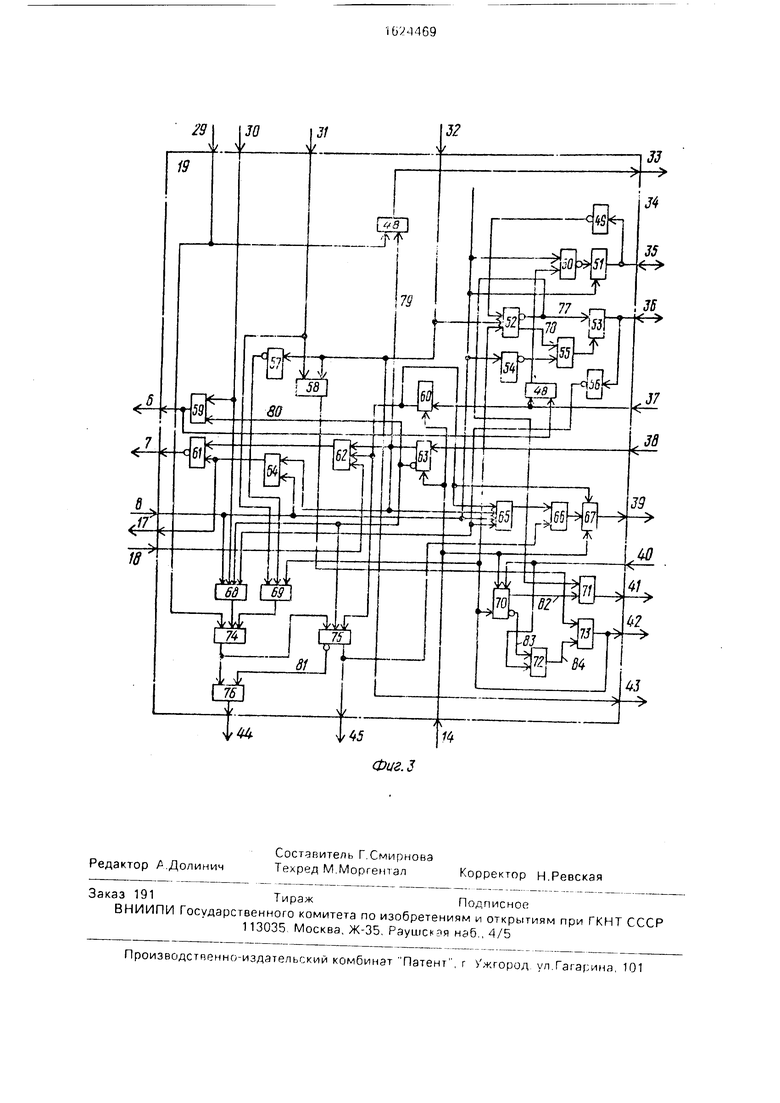

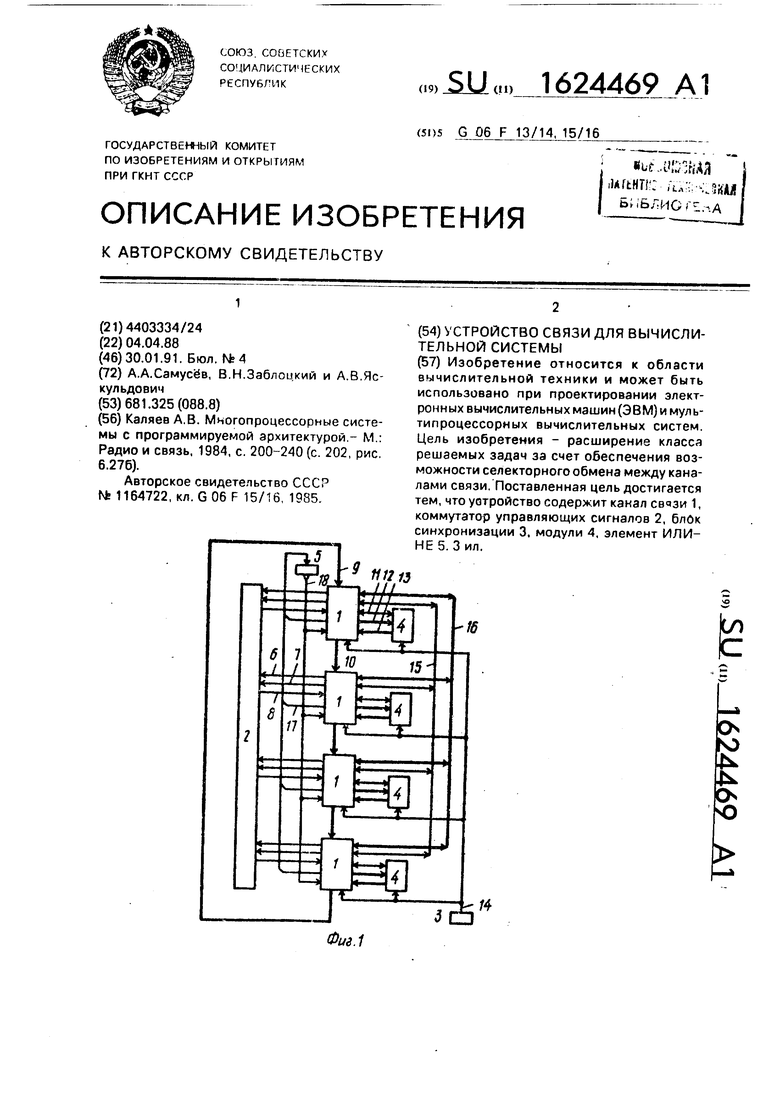

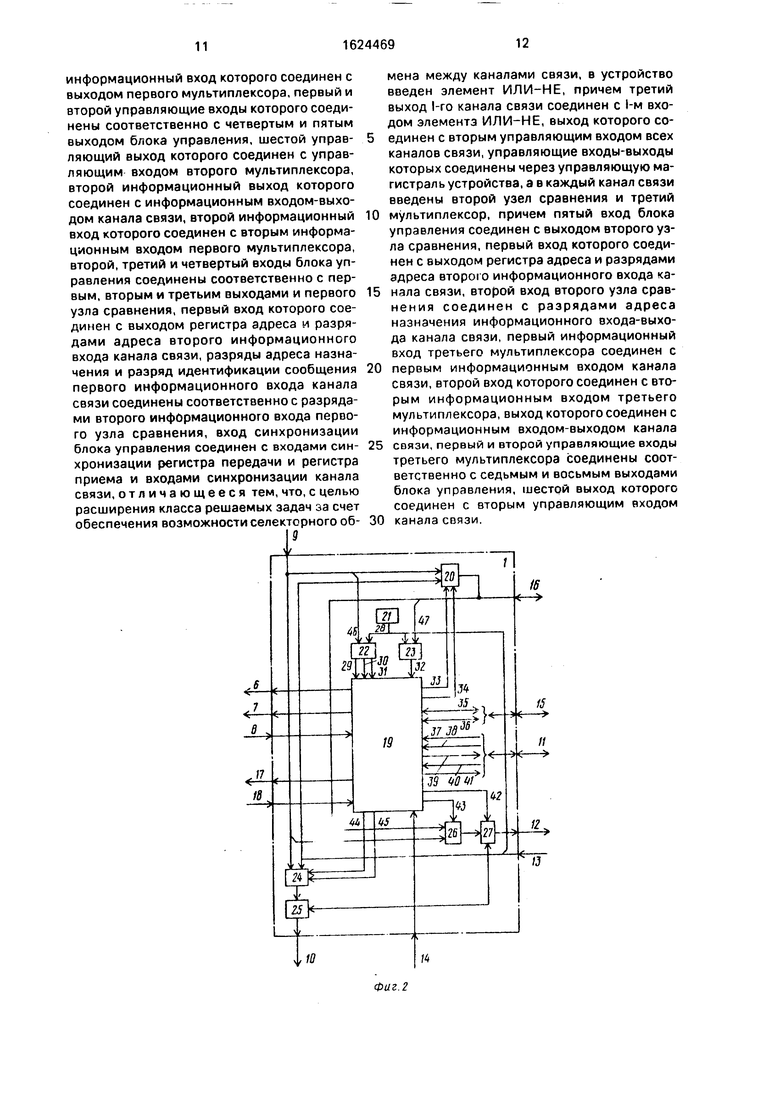

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности селекторного обмена между каналами связи. На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема канала связи; на фиг.З - функциональная схема блока управления.

Устройство (фиг.1) содержит канал 1. коммутатор 2 управляющих сигналов, блок 3 синхронизации, модули 4, элемент ИЛИ- НЕ 5, первый выход 6 1-го канала, второй выход 7 1-го канала, первый управляющий вход 81-го канала, первый информационный вход 9 канала 1, первый информационный выход 10 канала, входы 11.запроса на передачу и подтверждение приема (выходы признака передачи и удовлетворения запроса) 1-го канала, второй информационный выход 12 1-го канала, второй информационный вход 13 1-го канала, выход 14 блока синхронизации, управляющая магистраль устройства 15, информационная магистраль устройства 16, третий выход 17 канала, выход 18 элемента ИЛИ-НЕ.

Канал 1 (фиг.2) содержит блок 19 управления, первый мультиплексор20, регистр21 адреса, первый узел 22 сравнения, второй узел 23 сравнения, второй мультиплексор 24, регистр 25 передачи,третий мультиплексор 26, регистр 27 приема, выход 28 регист- Р. 21, выходы 29-31 узла 22, выход 32 узла 3, выход 33 блока 19, выход 34 блока 19, разрядные 35-36 управляющей магистрали, выходы шины 37, 38 запроса на передачу блока 19 в выход 39 - удовлетворения запроса блока 19 во вход 40 подтверждения приема блока 19, выход 41 признака передачи блока 19, выходы 42-45 блока 19, второй вход 46 узла 22, выход 47 узла 23.

Блок 19 управлзния канала (фиг.З) содержит первый элемент ИЛИ 48, первый элемент НЕ 49, первый элемент И-НЕ 50, первый буферный элемент 51, первый элемент И 52, второй буферный элемент 53, второй элемент НЕ 54, второй элемент И 55, третий элемент НЕ 56, четвертый элемент НЕ 57, второй элемент ИЛИ 58, третий элемент И 59, первый триггер 60, первый элемент ИЛИ-НЕ 61, четвертый элемент И 62, второй триггер 63, пятый элемент И 64, шестой элемент И 65, третий элемент ИЛИ 66, третий триггер 67, седьмой элемент И 68, восьмой элемент И 69, четвертый триггер 70, девятый элемент И 71, четвертый элемент ИЛИ 72, десятый элемент И 73,пятый элемент ИЛИ 74, одинадцатый элемент 75, двенадцатый элемент И 76, информационный вход 77 триггера 53, прямой выход 78 элемента И 52, прямой выход 79 триггера 63,

инверсный выход 80 триггера 63, инверсный выход 81 элемента 75, прямой выход 82 триггера 70, инверсный выход 83 триггера 70, выход 84 элемента ИЛИ 72.

Устройство функционирует следующим

0 образом.

В исходном состоянии в разряд идентификации сообщений всех регистров 25 заносится лог. О, а триггеры 60, 63, 67 и 70 переводятся в нулевое состояние (когда на

5 прямых выходах триггеров устанавливается лог. О путем подачи импульса сброса по цепям сброса. Затем включается блок 3 синхронизации и на выходе 14 периодически появляются импульсы синхронизации, фор0 мируя такты функционирования устройства. Под тактом функционирования устройства в данном случае понимается промежуток времени между моментами окончания (заднего фронта) двух соседних импульсов синхрони5 зации на входе 14. В качестве модулей 4

могут быть блоки обработки (процессоры),

блоки памяти, устройства внешней памяти.

Вычислительная задача (программа)

большого объема заранее (в процессе ком0 пиляции, редактирования и загрузки) разбивается на большое количество участков (блоков), которые допускают параллельную их обработку в процессорах. Эти программные блоки (части программы и

5 данные, подлежащие обработке) заранее распределяются по процессорам, однако часть их загружается в блоки памяти, а та их часть, которая не помещается в блоках памяти, запоминается во внешней памяти.

0 Между программными блоками в процессе их параллельной обработки возможен обмен отдельными сообщениями (промежуточными или конечными результатами обработки данных, который осуществляется

5 через кольцевую сеть связи (кольцо) путем установки в любом такте на выходах 37, 38 любого канала 1 запроса с кодом 10. При этом на входе 13 устанавливается сообщение, которое содержит поле адреса назна0 чения и информационное поле. Если в канале 1 имеются условия для передачи сообщения в кольцо, то в следующем такте в регистр 25 записывается сообщение со входа 13 вместе с кодом адреса передатчика на

5 выходе 21 и кодом идентификации сообщения. Таким образом, сообщение в регистре 25 содержит поле адреса назначения, поле адреса (номер) передатчика, поле информации и поле (бит) идентификации сообщения. Сообщения, запомненные в регистрах

25 передаются на вход 9 следующего канала 1, в котором оно может быть передано (и запомнено) или в регистр 27 (если оно адресовано модулю, подключенному к каналу 1), или в регистр 25, или передано в шину 16 (см. описание канала 1). В каждом новом такте сообщение будет следовательно передаваться из регистра 25 предыдущего канала в регистр 25 последующего канала 1 по кольцу до тех пор, пока оно не достигнет канала 1 с адресуемым модулем 4 и не будет принято в регистр 27 или передано через шину 16 в регистр 27 канала, подключенного к адресуемому модулю.

В случае, если сообщение со входа 9 1-го канала 1 принимается в регистр 27 любого канала 1, то в регистр 25 может быть принято новое сообщение со входа 12 1-го канала 1, если имеется запрос с кодом 10 rta входах

37, 38 1-го канала 1, где I 0, 1(т-1) и

необходимые условия для передачи сообщения в кольцо.

Если запрос на передачу сообщения кольцо в модуле 1 нет, который продолжает циркулировать по кольцу как и сообщение, однако на каналах 1 не воспринимает как сообщение.

Для того, чтобы сообщение в любом 1-ом канале 1 было передано со входа 9 в шину 16 необходимо, чтобы на выходе 7 (фиг.1) всех каналов 1 была установлена лог. 1, на выходе 7 1-го канала была установлена лог. 1, а на выходе всех каналов 1 с номерами большими I был установлен лог. О. В этом случае на выходе коммутатора 2 (см. описа ние коммутатора 2) устанавливается лог. 1, под управлением которой на выходе 34 блока 19 1-го канала устанавливается лог. 1 и сообщение со входа 9 передается на шину 16, а на разрядной шине 35 шины управления 15 устанавливается лог. О, гак как элемент 51 разблокируется, а на входах элемента И 50 блока 19 устанавливаются две лог. 1 (со входа 8 и входа 30), которые переводят в нулевое состояние выход элемента И 50. Для того, чтобы сообщение из шины 16 было передано (и запомнено) в регистре 27 канала 1, подклчюенного к адресному модулю 4, необходимо, чтобы в этом канале лог. 1 со входа 32 блока 19 через элемент ИЛИ 58 и И 73 установилась на входе элемента 52, под управлением которой на выходе 77 элемента 52 устанавливается лог, О, а на выходе 78 - лог. 1 (так как на выходе элемента 49 и входе 32 установлены лог. Г). На выходе элемента 55 устанавливается лог. 1, так как на выходе элемента 54 установлена лог. 1. В результате на разрядной шине 36 управляющей шины 15 устанавливается лог. О, который

с помощью элемента Н Е 56 уже 1-го (передающего, а не принимающего) канал 1 устанавливается на входе элемента И 68 лог. 1. на остальных входах элемента И 68 уже ус- 5 тановлены лог. Г. В результате на первом входе элемента И 76 устанавливается лог. 1. Если в 1-ом канале не предусмотрена передача сообщения из модуля 4 в кольцо, то на втором входе 81 элемента И 76 также

10 установлена лог. 1 (так как на выходе триггера 60 установлен лог. О). В итоге на выходе 44 формируется лог. 1, обеспечивающая запись в регистр 25 1-го канала 1 пустого кода. Если же запрос на передачу

5 сообщения (со йхода 13) в кольцо в i-ом канале есть (в триггере 60 хранится лог. 1, а в триггере 63 лог. О), то на выходе 81 элемента И 75 устанавливается лог. О и на выходе 44 формируется лог. О, обеспечи0 вающий действительность сообщения, запоминаемого в регистре 25 (со входов 13, 28). Передача сообщения со входов 13, 28 на выход мультиплексора 24 обеспечивается благодаря установке на выходе 45 блока 19

5 1-го канала лог. 1.

При этом на выходах элементов 51, 53 блоков 19 всех остальных каналов 1 устанавливается высокоимпедансное (третье) состояние.

0Следует отметить, что в канале 1, принявшем сообщение в регистр 27, возможны два режима приема сообщения: режим приема сообщения в модуль 4 (когда на входе

40установлена лог. 1 при любом состоя- 5 нии триггера 70) и режим снятия сообщений

из кольца (когда на входе 40 установлен лог. О, а триггер 70 находится в нулевом состоянии). В первом случае, если триггер 0 находится в единичном состоянии в начале

0 такт а передачи сообщения через общую шину 16, на выходе 41 установлена лог. О. Когдп на выходе 77 элемента 52 принимающего канала 1 устанавливается лог. О, на выходе 41 устанавливается (до действия им5 пульса синхронизации) лог. О, информирующий модуль 4 о приеме в регистр 27 нового сообщения (после действия очередного импульса синхронизации). После деист вия очередного импульса синхронизации в триг0 гере 70 подтвердится единичное состояние, на входе 32 и 77 установятся соответственно лог. О и лог. 1. В результате на выходе

41вновь установится лог. 1. Если в (первом случае) триггер 70 находился в нулевом

5 состоянии, то на выходе 41 устанавливается лог. 1. После действия очередного импульса синхронизации сообщение из шины 16 запоминается в регистр 27, триггер 70 переводится в единичное состояние и на выходе 41 устанавливается единичное состояние.

информирующее модуль А, что сообщение в регистр 27 принято.

Во втором случае (когда на входе 40 и выходе 41 установлены лог. О) после действия импульса синхронизации сообщение из шины 16 запоминается в регистр 27, однако триггер 70 не изменяет своего нулевого состояния и на выходе 41 сохраняется тог. О.

Аналогичные режимы приема предусмотрены в каждом канале 1 и при приеме сообщений со входа 9. При этом на выходах 17 всзх каналов 1 установлен лог. О, а на выходе и входах 18 - лог. 1.

В тех случаях, когда модули-процессоры выполняют программные блоки, которыми они были загружены, они запрашивают новые программные блоки, которые хранятся в блоках (модулях) памяти или во внешней памяти, путем передачи соответствующих сообщений в кольцо. Когда модули 4 памяти готовы для передачи программных блоков (представляемые в виде массива сообщений) они в любом такте выставляют на входах 37, 38 код 11. Возможны также случаи, когда в результате обработки в процессорах программных модулей формируются массивы данных, подлежащих дальнейшей обработке в других процессорах. В этом случае массив дчнных формируется в виде мас- сива сообщений в модуль-процессор перэлатчик устанавливается в любом такте на входах 37, 38 запрос в виде кода 11. В следующем такте лог. 1 со входов 37, 38 запоминаются в триггерах 60, 63 и на выходе 7 любого 1-го канала 1 устанавливается лог. О, на выходе 6 1-го канала 1 удерживается лог. О. На входе 8 1-го канала 1 формируется лог. 1 только в том случае, если на выходе 7 всех каналов с номерами большими I установлена лог. 1. Сигналы на выходе 6 каналов 1 не влияют на формирование сигналов на выходе 8. В результате на выходе элемента И 64, на выходе 17 1-го канала устанавливается лог. 1, а на выходе элемента ИЛИ-НЕ 5 - лог. О, который устанавливает на выходе хэлементз l/l 62 блока 19 всех каналов 1 лог. О, обеспечивая удержание лог. 1 на выходе 7 всех каналов 1, кроме 1-го до тех пор (в течение такого количества тактов), пока на входах 37, 38 1-го канала 1 удерживается код 11, который в каждом такте подтверждает единичное состояние 60 и 63.

Код на входах 37, 38 может удерживаться до тех пор, пока не будет установлена связь с адресуемым модулем через любой канал и не будет передан весь массив сообщений адресуемому модулю через шину 16. При этом любой запрос на общую шину в

любой другой канал 1 не будет удовлетворяться, т.е. не будет нарушать установленную связь. При этом в 1-ом канале 1 на выходах 33, 34 блока 19 установи/тся код 11.

под действием которого код со входов 13,28 подается на шину 16, на выходе элемента 50 установится лог, О, который передается на шину 35. В принимающем канале 1 (связанным с адресуемым модулем) на выходе эле0 мента НЕ 49 и выходе 32 устанавливаются лог. 1. Если регистр 27 принимающего канала 1 занят, то на выходе 41 и 42 установлены соответственно лог. 1 и лог. О. В результате состояние выходов элемента И

5 52 не изменяются и на шине 36 сохраняется высокоимпедансное состояние, которое воспринимается элементом НЕ 56 узла 19 передающего канала 1 как лог, 1. В результате на выходе элемента НЕ 56 передающе0 го канала 1 установится лог. О, который заблокирует элемент И 65. Так как на выходе 45 блока 19 передающего канала 1 установлен лог. О, то после действия очередного импульса синхронизации в ре5 гистр 67 будет записан лог. О, который установится на выходе 39, информирующий модуль 4, что связь не установлена и сообщение со входа 13 не принято в регистр 27 адресуемого канала 1. В этом случае запрос

0 с кодом 11 на входе 37, 38 передающего канала может сохраняться до тех пор, пока на выходе 42 принимающего канала не появится лог. 1 (при установке на входе 40 лог. 1, означающей, что модуль 4 готов прини5 мать сообщения и что регистр 27 свободен). В этом случае на выходах 77, 78 элемента 52 блока 19 принимающего канала установится код соответственно 0/,1. На шине 36 установится лог. О. На выходе 41 установится

0 лог. О, информирующий модуль 4, что в регистр 27 будет передано новое сообщение.

На входе элемента НЕ 56 блока 19 передающего канала 1 устанавливается лог. 1.

5 В результате на выходе элемента И 65 и ИЛИ 66 устанавливается лог. 1, которая после действия очередного импульса синхронизации запоминается в регистр 67 и устанавливается на входе 39. информируя

0 модуль 4 о том, что сообщение с общей шины 16 (с выходов 13, 28 передающего канала 1) принято в регистр 27 принимающего канала 1. В этом случае сразу же после импульса синхронизации на выходе 14, на

5 входе 13 передающего канала устанавливается новое сообщение из массива сообщений которые необходимо передать, а на входе 37 устанавливается лог. О на время, пока на шине 35 установится лог. 1, на выходе элемента НЕ 49 блока 19 принимающего канала установится лог. О, на выходе 77 и выходе 41 установиться лог, 1, информирующая, что в регистр 27 принимающего канала 1 будет записано новое сообщение. Затем до появления очередного импульса синхронизации на вход 37 вновь устанавливается лог. 1, также и на выходе 41 вновь устанавливается лог. 1, при этом в регистр 27 принимающего канала 1 записывается очередное сообщение с шины 16, так как на выходе 42 и 43 блока 19 устанавливается лог, 1. В следующих тактах действия по установке кодов на входе 13 и 37 передающего канала повторяются до тех пор, пока через общую шину 16 будут переданы все сообщения массива. При этом на выходах элементов 51, 53 блоков 19 и на выходе мультиплексоров 20 всех остальных каналов 1 (не участвующих в обмене сообщениями через общую шину) всегда устанавливается высокоимпеданс- ное (третье) состояние.

После передачи последнего сообщения массива данных перед появлением очередного импульса синхронизации на выходе 14 на входах 37, 38 передающего канала устанавливается лог. О. После действия очередного импульса синхронизации в триггеры 60, 63 записывается лог. О, который устанавливается на выходе 17 ( выходе элемента 64). В результате на выходе канала 19 устанавливается лог. 1, а на входе 8 устанавливается лог. О (см. описание коммутатора 2). под действием которого на выходе мультиплексора 20 и на выходе элемента 51 устанавливается высо- коимпедансное состояние в течение всего такта, если на входе 30 установлен лог. О. В этом же такте возможно, что на входе 30 будет установлена лог. 1 (означающая запрос на передачу сообщения из кольца в общую шину). Если при этом на входе 8 установится лог. 1, то на шине 35 вновь установится лог. О, а на шину 16 будет передано сообщение со входа 9, так как на выходе 33 установлен уже лог. О. Далее устройство будет функционировать как было описано выше (при передаче сообщения из кольца через общую шину). Следует только добавить, что если на шине 36 не установится лог. О, то передачи сообщения через общую шину не происходит и сообщение запоминается со входа 9 в регистр 25 и передается (при необходимости) в кольце дальше до тех пор, пока не будет принято в регистр 27 канала 1, свзяанного с адресуемым модулем 4.

С помощью элемента ИЛИ-НЕ 5 обеспечивается селекторная передача сообщений всего массива (за несколько тактов)

благодаря блокировке запросов на селекторный обмен от других каналов 1, даже имеющих более высокий приоритет. При этом параллельно обеспечивается двухсто- 5 ронний обмен сообщениями через кольцо между любыми каналами 1, в том числе и между принимающим и передающим через общую шину каналами 1.

Формула изобретения

10Устройство связи для вычислительной

системы, содержащее m каналов связи, коммутатор управляющих сигналов, блок синхронизации, причем первый информационный выход 1-го канала связи (где I 1 .т)

5 соединен с первым информационным входом (1+1)-го канала связи, первый информационный выход т-го канала связи соединен 1 с первым информационным входом первого канала связи, первый и второй выходы 1-го

0 канала связи соединен с соответственно с первым и вторым входом 1-й группы входов коммутатора управляющих сигналов, 1-вы- ход которого соединен с первым управляющим входом 1-го канала связи, второй

5 информационный вход, второй информационный выход, входы запроса на передачу и подтверждение приема, выходы признака передачи и удовлетворения запроса которого являются одноименными входами и

0 выходами 1-й группы входов и выходов устройства, выход блока синхронизации соединен с входом синхронизации всех каналов связи, информационные входы-выходы которых соединены через информационную

5 магистраль, причем каждый канал связи содержит блок управления, регистр передачи, регистр приема, первый и второй мультиплексоры, первый узел сравнения, регистр адреса, первый и второй выходы и первый

0 управляющий вход канала связи соединены соответственно с первым и вторым выходами и первым входом блока управления, входы запроса на передачи и подтверждения приема, выходы признака передачи и удов5 летворения запроса которого соединены соответственно с одноименными входами и выходами канала связи, первый информационный вход которого соединен с первым информационным входом первого мульти0 плексора, старшие разряды первого информационного входа соединены с первым информационным входом второго мультиплексора, выход которого соединен с информационным входом приемного реги5 стра, вход режима которого соединен с третьим выходом блока управления, выход приемного регистра соединен с вторым информационным выходом канала связи, первый информационный выход которого соединен с выходом передающего регист ра,

информационный вход которого соединен с выходом первого мультиплексора, первый и второй управляющие входы которого соединены соответственно с четвертым и пятым выходом блока управления, шестой управ- ляющий выход которого соединен с управляющим входом второго мультиплексора, второй информационный выход которого соединен с информационным входом-выходом канала связи, второй информационный вход которого соединен с вторым информационным входом первого мультиплексора, второй, третий и четвертый входы блока управления соединены соответственно с первым, вторым и третьим выходами и первого узла сравнения, первый вход которого соединен с выходом регистра адреса и разрядами адреса второго информационного входа канала связи, разряды адреса назначения и разряд идентификации сообщения первого информационного входа канала связи соединены соответственно с разрядами второго информационного входа первого узла сравнения, вход синхронизации блока управления соединен с входами син- хронизации регистра передачи и регистра приема и входами синхронизации канала связи, отличающееся тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности селекторного об-

мена между каналами связи, в устройство введен элемент ИЛИ-НЕ, причем третий выход 1-го канала связи соединен с 1-м входом элемента ИЛИ-НЕ, выход которого соединен с вторым управляющим входом всех каналов связи, управляющие входы-выходы которых соединены через управляющую магистраль устройства, а в каждый канал связи введены второй узел сравнения и третий мультиплексор, причем пятый вход блока управления соединен с выходом второго узла сравнения, первый вход которого соединен с выходом регистра адреса и разрядами адреса второю информационного входа канала связи, второй вход второго узла сравнения соединен с разрядами адреса назначения информационного входа-выхода канала связи, первый информационный вход третьего мультиплексора соединен с первым информационным входом канала связи, второй вход которого соединен с вторым информационным входом третьего мультиплексора, выход которого соединен с информационным входом-выходом канала связи, первый и второй управляющие входы третьего мультиплексора соединены соответственно с седьмым и восьмым выходами блока управления, шестой выход которого соединен с вторым управляющим входом канала связи.

31

| Каляев А.В | |||

| Многопроцессорные системы с программируемой архитектурой.- М.: Радио и связь, 1984, с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| Приспособление к тростильной машине для прекращения намотки шпули | 1923 |

|

SU202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1988-04-04—Подача