(54) УСТРОЙСТВО СВЯЗИ ДЛЯ ВЫЧИСЛИТЕЛЬНСЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

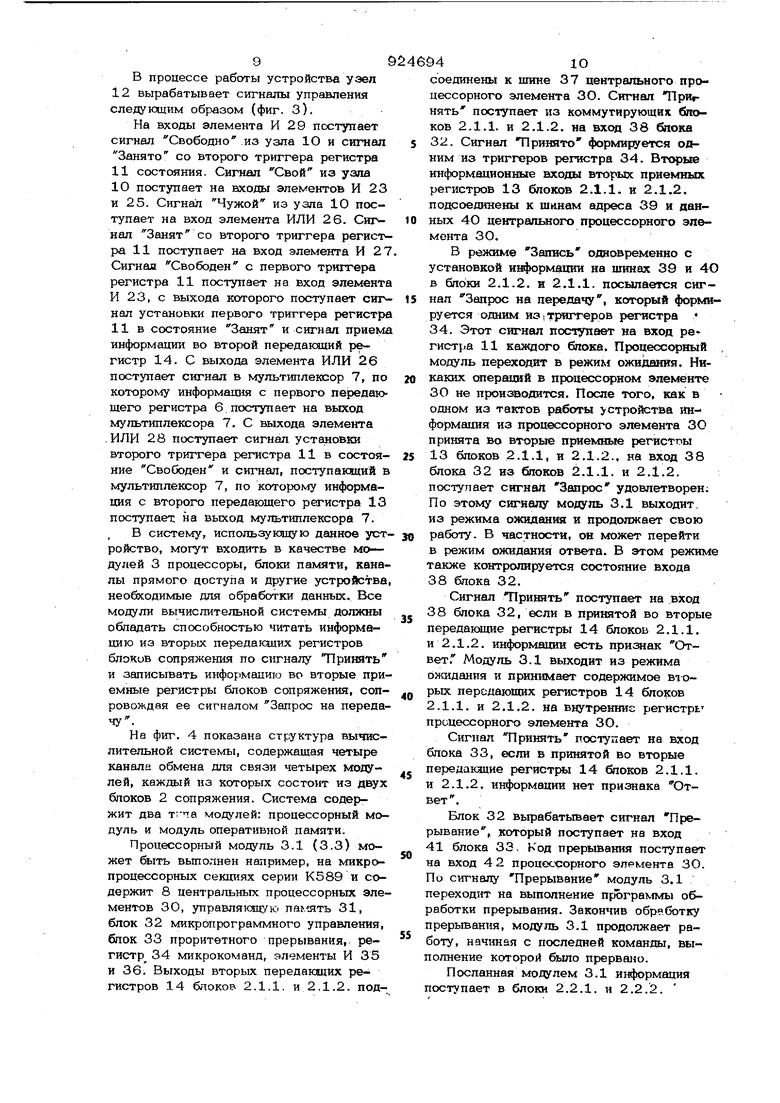

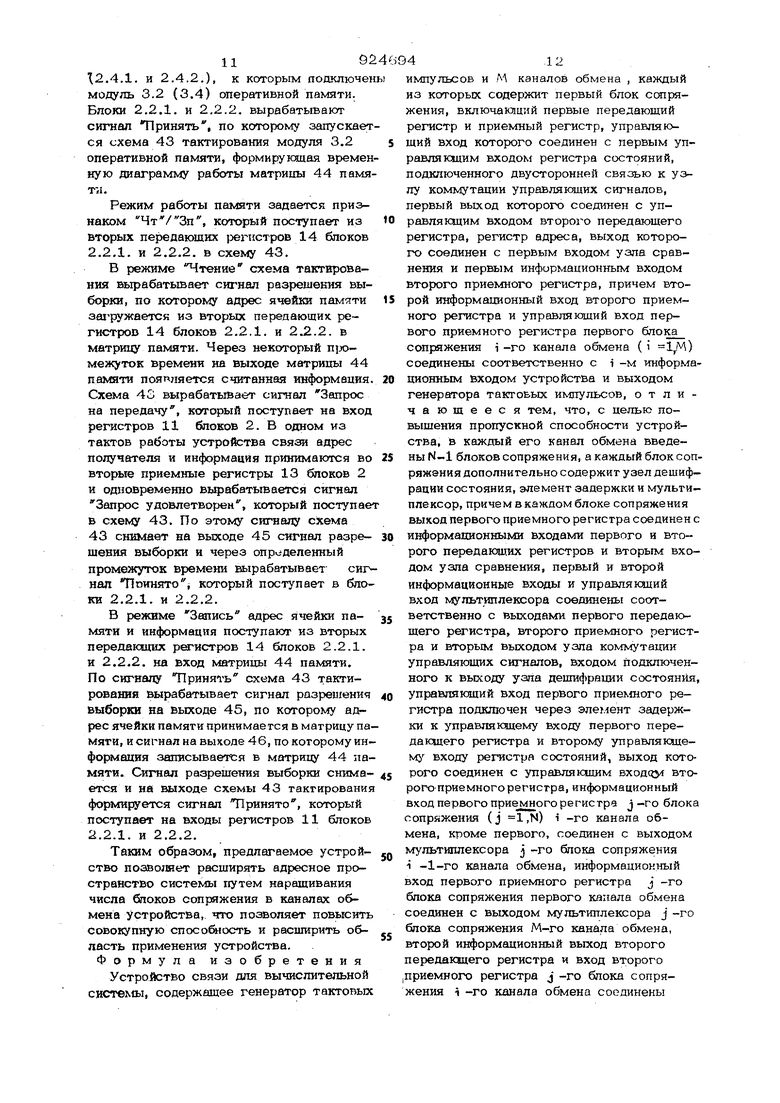

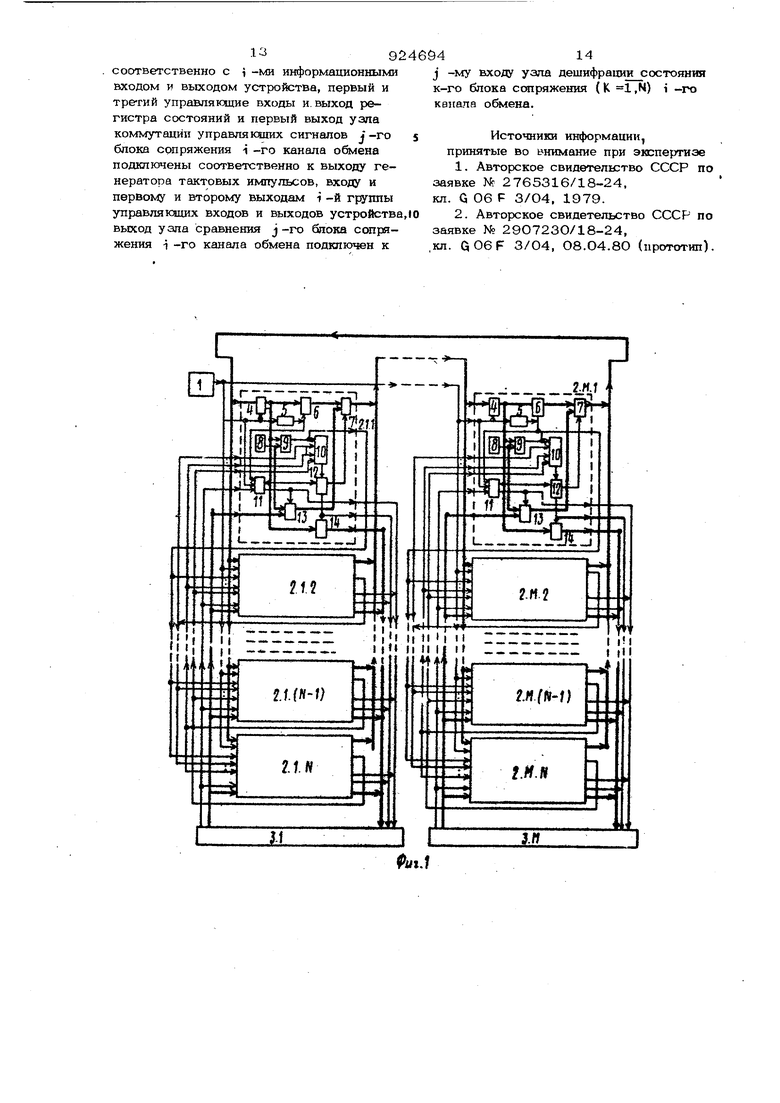

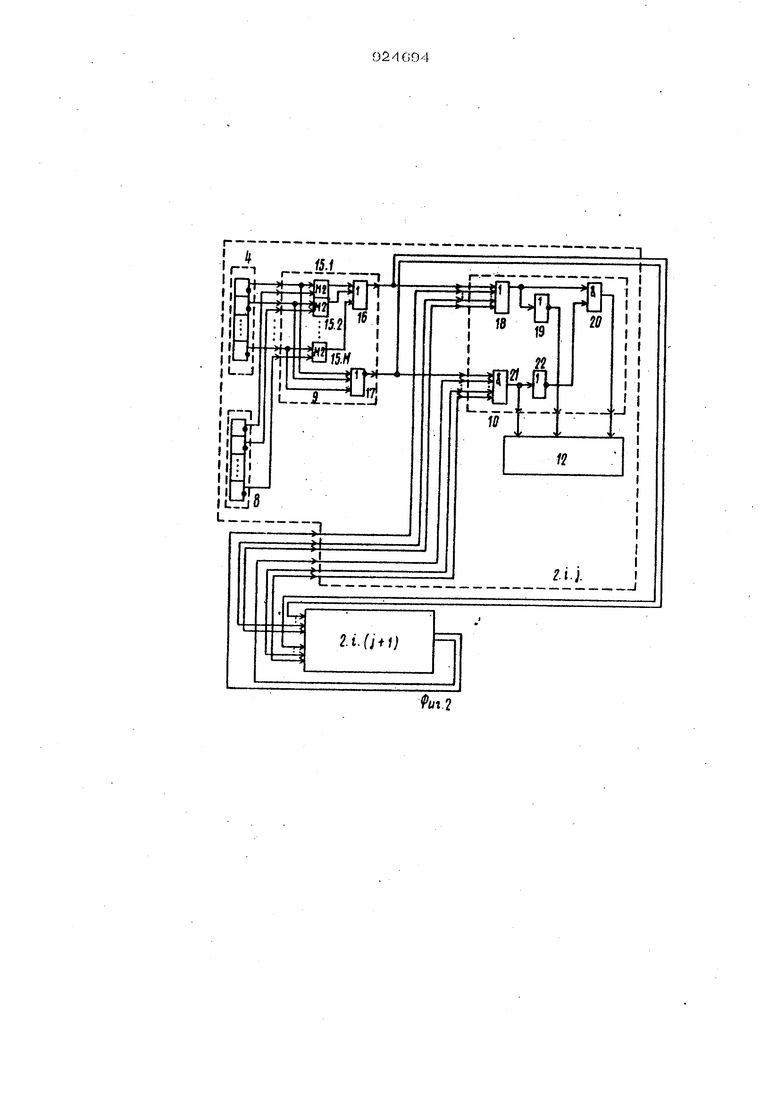

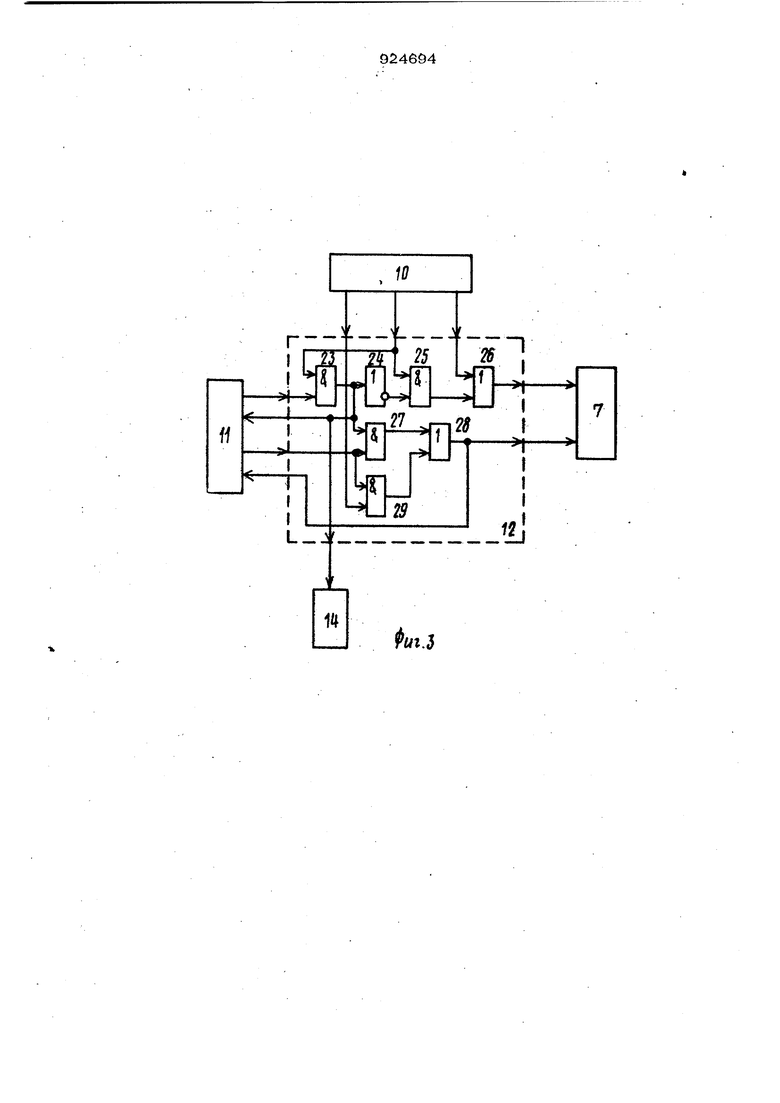

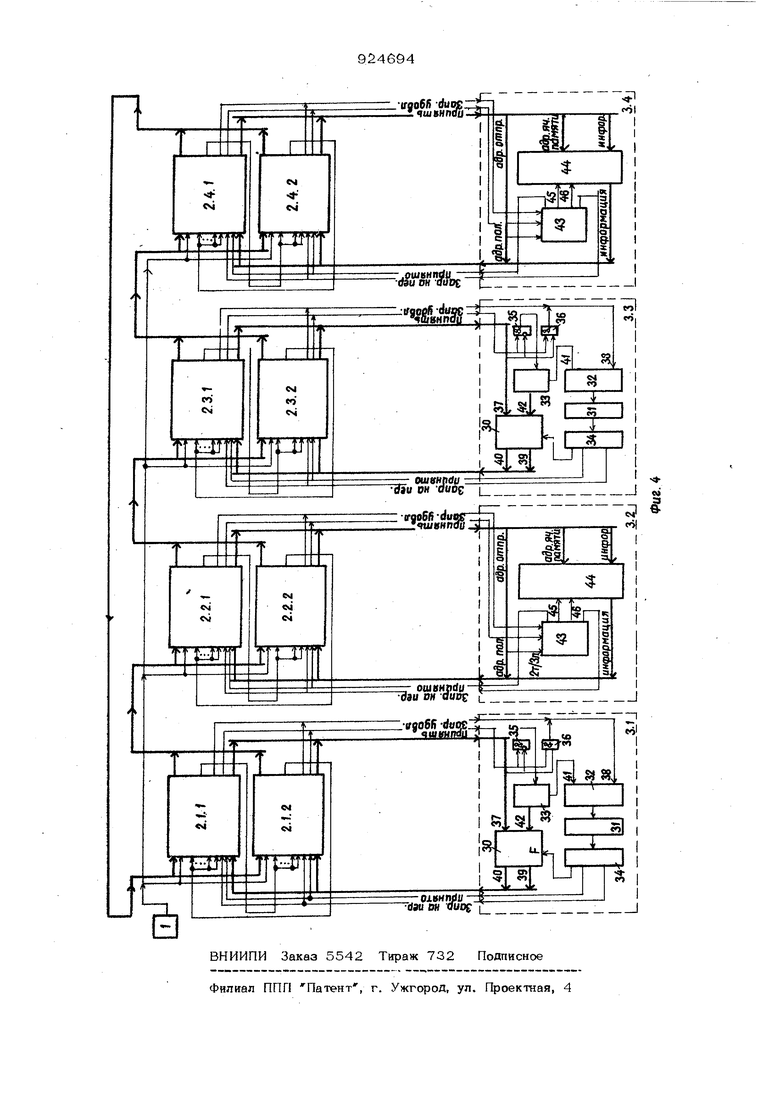

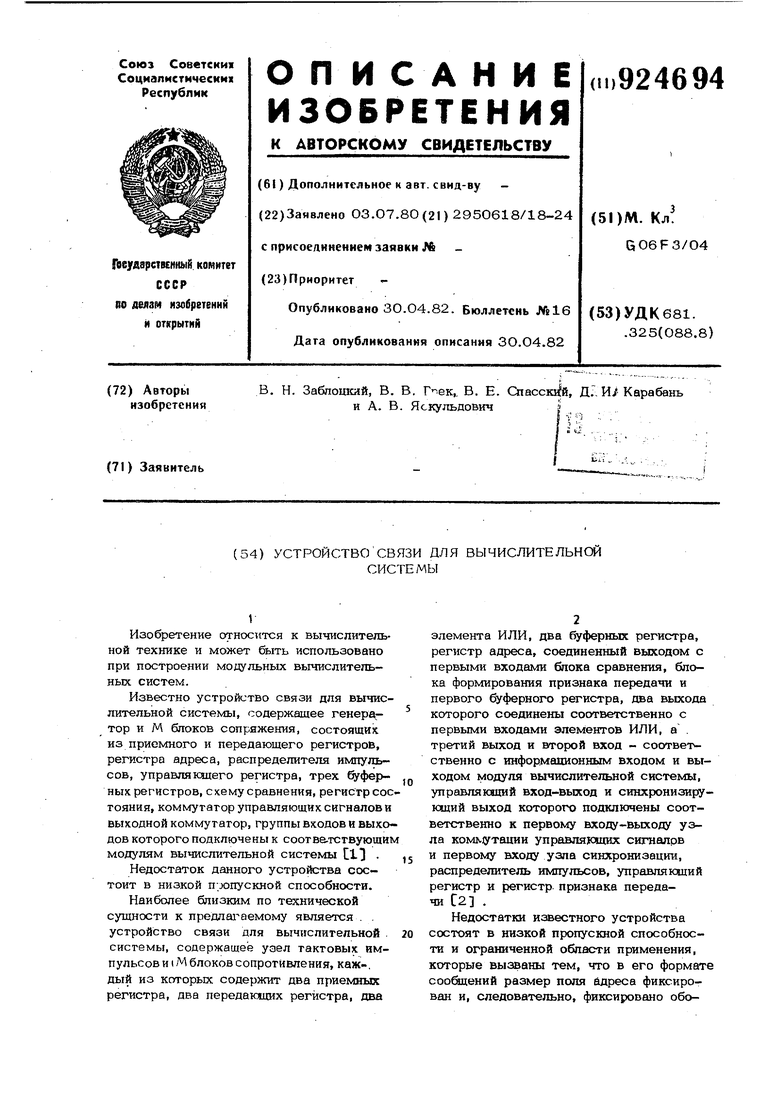

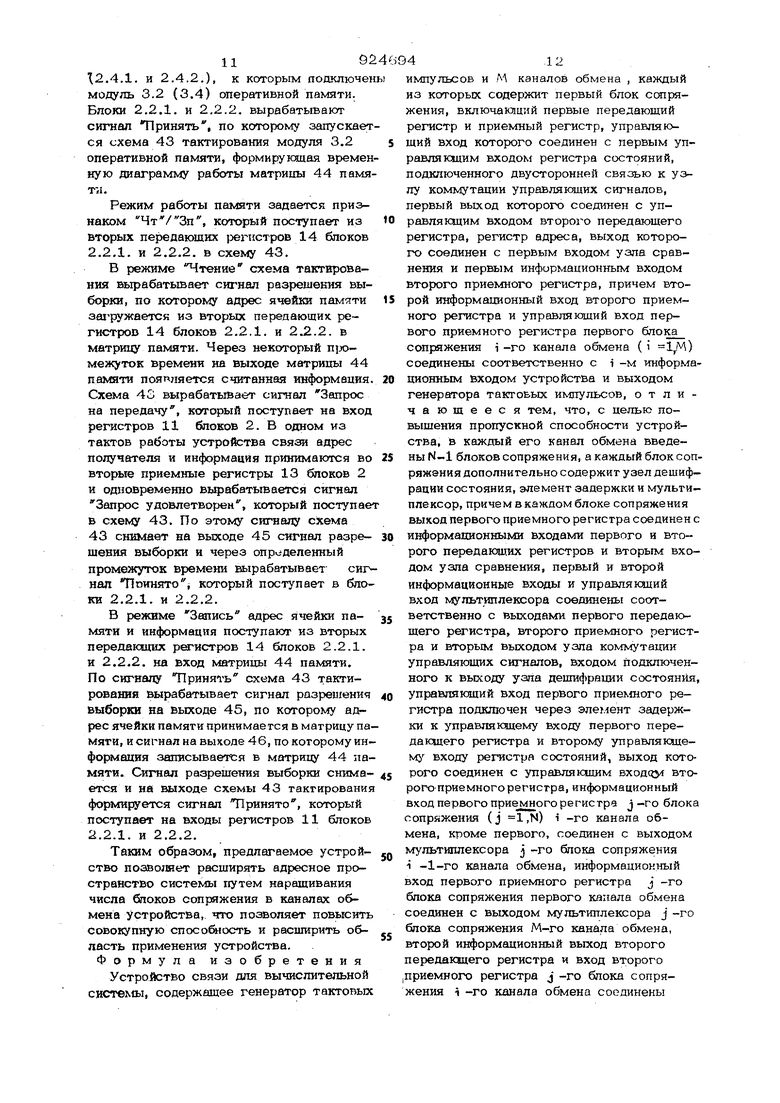

Изобретение относится к вычислительной технике и может бъгть использовано при построении модульных вычислительных систем. Известно устройство связи для вычислительной системы, содержащее генератор и М блоков сопряжения, состоящих из приемного и передающего регистров, регистра адреса, распределителя импульсов, управляющего регистра, трех Оуферкных регистров, схему сравнения, регистр сос тояния, коммутатор управляющих сигналов и выходной коммутатор, группы входов и выхо дов которого подключены к соотве-тствующи модулям вычислительной системы Cll Недостаток данного устройства состоит в низкой пюпускной способности. Наиболее близким по технической сущности к предлшаемому является . устройство связи для вычислительной . системы, содержащее узел тактовых импульсов и (М блоков сопротивления, каж-. дый из которых содержит два приемных регистра, два передающих регистра, два элемента ИЛИ, два буферных регистра, регистр адреса, соединенный выходом с первыми входами блока сравнения, блока формирования признака передачи и первого буферного регистра, выхода которого соединены соответственно с первыми входами элементов ИЛИ, а . третий выход и второй вход - соответственно с информационным входом и выходом модуля вычислительной системы, управляющий вход-выход и синхронизирующий выход которого подключены соответственно к первому входу-выходу узла комг утации управляющих сигналов и первому входу узла синхронизации, распределитель импульсов, управляющий регистр и регистр признака передачи С2 . Недостатки известного устройства состоят в низкой пропускной способности и ограниченной области применения, которые вызваны тем, что в его формате сообщений размер поля адреса фиксирован и, следовательно, фиксировано оборудовнния схемы сравнения, регистра адреса модуля, приемных и передающих регистров, которые входят в состав каналов o&vieHa. Для того, чтобы увеличит пропускную спосойюсть системы путем увеличения числа модулей, необходимо заменять оборудование каналов обмена усаройства связи. Цель изобретения - повышение пропускной способности устройства. Поставленная цель достигается тем, что в устройство, содержащее генератор тактовых импульсов и М каналов обмена, каждый из которых содержит первый блок сопряжения, включающий первые передающий регистр и приемный регистр, управлякшьй вход которого соединен с первым управляющим входом регистра состояний, подключенного двусторонней связью к узлу коммутации управляющих сигналов, первый выход которого соединен с управляющим входом второго передающего регистра, регистр адреса, выход которого соединен с первым входом у згш сравнения и первым информационным входом второго приемного регис тра, причем второй информационный вход второго приемного регистра и управляющий вход первого приемного рехтястра пеовогч бло1 сопряжения i -го канала обмена ( i 1 ,М) соединены соответствен но с i -м информационным входом устройства и выходом генератора тактовых импульсов, введены в каждый канал обмена N -1 блоков сопряжения, а каждый блок сопряжения дополнительно содержит узел дешифраций состояния, элемент задержки и мультиплеюсор, причем в каждо блоке сопряжения выход первого приемного регистра соединен с информационными вкодами первого и второго передающих регистров и вторьпу входом узла сравнения, первый и второй информадион ные входы и управляющий вход мультиплексора соединены соответственно с выходами первого передающего регисгра, второго приемного регистра и BTopbns выходом узла коммутации управляющих сигналов, входом подключенного к выходу уапа дешифрации состояния, управляющий вход первого приемного регистра подклт чен через элемент задержки к управляющему,входу первого передающего регистра иь второму управлякяцему входу регистра состояний, выход которог соединен с управляющим входом второго приемного регистра, информационный вход первого приемного регистра j-ro блока сопряжения (j 1,N) i -го канала 9 44 обмена, кроме первого, соединен с вы- i ходом мультиплексора j -го блока сопряжения i -1-го канала обмена, информационный вход первого приемного регистра. j-ro блока сопряжения первого канала обмена соединен с выходом мультиплексора j -го блока сопряжения М-го канала обмена, второй информационный вход второго приемного регистра и выход второго передающего регистра j -го блока сопряжения i -го канала обмена соединены соответственно с i -ми информационными входом и выходом устройства, первый и третий управляющие входы и выход регистра состояний и первый выход узла коммутации управляи щих сигналов j -го блока сопряжения 1-го канала обмена подключены соответственно к выходу генератора тактовых импульсов, входу и первому и второму выходам 1 -и группы управляющих входов и выходов устройства, выход узла сравнешш j -го блока сопряжения i -го канала обмена подключен к j -му входу узла дешифрации состояния к-го блока сопряжения (К 1,N) i -го канала обмена. На фиг, 1 представлена блок-схема устройства; на фиг. 2 - функциональные схемы узла дешифрации состояния и узла сравнения; на фиг. 3 - функциональная схема узла коммутации управляющих сигналов; на фиг. 4 - пример структуры системы, использующей данное устройство. Устройство содержит (фиг. 1) генератор 1 тактовых импульсов, блоки 2 сопряжения, соединенные с соответствующими модулями 3 вычислительной системы. Группа блоков 2 сопряжения, соединенных с информационными и управлякадими входалет и выходами с одним и тем же модулем 3, образует канал обмена. Каждый блок 2 сопряжения содержит первый приемный регистр 4, элемент 5 задержки, первый передающий регистр 6, мультиплексор 7, рет-истр 8 адреса, узел 9 сравнешш, узел 10 дешифрации состояния, регистр Псосгояния, узел 12 коммутации управляющих сигналов, вторые приемный 13 и передающий 14регистры. Узел 10 дешифрации состояния и узел 9 сравнения содержат {фиг. 2) сумматоры 15по модулю 2, элемент ИЛИ 16, элемент ИЛИ-НЕ 17, элемент ИЛИ 18. элемент НЕ 19, элементы И 20, 21 и элемент НЕ 22. Узел 12 коммутации управляющих сигналов (фиг. 3) состоит из первого элемента И 23, элемента НЕ 24, второ элемента И 25, первого элемента ИЛИ 26, третьего элемента И 27, второхх) элемента ИЛИ 28, четвертого элемента И 29, Генератор 1 тактовых импульсов пре назначен для синхронизации работы устройства. Блоки 2 идентичны по структуре я преднйзначены для приема (выдачи) информашга из (в) модулей 3 вычислитель ной системы и выдачи (приема) информ ции в (из) магистраль, образованную из пассивных шин адреса и данных и замкнутых в кольцо. Элемент о задержки предназначен для задержки тактового импульса, посту пающего на управлякх1тий вход блока 2. Мультиплексор 7 содержит набор управляемых, элементов И и элемент ИЛИ и предназначен для выбора и передачи информации с выходов второго приемног регистра 13 или первого передаюшегю регистра 6. Регистр 8 адреса преднаа1ачен для хранения собстзеннохч) адреса блока 2. Адрес в регистр 8 адреса заносится с помснцью тумблерного набора (не показан). Узел 9 сравнения предназначен для сравнения поля адреса получателя с соб ственным адресом данного блока 2, Узел 10 предназначен для интерпретации значений сигналов, поступакндих как из узла 9 сравнения данного блока 2, так и узпоь сравнения других блоков 2 того же канала охотна, и формирован сигналов управления режимами работы блока 2. Регистр 11 состояния содержит дВа триггера и предназначен для индикации состояния блока 2. В качестве модулей 3 вычислительно системы могут использоваться процессо ры, блотга памяти, прямого доступа и т.п. Устройство работает следующим обра зом. После пуска устройства генератор 1 (фиг. 1) начинает вырабатывать тактовые имп льсы, под управлением которых в устройстве нрчинаюг циркулировать свободные слова информации. Формат слова информации, пересыпаемого между блоками каналов обмена, имеет следующие поля: адрес отправителя; адгюс пол чателя; данные (адрес ячейки памяти, признак Запрос/Ответ, признак Чтение/Запись, собственно информация). По каждому TaKToBcAjy импульсу происходит передача слов информации между блоками каналов о&лена. Под управлением тактового икшульса информация записывается в первый приемный регистр 4, а под управлением задержанного тактового импульса она записывается в первый передающий регистр 6. По приему инфoJ aции в первый приемный регистр 4 в каждсм бпоке 2 происходит сравнение попей адреса получателя с собственным адресом данного блока 2, в ре льтате чего на выходе узла 9 формируются сигналы Равно, Не равно, Свободно , Занято, nociynaioщие на соответствующий выход блока 2 и вход узла 1О. Е.ли на входах узла 10 присутствует набор сигналов Равно, Не равно , Свободно , Занято, то на его ы 1ходе формируется сигаал Чужой, означающий, что на информационней выходе первого регистра 4 всех бгюков данного канала обмена присутствует информация, адресованная не своему модулю 3. Если на входах у ала 1О присутствует набор сигналов Равно, Свободно, Занято , или Равно, Занято, то на его выходе формируется сигнял Свой, означающий, что на информационном выходе первого приемното регистра 4 всех блоков 2 данного канала обмена присутствует информация, адресованная данному своему модулю 3. Если на входах узла 1О присутствует набор сигналов Свободно, Равно, Не равно или Свободно, Не равно , то Hfl его выходе формируется сигнал Свободно, означающий, что на информационном выходе первого приемного регистра 4 всех блоков 2 данного канала присутствует нулевая информация (адрес получателя равен нулю). Каждый канал обмена работает в двух pexHiviax: Чтение и Запись . Режим Чтение вьшолняется в два этапа. На первом этапе происходит сравнение поля адреса получателя слова информации, принятого в первый приемный регистр 4 из блока 2 предшествующего канала обмена, описанное выше. На втором этапе в зависимости от сигналов, сформированных на выходе узла 10, вьшолняется собственно режим Чтение. Если чр выходе уата 10 сформировался сигнал Чужой, то из узла 12 н упрнвлякхций иход лгультиплексора 7 ; поступает сигнал, по которому информация с первого передающего регистра 6 поступает на выход КГультиплексора 7. В следующем такте эта информация зяйисывается в одноименный блок 2 поспеду кщего кан ал а обмена. Если на выходе узла Ю сформировался сигнал Свободно, то УЗИЛ 12 не вырабатывает ситнала управления мультиплексором 7 и информация с первого передакхцего регистра 6 не поступ ет на выход мультиплексора 7. В следу щем такте в одноименный блок 2 последу ющмо канала обмена записывается нулевая информация. Пели на выходе узла 1О сформировал ся сигнал Свой и первый триггер регистра И состояния, фиксирующий незанятность второго передающего регистра 14, находится в состоянии Свободен то узел 12 вырабатывает сигнал, поступающий в регистр 11, сигнал, поступающий во второй передающий регистр 14, и сигнал Принять, поступакдций в свой модуль 3. По сигналу из узла 12 во вто рой передакпгой регистр 14 записываетс информация (адрес отправителя, данные) из первого приемного регистра 4. В сле дующем такгге задержанным тактовым импульсом первый триггер регистра 11 устанавливается в состояние Занят. В одноименный блок 2 послед кшегг канала записывается нулевая информация. I По сигналу Принять модуль 3 переписывает информацию (адрес отправителя, данные) из второго передающего регистра 14 на свои регистры и формирует сигнал ТЕринято, которым по приходу тактового импульса первый триггер регистра 11 устанавливается в состояние Свободен. Если на выходе узла 10 сформировался сигнал Свой и первый триггер регистра 11 находится в состоянии Занят, то узел 12 формирует сигнал, пос тупающий на управляющий вход мультиплексора 7. Далее происходят действия, аналогичные де твиям по сигналу Чужой, описанным выше, В режиме Запись, когда модулю 3 Необходимо передать информацию в м гистраль, он формирует сигнал Запрос на передачу, поступает на управляющий вход регистров 11 блокоэ 2 данного канала обмена. Режим Запись выполняется в два этапа. На первом этапе, если втррой триггер регистра 11, фиксирующий незанятость второго приемного регистра 13, находится в состоянии Свободен, ix по приходу тактового импульса в регистре 11 формируется сигнал, по которому второй триггер регистра 11 устанавливается в состояние Занят. Во второй приемный регистр 13 посылается сигнал, по которомув него записывается информация (адрес получателя, данные) из своего модуля 3 и информация (адрес отправителя) из регистра 8 адреса. С выхода регистра 11 в модуль вычислительной системы посылается сигнал Запрос удовлетворен, по приему которого модуль вышслительной системы снимает сигнал Запрос на передачу. На первом этапе также происходит сравнение поля адреса получателя слова кнформашги, принятого в первый приемный регистр 4 из одноименного блока предществующего канала обмена, описанное вьпие. На втором этапе в зависимости от сигналов, сформированных на выходе узла 10, вьшолняется собственно режим Запись, Если на выходе узла 10 сформ фовался сигнал Чужой, то происходят действия, аналогичные действиям по этому сигналу, описанным в режиме Чтение. Если на выходе узла Ю сформировался сигнал Свободно, то узел 12 по состоянию второго триггера Занят регистра 11 состояния формирует сигнал, поступающий на управляющий вход ryльтиплeксора 7, и сигнал, поступающий в регистр 11. По сигналу из узла 12 на выход мультиплексора 7 поступает информацияс второго приемного регистра 13. В следующем такте по приходу задержанного тактового импульса второй триггер регистра 11 устанавливается в состояние Свободен. Если на выходе узла Ю сформировался сигнал Свой и первый триггер регистра 11 находится в состоянии Свободен, то вьтолняется режим Чтение, описанный выше, и по состоянию второго триггера Занят регистра 11 узел 12 формирует сигнал, поступающий на управлякаций вход мультиплексора 7 и врегистр 11. Далее происходят действия, аналогичные действиям по сигналу Свободно, описанные выше в режиме Запись. В процессе работы устройства узел 12 вырабатывает сигналы управления следующим образом (фиг. 3). На входы элемента И 29 поступает сигнал Свободно из узла Юн сигнал Занято со второго триггера регистра 11 состояния. Сигнал Свой из узла 10поступает на входы элементов И 23 к 25. Сигнал Чужой из узла 10 пос тупает на вход элемента ИЛИ 26. Сигнал Занят со второго триггера регистра 11 поступает на вход элемента И 27 Сигнал Свободен с первого триггера регистра 11 поступает на вход элемента И 23, с выхода которого поступает сигнал установки первого триггера регистра 11в состояние Занят и сигнал приема информации во второй передающий регистр 14. С выхода элемента ИЛИ 26 поступает сигнал в мультиплексор 7, по которому информахшя с первого передающего регистра 6.поступает на выход мультиплексора 7. С выхода элемента .ИЛИ 28 поступает сигнал установки второго триггера регистра 11 в состояние Свободен и сигнал, поступающий в мультиплексор 7, по которому информация с второго передающего регистра 13 поступает на выход мультиплексора 7. В систему, используклыую данное устройство, могут входить в качестве модулей 3 процессоры, блоки памяти, каналы прямого доступа и другие устройства необходимые для обработки данных. Все модули вычислительной системы должны обладать способностью читать информацию из вторых передающих регистров блоков сопряжения по сигналу Принять и записывать информацию во вторые приемные регистры блоков сопряжения, сопровождая ее сигналом Запрос на передаНа фиг. 4 показана структура вычислительной системы, содержащая четыре канала обмена для связи четырех модулей, каждый из которых состоит из двух блоков 2 сопряжения. Система содержит два тгпа модулей: процессорный модуль и модуль оперативной памяти. Процессорный модуль 3.1 (З.З) может быть выполнен например, на микропроцессорных секциях серии К589 и содержит 8 центральных процессорных элементов 30, управлякис/ю паг.тъ 31, блок 32 микропрограммного управления, блок 33 проритетного прерывания, регистр 34 микрокоманд, элементы И 35 и 36. Выходы вторых передающих регистров 14 блоков 2.1.1. и2.1.2. под- соединены к нгане 37 центрального процессорного элемента ЗО. Сигнал Приг нять поступает из коммутирующих блоков 2.1.1. и 2.1.2. на вход 38 блока 32. Сигнал тринято формируется одним из триггеров регистра 34. Вторые информаинонгале входы вторых приемных регистров 13 блоков 2.1.1. и 2.1.2. подсоединены к шинам адреса 39 и данных 40 дентралыгого процессорного элемента ЗО. В режиме Запись одновременно с установкой информации на шинах 39 и 4О в бпокн 2.1.2. и 2.1.1. посылается сигнал Запрос на передачу, который формируется одним из I тржггеррв регистра 34. Этот сигнал поступает на вход регистра 11 каждого блока. Процессорный , модуль переходит в режим ожидания. Никаких операций в процессорном элементе ЗО не производится. После того, как в одном из тактов работы устройства информация из процессорного элемента ЗО принята во вторые приемные регистры 13 блоков 2.1.1, и 2.1.2., на вход 38 блока 32 из блоков 2.1.1. и 2.1.2. поступает сигнаЯ Запрос удовлетворен; По этому сигналу модуль 3.1 выходит, из режима ожидания и продолжает свою работу. В частности, он может перейти в режим ожидания ответа. В этом режиме также контролируется состояние входа 38 блока 32. Сигнал Принять поступает на вход 38 блока 32, если в принятой во вторые передающие регистры 14 блоков 2.1.1. и 2.1.2. информации есть признак Ответ. Модуль 3.1 выходит из режима ожидания и принимает содержимое вюрых передающих регистров 14 блоков 2.1.1. и 2.1.2. на внутренние регистра процессорного элемента ЗО. Сигнал Принять поступает на вход блока 33, если в принятой во вторые передающие регистр 14 блоков 2.1.1. и 2.1.2. информации нет признака Ответ. Блок 32 вырабатьгоает сигнал Прерывание, который поступает на вход 41 блока 33. Код прерывания поступает на вход 4 2 процессорного элемента ЗО. По сигналу Прерывание модуль 3.1 переходит на выполнение программы обработки прерывания. Закончив обработку прерывания, модуль 3.1 продолжает работу, начиная с последней комгшды, выполнение которой было прервано. Посланная модулем 3.1 информация поступает в блоки 2.2.1. и 2.2.2. 1192 (2,4.1. и 2.4.2.), к которым подключен модуль 3.2 (3.4) оперативной памяти. Бпоки 2.2.1. и 2.2.2. вырабатывают сигнал Принять, по которому запускает ся схема 43 тактирования модуля 3.2 оперативной памяти, формирующая времен ную диаграмму работы матрицы 44 памя Режим работы памяти задается признаком Чт/ 3п, который поступает из вторых передакших i erucTpoB 14 блоков 2.2.1. и 2.2.2. в схему 43. В режиме Чтение схема тактирования вырабатьюает сигнал разрешения выборки, по которому адрес ячейки памяти зшружается из вторых передающик ре гистроп 14 блоков 2.2,1. и 2.2.2. в матрицу памяти. Через некоторый щх межуток времени на выходе матрицы 44 памяти появляется считанная информация Схема 43 вырабатьюает сигнал Запрос на передачу, который поступает на вход регистров 11 блоков 2. В одном из тактов работы устройства связи адрес получателя и информация принимаются во BTOfftie приемные регистры 13 блоков 2 и одновременно вырабатывается сигнал Запрос удовлетворен, который поступае в схему 43. По этому сигналу схема 43 с-цкма&т на выходе 45 сигнал разрешения выборки и через опр зделенный промежуток времени вырабатывает сигнал ТТоинято который поступает в блоки 2.2.1. и 2.2.2. В режиме Запись адрес ячейки памяти и информация поступают из вторых передающих регистров 14 блоков 2.2.1. и 2.2.2. на вход матрицы 44 памяти. По сигналу Принять схема 43 тактирования вырабатывает сигнал разрешения выборки на выходе 45, по которому адрес ячейки памяти принимается в матрицу па мяти, и сигнал на выходе 46, по которому кнфо1л а11ня записывается в матрицу 44 памяти. Сигнал разрешения выборки снимается и на выходе схемы 43 гакгирования формируется сигнал Принято, который поступает на входы регистров 11 блоков 2.2.1. и 2.2.2. Таким образом, предлагаемое устройство позво;шет расширять адресное пространство системы путем наращивания числа блоков сопряжения в каналах обмена устройства, что позволяет повысить совокупную способ ость и расширить область применения устройства. Формула изобретения Устройство связи для вычислительной системы, содержащее генератор тактовых 412 импульсов и -М каналов обмена , каждый из KOTopbtx содержит первый блок сопряжения, включаЮ1Ш1й первые передающий регистр и приемный регистр, управляющий вход которого соединен с первым управляющим входом регистра состояний, подключенного двусторонней связью к узлу коммутации управляющих сигналов, первый выход которого соединен с управлягацим входом второго передающего регистра, регистр адреса, выход которого соединен с первым входом узла сравнения и первым информационным входом второго приемного регистра, причем второй информационный вход второго приемного регистра и управляющий вход первого приемного регистра первого блока сопряжения 1 -го канала обмена ( i 1/А) соединены соответственно с i -м информационным входом устройства и выходом генератора тактовых импульсов, отличающееся тем, что, с целью повышения пропускной способности устройства, в каждый его канал обмена введены N-1 блоков сопряжения, а каждый блок сопряжения дополнительно содержит узел дешифрации состояния, элемент задержки и мультиплексор, причем в каждом блоке сопряжения выход первого приемного регистра соединен с информационными входами первого и второго передающих регистров и вторым входом узла сравнения, первый и второй информационные входы и управляющий вход мультиплексора соединены соответственно с выходами первого передаю щего регистра, второго приемного регистра и вторым выходом узла коммутации управляющих сигналов, входом подключенного к выходу узла дешифрации состояния, управляющий вход первого приемного регистра подключен через элемент задержки к управляющему входу первого передающего регистра и второму управляющему входу регистра состояний, выход которого соединен с управляющим входс м второго приемного регистра, информационный вход первого приемного регистре j -го блока сопряжения (j 1 ,N) i -го канала обмена, кроме первого, соединен с выходом мультиплексора j -го блока сопряжения i -1-го канала обмена, информационный вход первого приемного регистра j -го блока сопряжения первого капала обмена соединен с выходом мультиплексора j -го блока сопряжения М-го канала обмена, второй информационный выход второго передающего регистра и вход второго приемного регистра j -го блока сопряжения i -го канала обмена соединены соответственно с { -ми информационными входом и выходом устройства, первый и третий управляющие входы и. выход регистра состояний и первый выход узла коммутации управляющих сигналов j-го блока сопряжения i -го канала обмена подключены соответственно к выходу генератора тактовых импульсов, входу и перво и второму выходам i -и группы управляющих входов и выходов устройств выход узла сравнения j -го блока сопряжения i -го канала обмена подключен к 9 4 j -му входу узла дешифрации состояния к-го блока сопряжения (К 1 ,N) i -го капала обмена. Источники информации, принятые во внимание при экспертизе 1.Авторское свидвтелы;тво СССР по заявке № 2765316/18-24. кл. G 06 F 3/04. 1979. 2.Авторское свидетельство СССР по заявке № 29О7230/18-24, ,кл. QO6F 3/О4, О8.О4.8О (прототип).

-г -MI

if

.ff

Авторы

Даты

1982-04-30—Публикация

1980-07-03—Подача