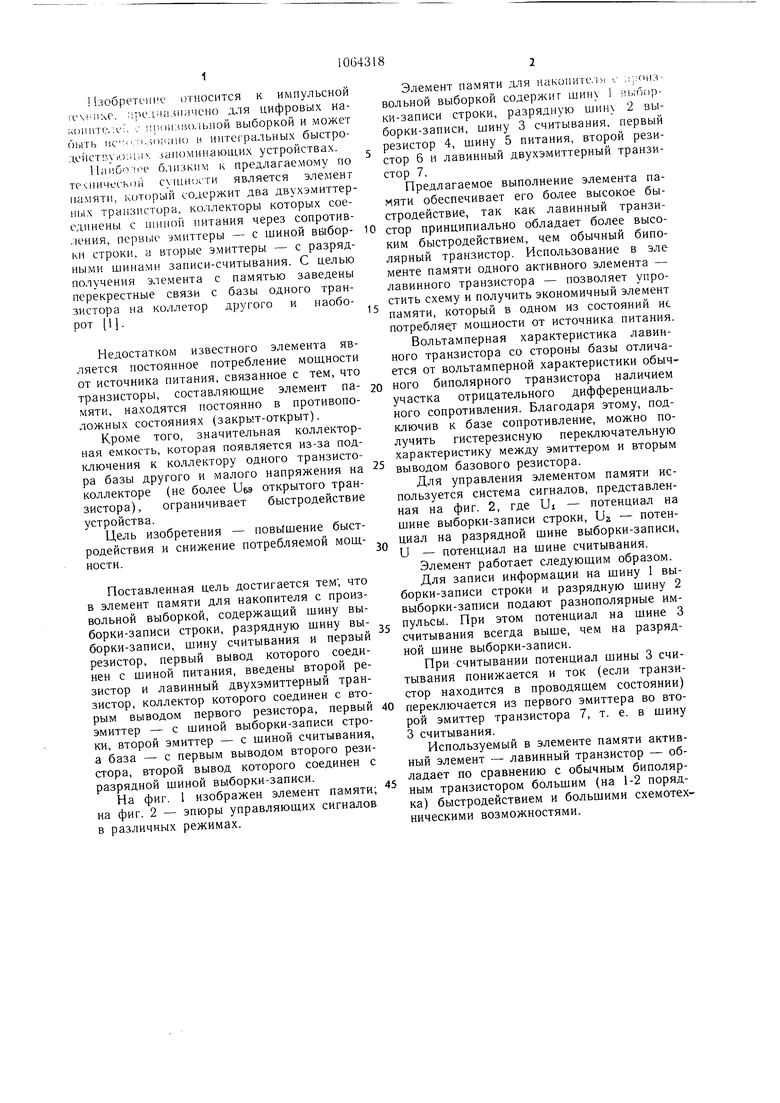

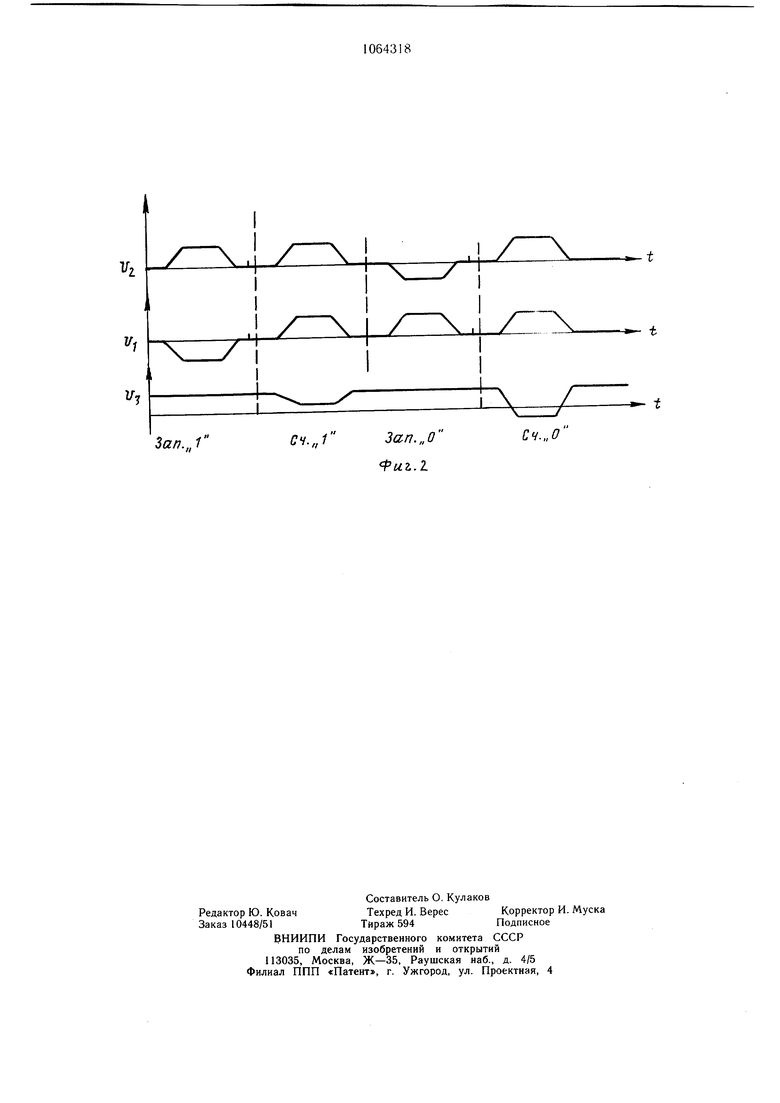

1зобрете11ио относится к импульсной . :;ре.ч.1а.5иачсно для цифровых наKDiinio.л; . 1П).)из1и)льиой выборкой и может быть ис.M.ioniiiio в ннтесральных быстродействующих запоминающих устройствах. llai.Go (е близким к предлагаемому по течнической сущности является элемент памяти, ()рый содержит два двухэмиттерных транзистора, коллекторы которых соеединеиы с 1ниной питания через сопротивления, перв1 1е :)миттеры - с шиной выборки строки, а вторые эмиттеры - с разрядными шинами записи-считывания. С целью получения элемента с памятью заведены перекрестные связи с базы одного транзистора на коллетор другого и наоборот 1. Недостатком известного элемента является постоянное потребление мощности от источника питания, связанное с тем, что транзисторы, составляющие элемент памяти, находятся постоянно в противоположных состояниях (закрыт-открыт). Кроме того, значительная коллекторная емкость, которая появляется из-за подключения к коллектору одного транзистора базы другого и малого напряжения на коллекторе (не более УБЭ открытого транзистора), ограничивает быстродействие устройства. Цель изобретения - повышение быстродействия и снижение потребляемой мощ ности. Поставленная цель достигается тем; что в элемент памяти для накопителя с произвольной выборкой, содержащий шину выборки-записи строки, разрядную шину выборки-записи, шину считывания и первый резистор, первый вывод которого соединен с шиной питания, введены второй резистор и лавинный двухэмиттерный транзистор, коллектор которого соединен с вторым выводом первого резистора, первый эмиттер - с шиной выборки-записи строки, второй эмиттер - с шиной считывания, а база - с первым выводом второго резистора, второй вывод которого соединен с разрядной шиной выборки-записи. На фиг. 1 изображен элемент памяти; на фиг. 2 - эпюры управляющих сигналов в различных режимах. Элемент памяти для накопителя v :;i: iii3вольной выборкой содержит шину 1 выборки-записи строки, разрядную шину 2 аыборки-записи, шину 3 считывания, первый резистор 4, шину 5 питания, второй резистор 6 и лавинный двухэмиттерный транзистор 7, Предлагаемое выполнение элемента памяти обеспечивает его более высокое быстродействие, так как лавинный транзистор принципиально обладает более высоким быстродействием, чем обычный биполярный транзистор. Использование в эле менте памяти одного активного элемента - лавинного транзистора - позволяет упростить схему и получить экономичный элемент памяти, который в одном из состояний НС потребляет мощности от источника питания. Вольтамперная характеристика лавинного транзистора со стороны базы отличается от вольтамперной характеристики обычного биполярного транзистора наличием участка отрицательного дифференциального сопротивления. Благодаря этому, подключив к базе сопротивление, можно получить гистерезисную переключательную характеристику между эмиттером и вторым выводом базового резистора. Для управления элементом памяти используется система сигналов, представленная на фиг. 2, где Ui - потенциал на шине выборки-записи строки, Ug - потенциал на разрядной шине выборки-записи, и - потенциал на шине считывания. Элемент работает следующим образом. Для записи информации на шину 1 выборки-записи строки и разрядную шину 2 выборки-записи подают разнополярные импульсы. При этом потенциал на шине 3 считывания всегда выше, чем на разрядной шине выборки-записи. При считывании потенциал шины 3 считывания понижается и ток (если транзистор находится в проводящем состоянии) переключается из первого эмиттера во второй эмиттер транзистора 7, т. е. в шину 3 считывания. Используемый в элементе памяти активный элемент - лавинный транзистор - обладает по сравнению с обычным биполярным транзистором большим (на 1-2 порядка) быстродействием и большими схемотехническими возможностями.

Т/,

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Элемент памяти | 1989 |

|

SU1679552A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| Накопитель | 1988 |

|

SU1536442A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

ЭЛЕМЕНТ ПАМЯТИ ДЛЯ НАКОПИТЕЛЯ С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ, содержащий шину выборки-записи строки, разрядную шину выборки-записи, шину считывания и первый резистор, первый вывод которого соединен с шиной питания, отличающийся тем, что, с целью повышения быстродействия и снижения потребляемой мош,ности, в него введены второй резистор и лавинный двухэмиттерный транзистор, коллектор которого соединен с вторым выводом первого резистора, первый эмиттер - с шиной выборки-записи строки, второй эмиттер - с шиной считывания, а база - с первым выводом второго резистора, второй вывод которого соединен с разрядной шиной выборки-записи. (Л о О5 j; со 00 fUZ. 1

Vf

Сч.,,1

гап.„Г

t

Сч.,,0

Зап. „о fuz.l

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Валиев К | |||

| А., Орликовский А | |||

| А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| М., «Советское радио, 1979 (прототип) . | |||

Авторы

Даты

1983-12-30—Публикация

1982-02-05—Подача