Mbw

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ПАМЯТИ | 1991 |

|

RU2006967C1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1990 |

|

SU1751816A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Запоминающее устройство | 1990 |

|

SU1751814A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

Изобретение относится к вычислительной технике, в частности к схемам оперативней и сверхоперативной биполярной памяти в интегральном исполнении. Целью изобретения является повышение быстродействия элемента памяти. Для этого в элемент памяти введен развязывающий диод 14с. соответствующими связями. В режиме выборки диод 14 закрывается, а состояние элемента памяти поддерживается током считывания, задаваемым транзистором 11 выборки. При переключении из состояния хранения в состояние выборки весь ток считывания идет на перезаряд емкостей только одного выбранного элемента памяти. 2 ил.

: Ьыб.У

Изобретение относится к вычислительной технике, в частности к схемам оператив- ной и сверхоперативной биполярной памяти в интегральном исполнении. Целью изобретения является повышение быстродействия элемента памяти,

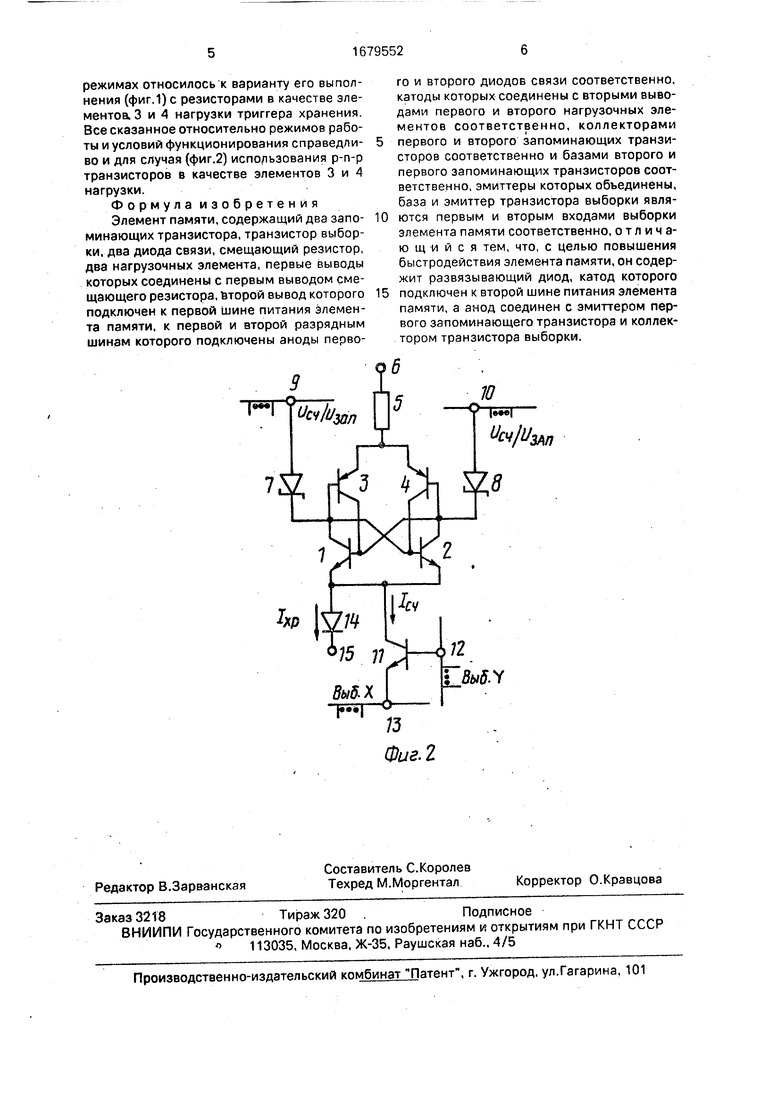

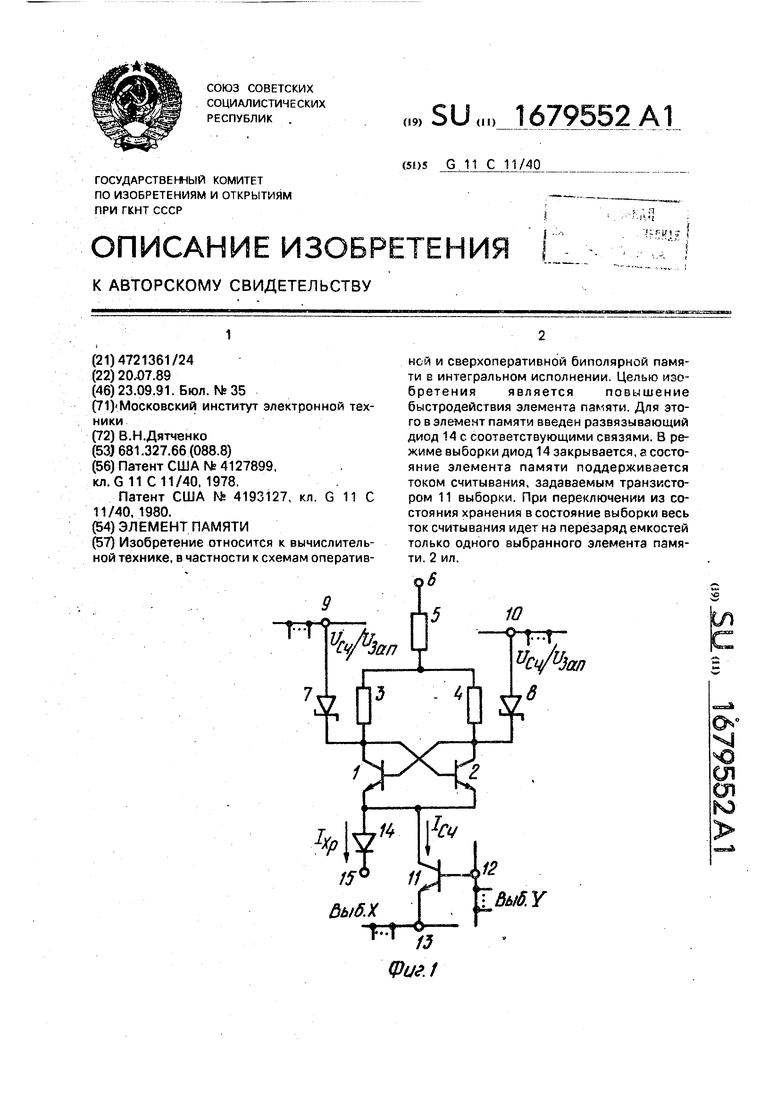

На фиг.1 и 2 представлены варианты электрических схем элемента памяти.

. Элемент памяти содержит первый 1 и второй 2 запоминающие транзисторы, первый 3 и второй 4 нагрузочные элементы, смещающий резистор 5, первую шину.6 питания, первый 7 и второй 8 диоды связи, первую 9 и вторую 10 разрядные шины, транзистор 11 выборки, первый 12 и второй, 13 входы выборки, развязывающий диод 14, вторую шину 15 питания.

Элемент памяти работает следующим образом.

В режиме хранения транзистор 11 не коммутирует ток считывания в триггер хранения, разность потенциалов в котором обеспечивается протеканием тока хранения, задаваемого от второй шины 15 питания через диод 14. Шины питания 6 и 15 могут быть общими для всего массива элементов памяти в накопителе (допускают произвольное объединение по строкам и столбцам в матрице, включая и одновременное обьединение и по строкам, и столбцам).

В режиме выборки в триггер хранения транзистором 11 коммутируется ток считывания. В силу этого за счет падения напря- жения на резисторе 5 потенциалы коллекторов транзисторов 1 и 2 в выбранном элементе памяти становятся меньше, чем в соседних, находящихся в режиме хранения. Соответственно, диод 14 в выбранном элементе памяти запирается, что предотвращает растекание тока считывания в соседние. Запирание диода 14 приводит также и к отключению тока хранения, поступающего в выбранный элемент по второй шине 15 питания, но вместо тока хране- ния в данном режиме разность потенциалов в триггере хранения обеспечивается протеканием тока считывания. Для поддержания разности потенциалов требуется малая доля тока считывания, большая часть которого протекает через диод 7(8) связи в открытом плече триггера. Одной из функций диодов 7(8) связи, таким образом, является фиксация потенциала коллектора открытого транзистора 1(2) с целью предотвращения глубокого насыщения и сохранения высокого быстродействия.

Выбранный элемент памяти может служить для считывания информации из него или для записи. Считывание и запись информации осуществляется по шинам 9 и 10

которые как и шины 6 и 15 питания могут быть общими для всех элементов памяти накопителя, и объединение их по строкам или столбцам может производиться произвольным образом. Режимы считывания или записи определяются соответствующими сигналами по шинам 9 и 10.

Режим считывания определяется тем, что по шинам 9 и 10 на анодах диодов 7 и 8

0 задаются одинаков ые по величине потенциалы считывания.

Для элементов памяти, использующих диоды 7 и 8 для ограничения падения напряжения в нагрузочных элементах 3 и 4 и пред5 отвращения глубокого насыщения транзисторов 1 и 2, известны два режима работы при выборке. В первом из них один диод 7(8) открыт, другой 8(7) заперт. Во втором режиме оба диода 7 и 8 открыты, а

0 логический перепад создается за счет падения напряжения на внутреннем сопротивлении диода 7(8).

Второй режим является предпочтительным, поскольку при нем снимается прису5 щее первому ограничение на величину отношения токов считывания и хранения, являющегося показателем быстродействия. При использовании указанного второго режима выборки возможно использование

0 вместо резисторов 5 в каждом элементе памяти одной цепочки постоянного по величине смещения для строки (или столбца) матрицы элементов памяти.

Разность токов диодов 7 и 8 является

5 сигналом считывания, поступающим на вход усилителя считывания. В элементах памяти, находящихся в режиме хранения, потенциалы на катодах диодов 7 и 8 существенно выше, чем в выбранном, поэ0 тому все диоды 7 и 8 в них заперты и не дают вклад в сигнал считывания,

В режиме записи информации на одной из шин 9 или 10 (в зависимости от рода записываемой информации) потенциал по5 вышается до величины потенциала записи. Это обеспечивает переброс триггера (перезапись информации) в случае, когда потенциал повышается на аноде открытого диода 7(8): с помощью диода 7(8) потенциал логического О повышается до тех пор, пока не

0 сравнивается с потенциалом логической 1, после чего триггер перебрасывается. В случае, когда потенциал повышается на аноде запертого диода 7(8) выбранного элемента памяти, возможно только некоторое

5 повышение потенциала логической 1, переброса триггера не происходит (запись однородной информации в триггер).

Приведенное выше описание работы заявляемого элемента памяти в статических

режимах относилось к варианту его выполнения (фиг,1) с резисторами в качестве элементов, 3 и 4 нагрузки триггера хранения. Все сказанное относительно режимов работы и условий функционирования справедливо и для случая (фиг.2) использования р-п-р транзисторов в качестве элементов 3 и 4 нагрузки.

Формула изобретения Элемент памяти, содержащий два запоминающих транзистора, транзистор выборки, два диода связи, смещающий резистор, два нагрузочных элемента, первые выводы которых соединены с первым выводом смещающего резистора, второй вывод которого подключен к первой шине питания элемента памяти, к первой и второй разрядным шинам которого подключены аноды первоЧР

го и второго диодов связи соответственно, катоды которых соединены с вторыми выводами первого и второго нагрузочных элементов соответственно, коллекторами

первого и второго запоминающих транзисторов соответственно и базами второго и первого запоминающих транзисторов соответственно, эмиттеры которых обьединены, база и эмиттер транзистора выборки являются первым и вторым входами выборки элемента памяти соответственно, отличающийся тем, что, с целью повышения быстродействия элемента памяти, он содержит развязывающий диод, катод которого

подключен к второй шине питания элемента памяти, а анод соединен с эмиттером первого запоминающего транзистора и коллектором транзистора выборки.

ЗАЛ

LW.Y

| Патент США № 4127899, кл.С 11 С 11/40, 1978 | |||

| Патент США № 4193127, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-09-23—Публикация

1989-07-20—Подача