Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных и специализированньис цифровых вычислительных- матин.

Известен многофункциональный погический элемент, содержащий два элемента равнозначности и элемент И, элемент НЕ/ причем каждый элемент равнозначности имеет один информационный и один управляющий входй, выходы элементов равнозначноети подключены к входам элемента И, выход которого соединен с прямым выходом логического элемента и с входом элемента НЕ, выход которого связан с инверсным выходом логического элемента tl

Недостатком известного устройства является низкая надежность схемы ввиду большого числа аппаратных средств, что определяется избыточной функциональной возможностью данного устройства.

Наиболее близким к предлагаемому является многофункциональный логи-,

, ческий элемент, содержащий две информационные шины, шины прямого и инверсного сигналов управления, первый, второй информационные и первый ; коммутирующий транзисторы п па, включенные последовательно, первый, второй нагрузочные транзисторы р-типа, включенные последова- , тельно, двухвходовый логический элемент К-НЕ, два двухвходовых логических элемента ИЛИ-НЕ, тги логических элемента НЕ, сток первого информационного транзистора.п-типа соединен с общей шиной, сток первого нагрузочного транзистора р-типа сО|Е(Динен с шиной источника питания, затворы первого информационного п-типа и первого нагрузочного р-типа транзисторов соединены с пеовой инфоомационно шиной, затворы второго информационного п -типа и второго н.агрузочного р-типа транзисторов соединены с второй инфоомационной шиной, затвор первого коммутирующего транзистора Г1-типа соединен с шиной прямого сигнала управления 2. Недостаток указанного элемента низкая надежность ввиду большого числа компонентов схемы.

Цель изобр етения - повышение надежности многофункционального логического элемента.

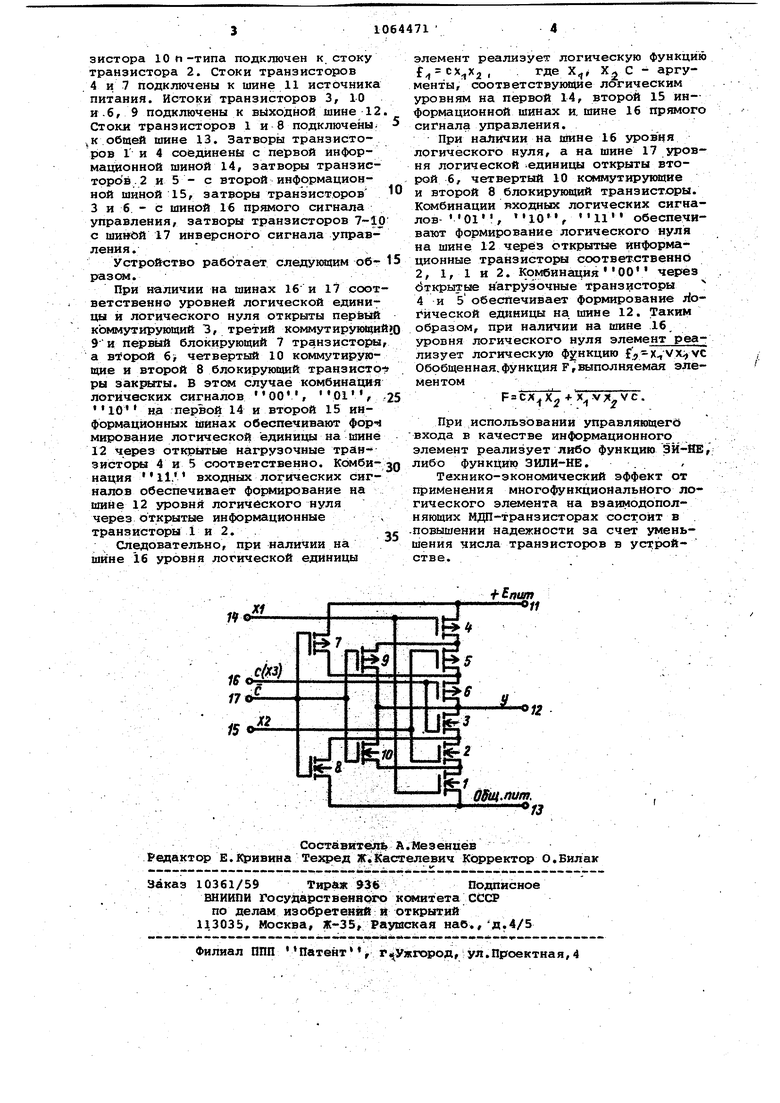

Для достижения поставленной цели в многофункциональный логический элемент наМДП-транэисторах, содержащий первый, второй информационные и первый коммутирующий транзисторы ; , включенные последовательно, первый, второй нагрузочные транзис торы р-типа, включенные последовательно, две информационные шины, шйны прямого и инверсного сигналовуправления, сток первого информационного транзистора п-типа соединен с общей шинойу сток первого нагрузочного транзистора, р-типа соединен с шиной источника питания, затворы первого информационного п-типа и Первого нагрузочного р-типа транзисторов соединены с первой информационной шиной затворы второго.информационного п-типа и второго нагрузочного р-типа транзисторов соеди.нены с второй информационной шиной, затвор первого коммутирующего транзистора п-типа соединен с шиной прямого сигнала управления, введены второй коммутирующий тоанзистоо р-типа: который включен последовательво с первьлм и вторым нагрузочными транзис торами р-типа, первый р-типа и второ .п-типа блокирующие транзисторы, третий р-типа и четвертый п-типа коммутирующие транзисторы, сток первого блокирующего транзистора р-типа соединен с шиной источника питания,- к выходной шине подключены истоки первого, четвертого п-типа и второго, третьего р-типа коммутирующих транзисторов, к общей шине подключён сто второго блокирующего транзистора п.-типа, исток первого блокирую1гего транзистора р-типа подключен к стоку второго коммутирующего транзисторар-типа, сток третьего коммутирунядего транзистЪ а р-типа подключен к стоку второго нагрузочного тра:нзистора р-типа, сток четвертого коммутирующего транзистора и-типа подключен к стоку второго информационного транзистора ti-типа, исток второго блокирующего Транзисторна п-типа подключен к стоку первого коммутирующего транзистора г -типа, затвор второго коммутирунидего транзистора р-типа соединен с вшной прямого сигнала управления, затворы первого , второго п-типа блокирующих и третьего р-типа, четвертого tf-тип% коммутируК)щих транзисторов соединены с шйной. инвэрсного сигнала управления. « На. чертеже П редставлена принципиальная схема предлагаемого многофункционального логического элемента на МДП-транзисторах. .

Первый 1, второй 2 информационные и первый KOMuiyтирующий 3 транзисторы П-типа включены .последовательно, первый 4, второй 5 нагрузочные и второй коммутирующий б транзист:оры р-типа включены последовательно, исток первого блокирующего транзистора

7р-типа подключен к стоку транзистора б, исток второгб блокирующего

8транзистора h-типа подключен к стоку транзистора 3/ сток третьего коммутирующего транзистора/.Э р-типа подключен к стоку транзистора 5, сток четвертого коммутирующего тракзистора 10 n-типа подключен к. стоку транзистора 2. Стоки транзисторов 4 и 7 подключены к шине 11 источника питания. Истоки транзисторов 3, 10 И-б, 9 подключены к выходной шине 12 Стоки транзисторов 1 и 8 подключены/ к общей шине 13. Затворы транзисторов Г и 4 соединены с первой информадаонной шиной 14, затворы транзисторов. 2 и 5 - с второй информационной шиной 15, затворы транзисторов 3 и 6 - с шиной 16 прямого сигнала управления, затворы транзисторов 7-10 с ШИНОЙ 17 инверсного сигнала управления . Устройство работает следующим образом. При наличии на шинах 16 и 17 соот ветственно уровней логической единицы и лЬгического нуля открыты первый коммутирующий 3, третий коммутируюи и 9и первый блокирующий 7 транзисторы а второй б четвертый 10 коммутирующие и второй 8 блокирующий транзисто ры закрыты. В зтом случае комбинация логических сигналов 00, 01% Ю н.а первой 14 и второй 15 ийформацИонных шинах обеспечивают формирование логической единицы на шине 12 через открытые нагрузочные транзисторы 4 и 5 соответственно. Комбинация 11, входных логических сигиалов обеспечивает формирование на шине 12 уровни логического нуля через отк1ялтые информационные транзисторы i и 2. . Следовательно, при наличии на шине 16 уровня логической единицы элемент реализует логическую функцию f cx,,X2, где Х Х С - аргументы, соответствующие логическим уровням на первой 14, второй 15 информационной шинах и, шине 16 прямого сигнала управления. При наличии на пшне 16 уровня логического нуля, а на шине 17 уровня логической единицы открыты второй б, четвертый 10 коммутирующие и второй 8 блокирувмций транзисторы. Комбинации входных логических сигналов 01, «10г 11 обеспечивают формирование логического нуля на шине 12 через открытые информационные транзисторы соответ ствеино 2, 1, 1 и 2. Комбинация 00 через Открытые нагрузочные транзисторы 4 и зобеспечивает формирование lio гйческой единищд на шине 12. Таким образом, при наличии на шине 16. уровня логического нуля элемент реализует логическую функцию , vc Обобщенная.функция F,выполняемая элементом v;(vc. При использовании управляющего входа в качестве информационного элемент реализует либо функцию ЗЙ-ЯЕ, либо функцию ЗИЛИ-НЕ. . Технико-экономический эффект от применения многофункционального логического элемента на взаимодополняющих МДП-транзисторах состоит в Повышении надежности за счет уменьшения числа транзисторов в устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2011 |

|

RU2449469C1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ, содержащий первый, второй информационные и первый коммутирующий транзисторы n-THiia, включенные последовательно, первый, второй нагрузочные транзисторы р-типа, включенные посл едовательно, две информационные шины, шины прямого и инверсного сигналов управления, сток .первого информационного транзистора h-типа соединен с общей шиной, сток первого нагрузочного транзистора р-типа соединен с шиной источника питания, затворы первого информационного п-типа и первого нагрузочного р-типа транзисторов соединены с первой информационной шиной, затворы второго информационного п-типа и второго нагрузочного р-типа транзисторов соединены с второй информационной ШИНОЙ, аатвор .первого коммутирующего транзистора п -типа соединен с шиной прямого сигнала упра.вления, от личающййся т&л, что, с целью повышения надежности, в него введены второй коммутирующий транзистор р-типа, который включен последовательно с первым и вторым нагрузочным транзисторами р-тйпа,первый р-типаи второй п-типа блокирующие транзисторы, третий р-типа и четвертый h-типа коммутирующие транзисторы, сток первого блокирующего транзистора р-типа соединен с шиной источника питания, к выходной шине подключены истоки первого, четвертого п-типа и второго, третьего р-типа коммутирующих транзисторов, к общей шине подключен сток второго блокирующего транзистора п-типа, йсток первого блокирующего тра.нзисi тора р-типа подключен к стоку второго коммутирующего транзистора р-типа, (Л сток третьего коммутирующего транзистора р -типа подключен к стоку второго нагрузочного транзистора р-типа, сток четвертого коммутирующего транзистора п-типа подключен к стоку 2 второго информационного транзистора п-типа, исток второго блокирующего транзистора п-типа подключен к стоку первого, коммутирующего транзистора О) п-типа, затвор второго коммутирующего 0 транзистора р-типа соединен с шиной прямого ригнала управления, затворы первого р-типа, второго л-типа блокирующйхои третьего р-типа, четвертого п-типа ксялмутирующих транзисторов соединены с шиной инверсного .сигналауправления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многофункциональный логический модуль | 1979 |

|

SU851397A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Каталог элементов ХАЗ, 487.130.ЭЗ. | |||

Авторы

Даты

1983-12-30—Публикация

1982-10-06—Подача