того нагрузочных транзисторов р-типа соединены с шиной прямого сигнала управления, затворы коммутирующих

и блокирующих транзисторов соединены с шиной инверсного сигнала управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064471A1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2011 |

|

RU2449469C1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| Преобразователь уровня напряжения | 1987 |

|

SU1466005A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1128379A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Логический элемент Исключающее ИЛИ | 1982 |

|

SU1072264A1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ, содержащий первый, второй и третий информационные транзисторы п-типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы п-типа, включенные после-, довательно, четыре входные шины, шины прямого и инверсного сигнала управления, о т.пл ичающийся тем, что, с целью повышения надеж.ности, первый, второй и третий информационные транзисторы включены между выходной и общей шинами четвертый, пятый и шестой информационные транзисторы включены между выходной и общей шинами, первый, второй и третий нагрузочные транзисторы р-типа включены последовательно между шиной источника питания и выходной шиной, четвертый, пятый и шестой нагрузрчныё; транзисторы р-типа включены последовательно между шиной источника питания и выходной шиной, сток первого блокирующего транзистора р-тйпа соединен с шиной источника питания, а исток подключён к стоку третьего .нагрузочг ного транзистора р-типа, сток первого коммутирующего транзистора р-типа подключен к стоку второго на рузоч- ного транзистора р-типа, а исток соединен со стоком шестого нагрузочного транзистора р-типа,сток второго коммутирующего транзистора р-типа подключен к стоку пятого нагрузочного транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзисГтора п-типа соединен с общей шиной, а исток подключен к стоку первого информационного транзистора п-типа, сток третьего коммутирующего транзистора п-типа подключен к стоку второго информационного транзистора п-типа, а исток - к стоку четвертого информационного транзистора п-типа, сток четвертого коммутирующего транзистора .п-типа подключен к стоку пятого нагрузочно-го транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора п-типа . соединен с общей шиной, а исток подключен к стоку первого информаен ционного транзистора п-типа, сток третьего коммутирующего транзистора п-типа подключен к стоку второго информационного транзистора ,п-типа, а исток - к стоку четвертого информационного транзистора п-типа, сток четвертого коммутирующего транзистора п-типа подключен к стоку пятого информацнон ного транзистора п-типа, а исток соединен с выходнойпшиной, затворы 4i первого нагрузочного транзистора vl р-типа и третьего информационного транзистора п-типа соединены с первой входной шиной, затворы второго нагрузочного транзистора р-типа и второго информационного тра нзистора .п-типа соединены- с второй входной шиной, затворы пятого нагрузочного транзистора р-типа .и пятого информа-ционного транзисшрра гт-типа соединены с третьей входной шиной, затворы шестого нагрузочного транзистора р-типа и четвер.того информационного транзистора п-типа соединены с четвертой входной шиной, затворы первого и шестого информационных тран зисторов п-типа и третьего и четвер

1

Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных и специализированных цифровых вычислительных машин.

Известен многофункциональный логический элемент, содержащий два элeмe тa равнозначности и элемент И элемент НЕ, причем каждый .элемент равнозначности имеет один информационный и один управляющий входы-, входы элементов равнозначности подключены к входам элемента И, выход которого соединен с прямым выходом логического элемента и с входом элемента НЕ, выход которого связан инверсным выходом логического элемента Cl 3.

Недостатком известного устройства является, низкая надежность схемы в виду большого числа аппаратных средств, что определяется избыточной -функциональной возможностью данного устройства.

Наиболее близким к предлагаемому является многофункциональный логический элемент на МДП-транзисторах, содержащий первый, второй и третий информационные транзисторы п-типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы п-типа, включенные последовательно .четыре входные шины .шины

прямого и инверсного сигнала управления 2 .

Недостаток указанного элемента низкая надежность в виду большого числа компонентов схемы.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что в многофункциональном логическом элементе на МДЦ-рранзисторах, содержащем первый, второй и третий информационные транзисторы п-типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы п-типа, включенные последовательно, четыре .входные шины, шины прямого и инверсного сигнала; управления, первый, I второй и третий информационные транЬисторы включены между выходной и общей шинами, четвертый, пятый и шестой информационные транзисторы включены между выходной и общей, шинами, первый второй и третий нагрузочные транзисторы р-типа включены последовательно между шиной источника п-итания и выходной шиной, четвертый, пятыйи шестой нагрузочные транзисторы р-типа включены последовательно между шиной источника питания и выходной шиной, сток первого блокирующего транзистора р-типа соединен с

0 шиной источника питания, а исток

подключен к стоку третьего нагрузочного транзистора р-типа, сток первого коммутирающего транзистора р-типа подключен к стоку второго нагрузочно5 го транзистора р-типа а исток соединен со стоком шестого нагрузочного транзистора р-типа,сток второго коммутирующего транзистора р-типа подключен к стоку пятого нагрузочного транз-истора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора п-типа соединен с общей шиной, а исток подключен к cTOf ку первого информационного транзистора п-типа, сток третьего коммутирунадего транзистора п-типа подключен к . стоку второго информационного транзистора п -типа, -а исток - к стоку четвертого информационного транзистора п-типа, сток четвертого

0 коммутирующего транзистора г -типа подключен к стоку пятого нагрузочного транзистора р-типа, а исток соединен с вьаходной шиной, сток второго блокирующего транзистора п-типа

5 соединен с общей шиной, а исток подключен к стоку первого информационного транзистора п-типа, сток третьш о коммутирующего транзистора л-типа подключен к стоку второго

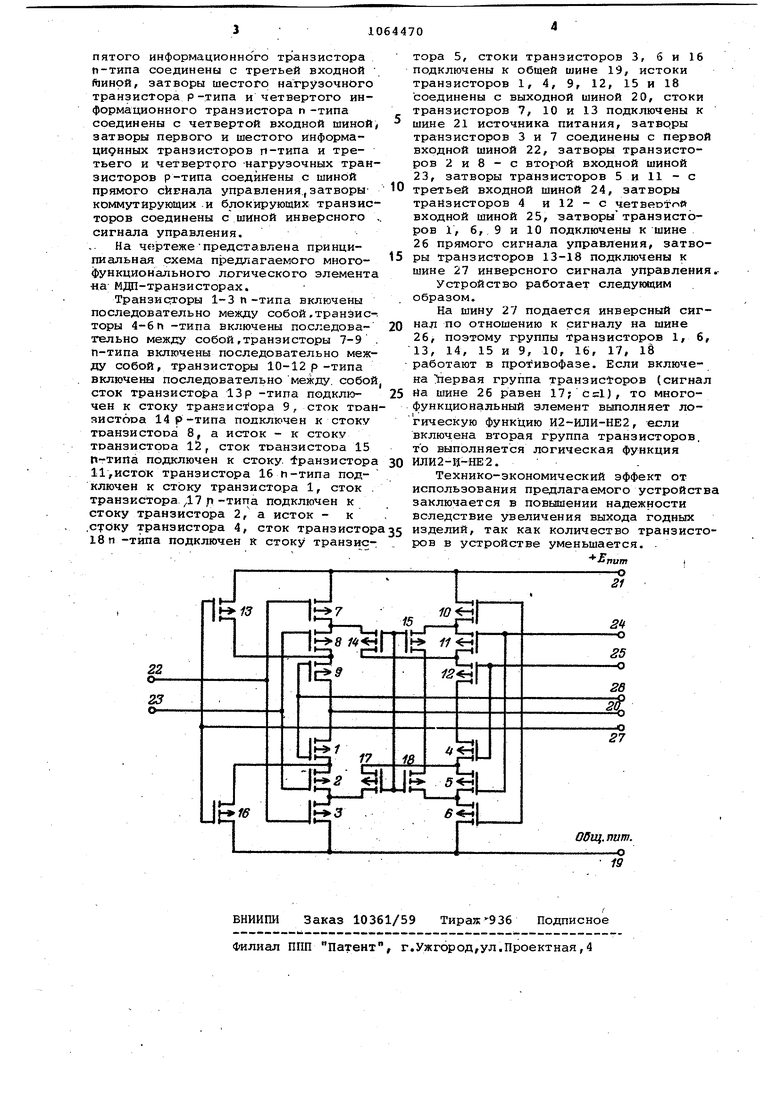

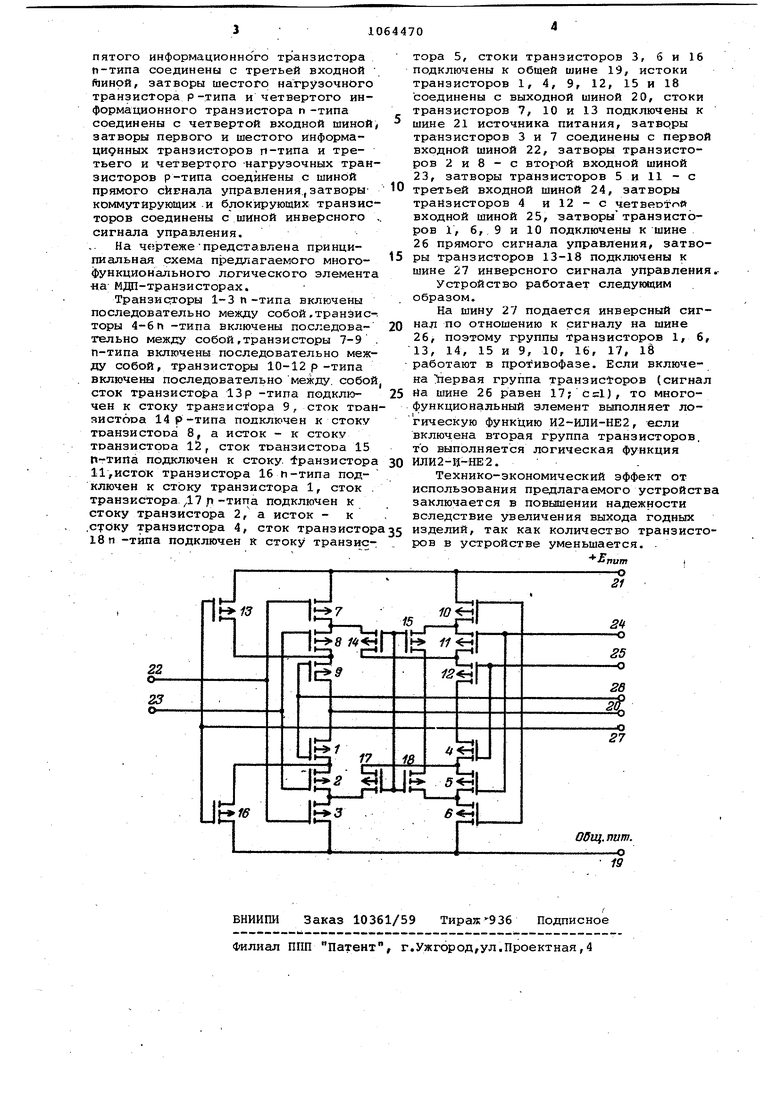

0 информационного транзистора п-типа, а исток - к CTORy четвертого информационного транзистора п-типа, сток четвертого коммутирующего транзистора п-типа подключен к стоку пятого информационного транзистора п-типа/ а исток соединен с выходной шиной, затворы первого нагрузочного транзистора р-типа и третьего информационного транзистора п-типа соединены с первой входной шиной,,затворы второго нагрузочного транзистора р-типа и второго информационного транзистора п-типа соединены с второй входной шиной, затворы пятого нагрузочного транзистора р-типа и пятого информационного транзистора п-типа соединены с третьей входной йинрй, затворы шестого нагрузочного транзистора р-типа и четвертого информационного транзистора п-типа соединены с четвертой входной шиной затворы первого и шестого информацифнных транзисторов п-типа и третьего и четвертого -нагрузочных тран зисторов р-типа соединены с шиной прямого сйЕяала управления., затворыкоммутирующих .и блокирующих транзис торов соединены с шиной инверсного сигнала управления. На ч«фтежеПредставлена принципиальная схема предлагаемого многофункционального логического элемент «а МДП-транзисторах. Транзисторы 1-3 п-типа включены последовательно между собой.транзис торы 4-6п -типа включены последовагельно между собой,транзисторы 7-9 п-типа включены последовательно меж ду собой, транзисторы 10-12 р -типа включены последовательно между, собо сток транзистора 13р -типа подключен к стоку транзистора 9, сток тоа аистбоа 14 р-типа подключен к стоку транзистора 8, а исток - к стоку транзистора IS, сток тоанзистооа 15 П-типа подключен к стоку, транзистор 11,исток транзистора 16 м-типа подключен к стоку транзистора 1, сток транзистора. Д7р-типа подключен к стоку транзистора 2, а исток - к ,стоку транзистора 4, сток транзистор 18п -типа подключен к стоку транзис

J

п

2f тора 5, стоки транзисторов 3, б и 16 подключены к общей и;ине 19, истоки транзисторов 1, 4, 9, 12, 15 и 18 соединены с выходной шиной 20, стоки транзисторов 7, 10 и 13 подключены к шине 21 источника питания, затврры транзисторов 3 и 7 соединены с первой входной шиной 22, затворы транзисторов 2 и 8 - с второй входной шиной 23, затворы транзисторов 5 и 11 - с третьей входной шиной 24, затворы транзисторов 4 и 12 - с четвеото входной шиной 25, затворытранзисторов 1, 6, 9 и 10 подключены к шине 26 прямого сигнала управления, затворы транзисторов 13-18 подключены к шине 27 инверсного сигнала управления. Устройство работает следующим образом. На шину 27 подается инверсный сигнал по отношению к сигналу на шине 26, поэтому г-руппы Транзисторов 1, 6, 13, 14, 15 и 9, 10, 16, 17, 18 работают в про ивофазе. Если включена Угервая группа транзис оров (сигнал На шине 26 равен 17; ), то многофункциональный элемент выполняет логическую функцию И2-ИЛИ-НЕ2, если включена вторая группа транзисторов, то выполняется логическая функция ИЛИ2-1К-НЕ2. Технико-экономический эффект от использования предлагаемого устройства заключается в повышении надежности вследствие увеличения выхода годных изделий, так как количество транзисторов в устройстве уменьшается. . Елит I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многофункциональный логический модуль | 1979 |

|

SU851397A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

Авторы

Даты

1983-12-30—Публикация

1982-09-27—Подача