Изобретение относится к вычислительной технике и может быть использовано для генерации тестовых последовательностей при функциональном контроле оперативных запоминающих устройств, а также для задания тестовых последовательностей других цифровых схем, генерации потоков псевдослучайных чисел с равномерным законом распределения.

Целью изобретения является повышение производительности контроля и расширение функциональных возможностей устройства за счет обеспечения контроля любых типов логических схем.

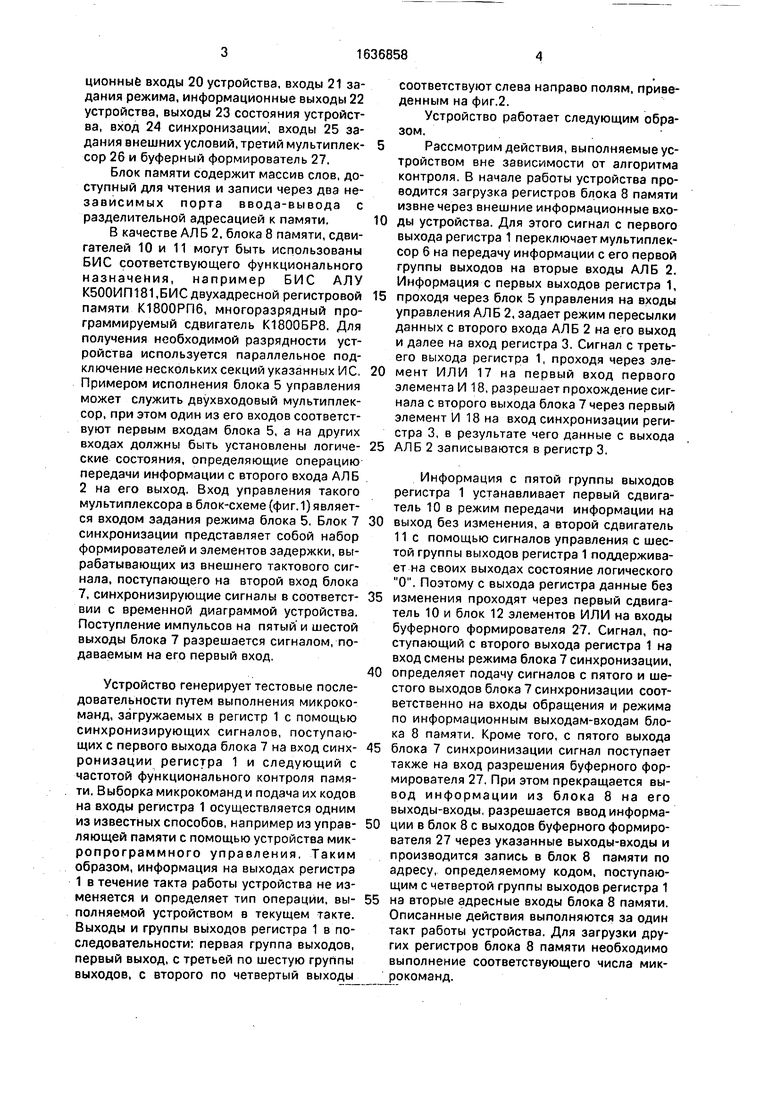

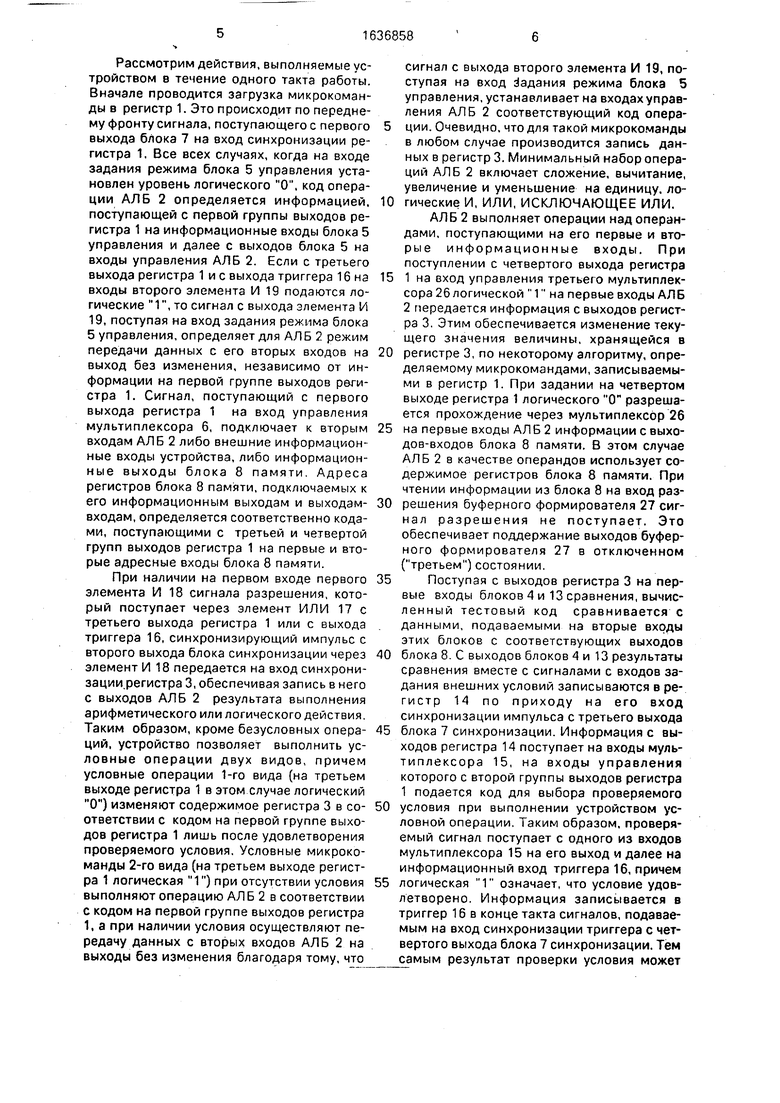

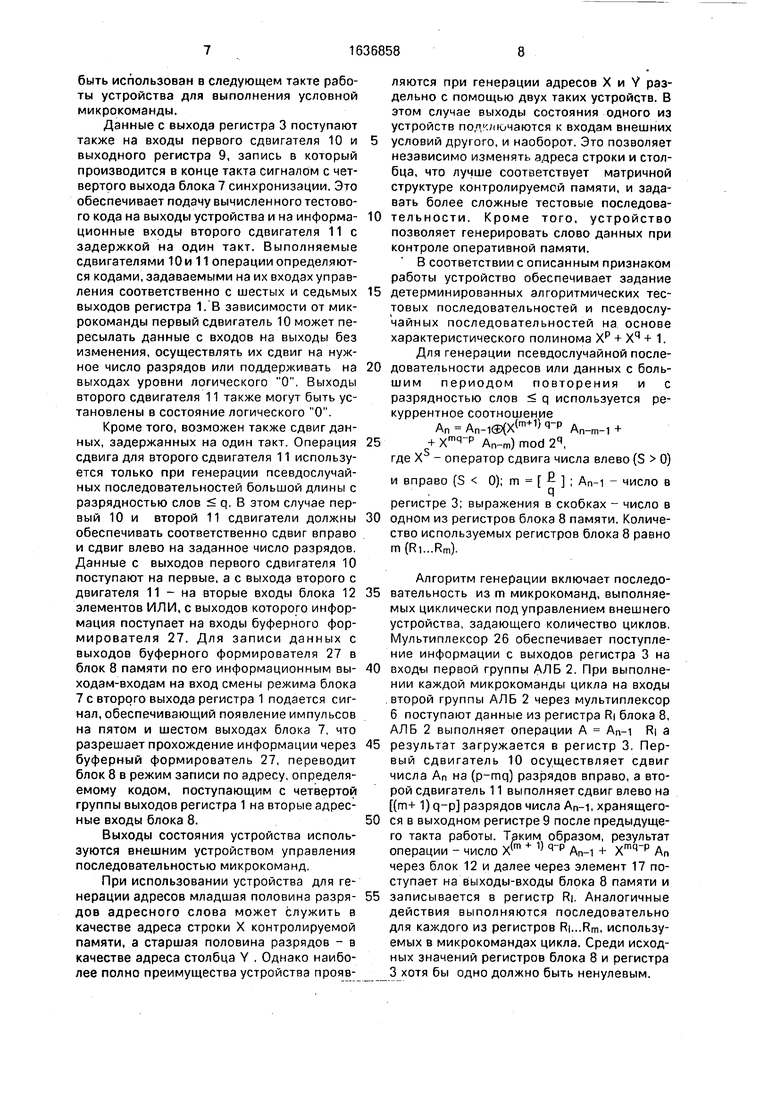

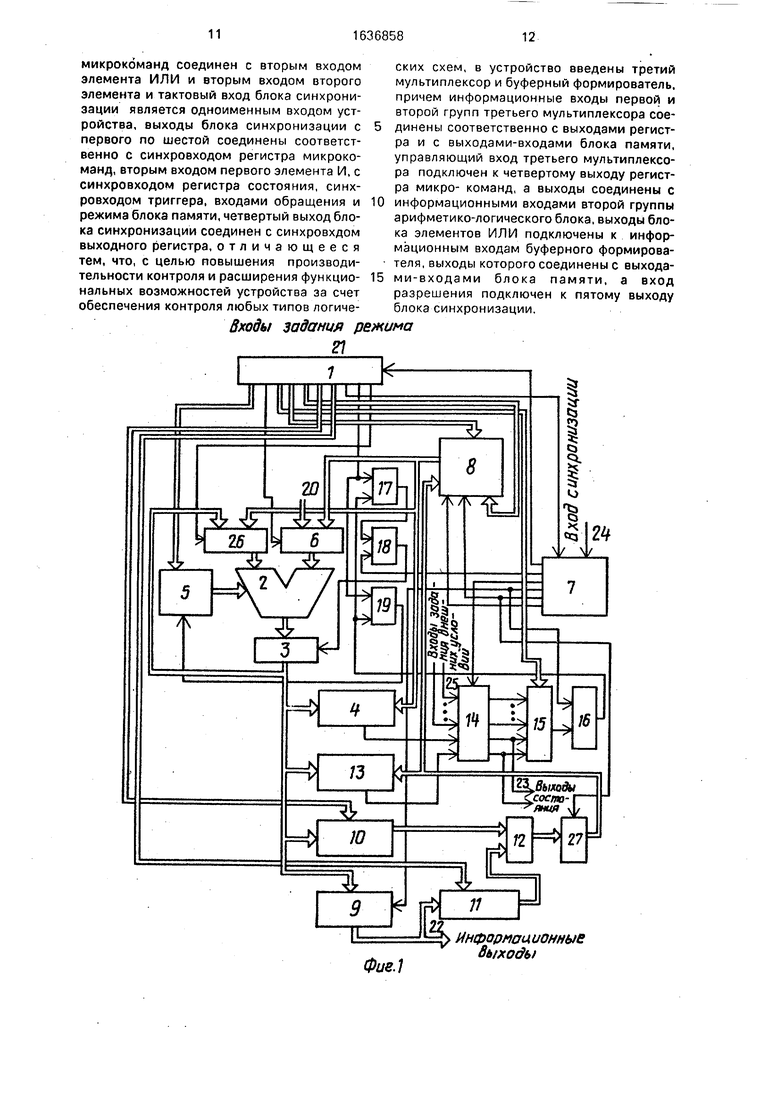

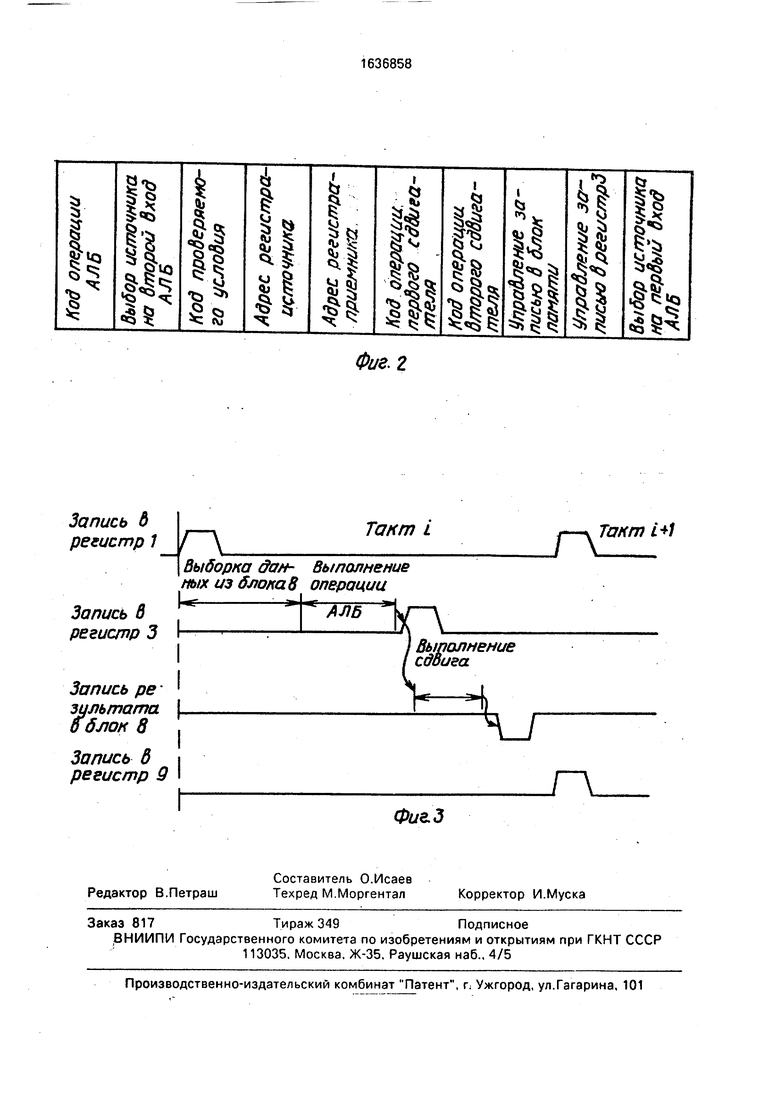

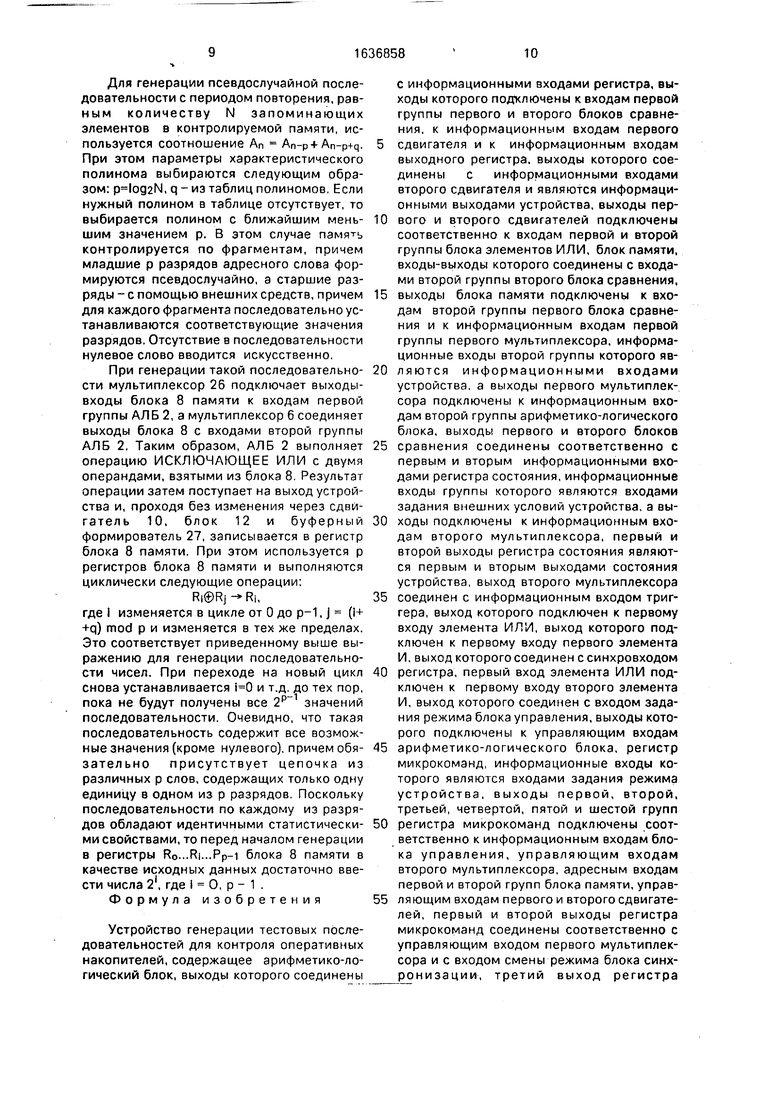

На фиг. 1 представлена структурная схема устройства; на фиг 2 - структура слова микрокоманды, выполняемой устройством; на фиг. 3 - временная диаграмма работы устройства.

Устройство содержит регистр 1 микрокоманд, арифметико-логический блок (АЛБ) 2, регистр 3, первый блок 4 сравнения, блок 5 управления, первый мультиплексор 6, блок 7 синхронизации, блок 8 памяти, выходной регистр 9, первый 10 и второй 11 сдвигатели, блок 12 элементов ИЛИ, второй блок 13 сравнения, регистр 14 состояния, второй мультиплексор 15, триггер 16, элемент ИЛИ 17, элементы И 18 и 19, информаONOJ О 00 СЛ 00

ционныб входы 20 устройства, входы 21 задания режима, информационные выходы 22 устройства, выходы 23 состояния устройства, вход 24 синхронизации, входы 25 задания внешних условий, третий мультиплексор 26 и буферный формирователь 27.

Блок памяти содержит массив слов, доступный для чтения и записи через два независимых порта ввода-вывода с разделительной адресацией к памяти.

В качестве АЛ Б 2, блока 8 памяти, сдви- гателей 10 и 11 могут быть использованы БИС соответствующего функционального назначения, например БИС АЛУ К500ИП181,БИС двухадресной регистровой памяти К1800РП6, многоразрядный программируемый сдвигатель К1800БР8. Для получения необходимой разрядности устройства используется параллельное подключение нескольких секций указанных ИС, Примером исполнения блока 5 управления может служить двухвходовый мультиплексор, при этом один из его входов соответствуют первым входам блока 5, а на других входах должны быть установлены логические состояния, определяющие операцию передачи информации с второго входа АЛ Б 2 на его выход. Вход управления такого мультиплексора в блок-схеме (фиг. является входом задания режима блока 5. Блок 7 синхронизации представляет собой набор формирователей и элементов задержки, вырабатывающих из внешнего тактового сигнала, поступающего на второй вход блока 7, синхронизирующие сигналы в соответствии с временной диаграммой устройства. Поступление импульсов на пятый и шестой выходы блока 7 разрешается сигналом, подаваемым на его первый вход.

Устройство генерирует тестовые последовательности путем выполнения микрокоманд, загружаемых в регистр 1 с помощью синхронизирующих сигналов, поступающих с первого выхода блока 7 на вход синхронизации регистра 1 и следующий с частотой функционального контроля памяти. Выборка микрокоманд и подача их кодов на входы регистра 1 осуществляется одним из известных способов, например из управляющей памяти с помощью устройства микропрограммного управления. Таким образом, информация на выходах регистра 1 в течение такта работы устройства не изменяется и определяет тип операции, выполняемой устройством в текущем такте. Выходы и группы выходов регистра 1 в последовательности: первая группа выходов, первый выход, с третьей по шестую группы выходов, с второго по четвертый выходы

соответствуют слева направо полям, приведенным на фиг.2.

Устройство работает следующим образом.

Рассмотрим действия, выполняемые устройством вне зависимости от алгоритма контроля. В начале работы устройства проводится загрузка регистров блока 8 памяти извне через внешние информационные входы устройства. Для этого сигнал с первого выхода регистра 1 переключает мультиплексор 6 на передачу информации с его первой группы выходов на вторые входы АЛ Б 2. Информация с первых выходов регистра 1,

проходя через блок 5 управления на входы управления АЛ Б 2, задает режим пересылки данных с второго входа АЛ Б 2 на его выход и далее на вход регистра 3. Сигнал с третьего выхода регистра 1, проходя через элемент ИЛИ 17 на первый вход первого элемента И 18, разрешает прохождение сигнала с второго выхода блока 7 через первый элемент И 18 на вход синхронизации регистра 3, в результате чего данные с выхода

АЛБ 2 записываются в регистр 3.

Информация с пятой группы выходов регистра 1 устанавливает первый сдвигатель 10 в режим передачи информации на

выход без изменения, а второй сдвигатель 11 с помощью сигналов управления с шестой группы выходов регистра 1 поддерживает на своих выходах состояние логического О. Поэтому с выхода регистра данные без

изменения проходят через первый сдвигатель 10 и блок 12 элементов ИЛИ на входы буферного формирователя 27. Сигнал, поступающий с второго выхода регистра 1 на вход смены режима блока 7 синхронизации,

определяет подачу сигналов с пятого и шестого выходов блока 7 синхронизации соответственно на входы обращения и режима по информационным выходам-входам блока 8 памяти. Кроме того, с пятого выхода

блока 7 синхроинизации сигнал поступает также на вход разрешения буферного формирователя 27. При этом прекращается вывод информации из блока 8 на его выходы-входы, разрешается вводинформации в блок 8 с выходов буферного формирователя 27 через указанные выходы-входы и производится запись в блок 8 памяти по адресу, определяемому кодом, поступающим с четвертой группы выходов регистра 1

на вторые адресные входы блока 8 памяти. Описанные действия выполняются за один такт работы устройства. Для загрузки других регистров блока 8 памяти необходимо выполнение соответствующего числа микрокоманд.

Рассмотрим действия, выполняемые устройством в течение одного такта работы. Вначале проводится загрузка микрокоманды в регистр 1. Это происходит по переднему фронту сигнала, поступающего с первого выхода блока 7 на вход синхронизации регистра 1, Все всех случаях, когда на входе задания режима блока 5 управления установлен уровень логического О, код операции АЛБ 2 определяется информацией, поступающей с первой группы выходов регистра 1 на информационные входы блока 5 управления и далее с выходов блока 5 на входы управления АЛБ 2. Если с третьего выхода регистра 1 и с выхода триггера 16 на входы второго элемента И 19 подаются логические 1, то сигнал с выхода элемента И 19, поступая на вход задания режима блока 5 управления, определяет для АЛБ 2 режим передачи данных с его вторых входов на выход без изменения, независимо от информации на первой группе выходов регистра 1. Сигнал, поступающий с первого выхода регистра 1 на вход управления мультиплексора 6, подключает к вторым входам АЛБ 2 либо внешние информационные входы устройства, либо информационные выходы блока 8 памяти. Адреса регистров блока 8 памяти, подключаемых к его информационным выходам и выходам- входам, определяется соответственно кодами, поступающими с третьей и четвертой групп выходов регистра 1 на первые и вторые адресные входы блока 8 памяти.

При наличии на первом входе первого элемента И 18 сигнала разрешения, который поступает через элеме-нт ИЛИ 17 с третьего выхода регистра 1 или с выхода триггера 16, синхронизирующий импульс с второго выхода блока синхронизации через элемент И 18 передается на вход синхрони- зации.регистра 3, обеспечивая запись в него с выходов АЛБ 2 результата выполнения арифметического или логического действия. Таким образом, кроме безусловных операций, устройство позволяет выполнить условные операции двух видов, причем условные операции 1-го вида (на третьем выходе регистра 1 в этом случае логический О) изменяют содержимое регистра 3 в соответствии с кодом на первой группе выходов регистра 1 лишь после удовлетворения проверяемого условия. Условные микрокоманды 2-го вида (на третьем выходе регистра 1 логическая 1) при отсутствии условия выполняют операцию АЛ Б 2 в соответствии с кодом на первой группе выходов регистра 1, а при наличии условия осуществляют передачу данных с вторых входов АЛБ 2 на выходы без изменения благодаря тому, что

сигнал с выхода второго элемента И 19, поступая на вход Задания режима блока 5 управления, устанавливает на входах управления АЛБ 2 соответствующий код операции. Очевидно, что для такой микрокоманды в любом случае производится запись данных в регистр 3. Минимальный набор операций АЛБ 2 включает сложение, вычитание, увеличение и уменьшение на единицу, ло0 гические И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ.

АЛБ 2 выполняет операции над операндами, поступающими на его первые и вторые информационные входы. При поступлении с четвертого выхода регистра

5 1 на вход управления третьего мультиплексора 26 логической 1 на первые входы АЛБ 2 передается информация с выходов регистра 3. Этим обеспечивается изменение текущего значения величины, хранящейся в

0 регистре 3, по некоторому алгоритму, определяемому микрокомандами,записываемыми в регистр 1. При задании на четвертом выходе регистра 1 логического О разрешается прохождение через мультиплексор 26

5 на первые входы АЛБ 2 информации с выходов-входов блока 8 памяти. В этом случае АЛБ 2 в качестве операндов использует содержимое регистров блока 8 памяти. При чтении информации из блока 8 на вход раз0 решения буферного формирователя 27 сигнал разрешения не поступает. Это обеспечивает поддержание выходов буферного формирователя 27 в отключенном (третьем) состоянии.

5 Поступая с выходов регистра 3 на первые входы блоков 4 и 13 сравнения, вычисленный тестовый код сравнивается с данными, подаваемыми на вторые входы этих блоков с соответствующих выходов

0 блока 8. С выходов блоков 4 и 13 результаты сравнения вместе с сигналами с входов задания внешних условий записываются в регистр 14 по приходу на его вход синхронизации импульса с третьего выхода

5 блока 7 синхронизации. Информация с выходов регистра 14 поступает на входы мультиплексора 15, на входы управления которого с второй группы выходов регистра 1 подается код для выбора проверяемого

0 условия при выполнении устройством условной операции. Таким образом, проверяемый сигнал поступает с одного из входов мультиплексора 15 на его выход и далее на информационный вход триггера 16, причем

5 логическая 1 означает, что условие удовлетворено. Информация записывается в триггер 16 в конце такта сигналов, подаваемым на вход синхронизации триггера с четвертого выхода блока 7 синхронизации. Тем самым результат проверки условия может

быть использован в следующем такте работы устройства для выполнения условной микрокоманды.

Данные с выхода регистра 3 поступают также на входы первого сдвигателя 10 и выходного регистра 9, запись в который производится в конце такта сигналом с четвертого выхода блока 7 синхронизации. Это обеспечивает подачу вычисленного тестового кода на выходы устройства и на информа- ционные входы второго сдвигателя 11 с задержкой на один такт. Выполняемые сдвигателями 10 и 11 операции определяются кодами, задаваемыми на их входах управления соответственно с шестых и седьмых выходов регистра 1. В зависимости от микрокоманды первый сдвигатель 10 может пересылать данные с входов на выходы без изменения, осуществлять их сдвиг на нужное число разрядов или поддерживать на выходах уровни логического О. Выходы второго сдвигателя 11 также могут быть установлены в состояние логического О.

Кроме того, возможен также сдвиг данных, задержанных на один такт. Операция сдвига для второго сдвигателя 11 используется только при генерации псевдослучайных последовательностей большой длины с разрядностью слов q, В этом случае первый 10 и второй 11 сдвигатели должны обеспечивать соответственно сдвиг вправо и сдвиг влево на заданное число разрядов. Данные с выходов первого сдвигателя 10 поступают на первые, а с выхода второго с двигателя 11 - на вторые входы блока 12 элементов ИЛИ, с выходов которого информация поступает на входы буферного формирователя 27. Для записи данных с выходов буферного формирователя 27 в блок 8 памяти по его информационным вы- ходам-входам на вход смены режима блока 7 с второго выхода регистра 1 подается сигнал, обеспечивающий появление импульсов на пятом и шестом выходах блока 7, что разрешает прохождение информации через буферный формирователь 27, переводит блок 8 в режим записи по адресу, определяемому кодом, поступающим с четвертой группы выходов регистра 1 на вторые адресные входы блока 8.

Выходы состояния устройства используются внешним устройством управления последовательностью микрокоманд.

При использовании устройства для генерации адресов младшая половина разря- дов адресного слова может служить в качестве адреса строки X контролируемой памяти, а старшая половина разрядов - в качестве адреса столбца Y , Однако наиболее полно преимущества устройства проявляются при генерации адресов X и Y раздельно с помощью двух таких устройств. В этом случае выходы состояния одного из устройств пол ючаются к входам внешних условий другого, и наоборот. Это позволяет независимо изменять адреса строки и столбца, что лучше соответствует матричной структуре контролируемой памяти, и задавать более сложные тестовые последовательности. Кроме того, устройство позволяет генерировать слово данных при контроле оперативной памяти.

В соответствии с описанным признаком работы устройство обеспечивает задание детерминированных алгоритмических тестовых последовательностей и псевдослучайных последовательностей на основе характеристического полинома Хр + Xq + 1.

Для генерации псевдослучайной последовательности адресов или данных с большим периодом повторения и с разрядностью слов q используется рекуррентное соотношение

An An-i®(X{m+1) Ч-Р An-m-l + + Xmcrp An-m) mod 2q, где Xs - оператор сдвига числа влево (S 0)

и вправо (S 0); m Ј ; Ап-1 - число в

q

регистре 3; выражения в скобках - число в одном из регистров блока 8 памяти. Количество используемых регистров блока 8 равно m(Ri...Rm).

Алгоритм генерации включает последовательность из m микрокоманд, выполняемых циклически под управлением внешнего устройства, задающего количество циклов, Мультиплексор 26 обеспечивает поступление информации с выходов регистра 3 на входъ первой группы АЛБ 2. При выполнении каждой микрокоманды цикла на входы второй группы АЛБ 2 через мультиплексор 6 поступают данные из регистра RI блока 8, АЛБ 2 выполняет операции А Ап-1 RI a результат загружается в регистр 3. Первый сдвигатель 10 осуществляет сдвиг числа An на (p-mq) разрядов вправо, а второй сдвигатель 11 выполняет сдвиг влево на t(m+ 1) q-p разрядов числа Ап-1, хранящегося в выходном регистре 9 после предыдущего такта работы. Таким образом, результат операции - число Х(т + 1) Ап-1 + An через блок 12 и далее через элемент 17 поступает на выходы-входы блока 8 памяти и записывается в регистр RI. Аналогичные действия выполняются последовательно для каждого из регистров Ri...Rm, используемых в микрокомандах цикла. Среди исходных значений регистров блока 8 и регистра 3 хотя бы одно должно быть ненулевым.

Для генерации псевдослучайной последовательности с периодом повторения, рав- ным количеству N запоминающих элементов в контролируемой памяти, используется соотношение An An-p + An-p+q. При этом параметры характеристического полинома выбираются следующим образом: p log2N, q - из таблиц полиномов. Если нужный полином в таблице отсутствует, то выбирается полином с ближайшим меньшим значением р. В этом случае память контролируется по фрагментам, причем младшие р разрядов адресного слова формируются псевдослучайно, а старшие разряды - с помощью внешних средств, причем для каждого фрагмента последовательно устанавливаются соответствующие значения разрядов. Отсутствие в последовательности нулевое слово вводится искусственно.

При генерации такой последовательности мультиплексор 26 подключает выходы- входы блока 8 памяти к входам первой группы АЛБ 2, а мультиплексор 6 соединяет выходы блока 8 с входами второй группы АЛБ 2. Таким образом, АЛБ 2 выполняет операцию ИСКЛЮЧАЮЩЕЕ ИЛИ с двумя операндами, взятыми из блока 8. Результат операции затем поступает на выход устройства и, проходя без изменения через сдви- гатель 10, блок 12 и буферный формирователь 27, записывается в регистр блока 8 памяти. При этом используется р регистров блока 8 памяти и выполняются циклически следующие операции:

Ri©Rj ,

где i изменяется в цикле от 0 до р-1, j (i+ +q) mod p и изменяется в тех же пределах. Это соответствует приведенному выше выражению для генерации последовательности чисел. При переходе на новый цикл снова устанавливается и т.д. до тех пор, пока не будут получены все значений последовательности. Очевидно, что такая последовательность содержит все возможные значения (кроме нулевого), причем обязательно присутствует цепочка из различных р слов, содержащих только одну единицу в одном из р разрядов. Поскольку последовательности по каждому из разрядов обладают идентичными статистическими свойствами, то перед началом генерации в регистры R0...Ri...Pp-i блока 8 памяти в качестве исходных данных достаточно ввести числа 21, где I О, р - 1 .

Формула изобретения

Устройство генерации тестовых последовательностей для контроля оперативных накопителей, содержащее арифметико-логический блок, выходы которого соединены

с информационными входами регистра, выходы которого подключены к входам первой группы первого и второго блоков сравнения, к информационным входам первого

сдвигателя и к информационным входам выходного регистра, выходы которого соединены с информационными входами второго сдвигателя и являются информационными выходами устройства, выходы пер0 вого и второго сдвигателей подключены соответственно к входам первой и второй группы блока элементов ИЛИ, блок памяти, входы-выходы которого соединены с входами второй группы второго блока сравнения,

5 выходы блока памяти подключены к входам второй группы первого блока сравнения и к информационным входам первой группы первого мультиплексора, информационные входы второй группы которого яв0 ляются информационными входами устройства, а выходы первого мультиплексора подключены к информационным входам второй группы арифметико-логического блока, выходы первого и второго блоков

5 сравнения соединены соответственно с первым и вторым информационными входами регистра состояния, информационные входы группы которого являются входами задания внешних условий устройства, а вы0 ходы подключены к информационным входам второго мультиплексора, первый и второй выходы регистра состояния являются первым и вторым выходами состояния устройства, выход второго мультиплексора

5 соединен с информационным входом триггера, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к первому входу первого элемента И, выход которого соединен с синхровходом

0 регистра, первый вход элемента ИЛИ подключен к первому входу второго элемента И, выход которого соединен с входом задания режима блока управления, выходы которого подключены к управляющим входам

5 арифметико-логического блока, регистр микрокоманд, информационные входы которого являются входами задания режима устройства, выходы первой, второй, третьей, четвертой, пятой и шестой групп

0 регистра микрокоманд подключены соответственно к информационным входам блока управления, управляющим входам второго мультиплексора, адресным входам первой и второй групп блока памяти, управ5 ляющим входам первого и второго сдвигателей, первый и второй выходы регистра микрокоманд соединены соответственно с управляющим входом первого мультиплексора и с входом смены режима блока синхронизации, третий выход регистра

микрокоманд соединен с вторым входом элемента ИЛИ и вторым входом второго элемента и тактовый вход блока синхронизации является одноименным входом устройства, выходы блока синхронизации с первого по шестой соединены соответственно с синхровходом регистра микрокоманд, вторым входом первого элемента И, с синхровходом регистра состояния, синхровходом триггера, входами обращения и 10 информационными входами второй группы

режима блока памяти, четвертый выход блока синхронизации соединен с синхровхдом выходного регистра, отличающееся тем, что, с целью повышения производительности контроля и расширения функцио- 15 нальных возможностей устройства за счет обеспечения контроля любых типов логичеВходы задания режима 21

4

арифметико-логического блока, выходы блока элементов ИЛИ подключены к информационным входам буферного формирователя, выходы которого соединены с еыхода- ми-входами блока памяти, а вход разрешения подключен к пятому выходу блока синхронизации.

ских схем, в устройство введены третий мультиплексор и буферный формирователь. причем информационные входы первой и второй групп третьего мультиплексора соединены соответственно с выходами регистра и с выходами-входами блока памяти, управляющий вход третьего мультиплексора подключен к четвертому выходу регистра микро- команд, а выходы соединены с

арифметико-логического блока, выходы блока элементов ИЛИ подключены к информационным входам буферного формирователя, выходы которого соединены с еыхода- ми-входами блока памяти, а вход разрешения подключен к пятому выходу блока синхронизации.

Фие.1

Информационные Выходы

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство генерации адресной последовательности для контроля оперативных накопителей | 1987 |

|

SU1513524A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

Изобретение относится к вычислительной технике и может быть использовано для генерации тестовых последовательностей при функциональном контроле оперативных запоминающих устройств. Устройство может быть также использовано для задания тестовых последовательностей других цифровых схем, генерации потоков псевдослучайных чисел с равномерным законом распределения. Целью изобретения является повышение производительности контроля и расширение функциональных возможностей устройства за счет обеспечения контроля любых типов логических схем. Устройство содержит регистр микрокоманд, арифметико-логический блок, регистр, первый и второй блоки сравнения, блок управления, первый, второй и третий мультиплексоры, блок синхронизации, блок памяти, выходной регистр, первый и второй сдвигатели, блок элементов ИЛИ. регистр состояния, триггер, элемент ИЛИ, первый и второй элементы И, буферный формирователь. Устройство обеспечивает программную генерацию псевдослучайных адресных последовательностей, длина которых соответствует информационной емкости контролируемого накопителя, причем алгоритмы формирования данных и сигнала записи считывания аналогичны известным линейным тестам. 3 ил.

г

Такт

Выборка дан- Выполнение из блока В операции

АЛБ

Запись б регистр 9

Такт L

Г

Такт

Выполнение сдвига

г

| Патент США № 4293950, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Устройство генерации адресной последовательности для контроля оперативных накопителей | 1987 |

|

SU1513524A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-03-23—Публикация

1989-01-05—Подача