О- О

В)(.Пр.

-3

Ш

т

505)52 22232 25

ффф

«w

ад «в

в

21

11

ти -o

с

I

15 3 35J73B

(Л

сд

со

4 01

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| Модуль однородной вычислительной структуры | 1984 |

|

SU1359782A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1443000A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

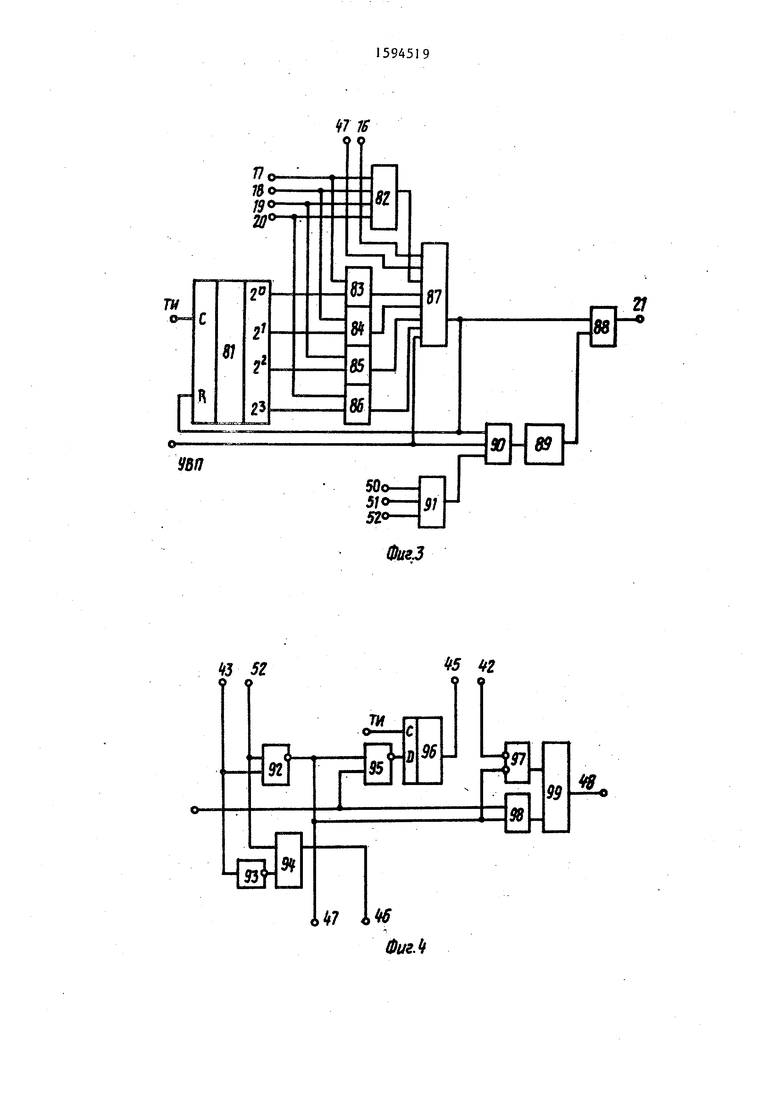

Изобретение относится к вычислительной технике и может быть использовано в качестве базового элемента при построении однородных вычислительных сред. Целью изобретения является расширение функциональных возможностей за счет возможности динамической реконфигурации информационных потоков. Устройство содержит блок 1 управления вычислениями, двунаправленный коммутатор 2, входные мультиплексоры 3,4, триггер 5, арифметико-логический блок 6, мультиплексоры 7,8, блок 9 управления дополнительным каналом транзита, триггер 10, блок 11 модификации адреса, триггер 12, мультиплексор 13, демультиплексоры 14,15. Поставленная цель достигается введением новых элементов и связей. 6 ил.

3

П

Изобретение относится к вычислительной технике и может быть использовано в качестве базового элемента При построении однородных вычислительных сред.

Целью изобретения является расширение функциональных возможностей за ;;чет возможности динамической реконфигурации информационных потоков. ,п

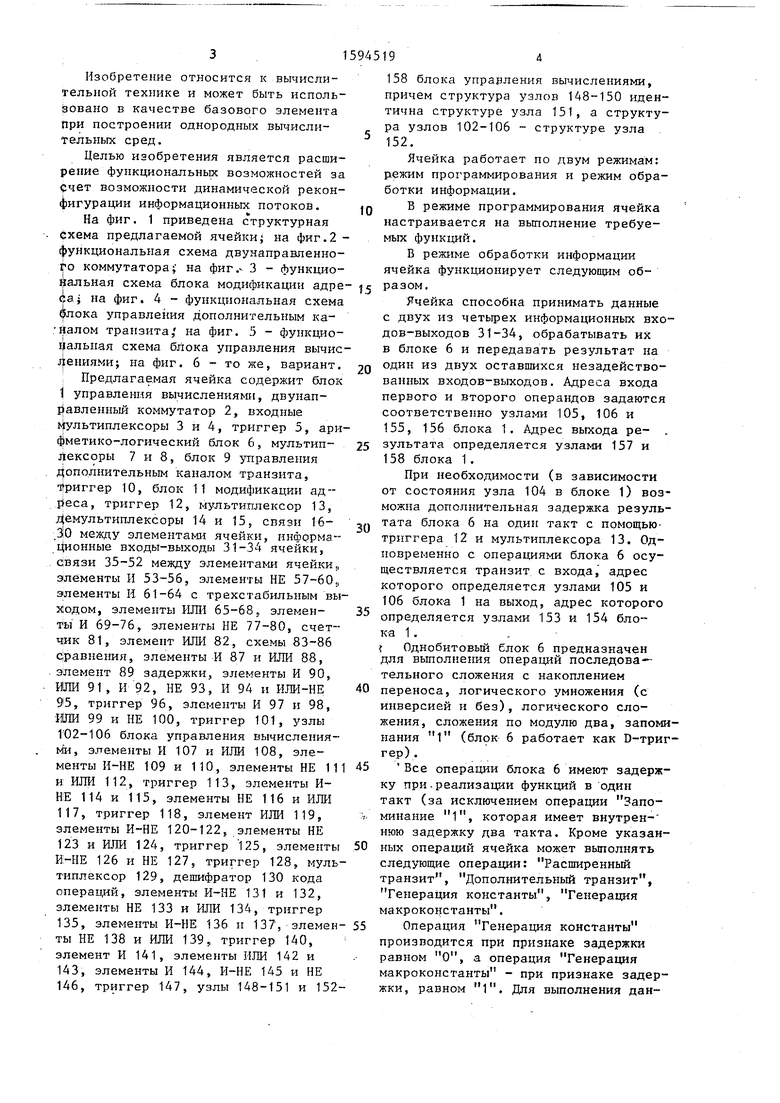

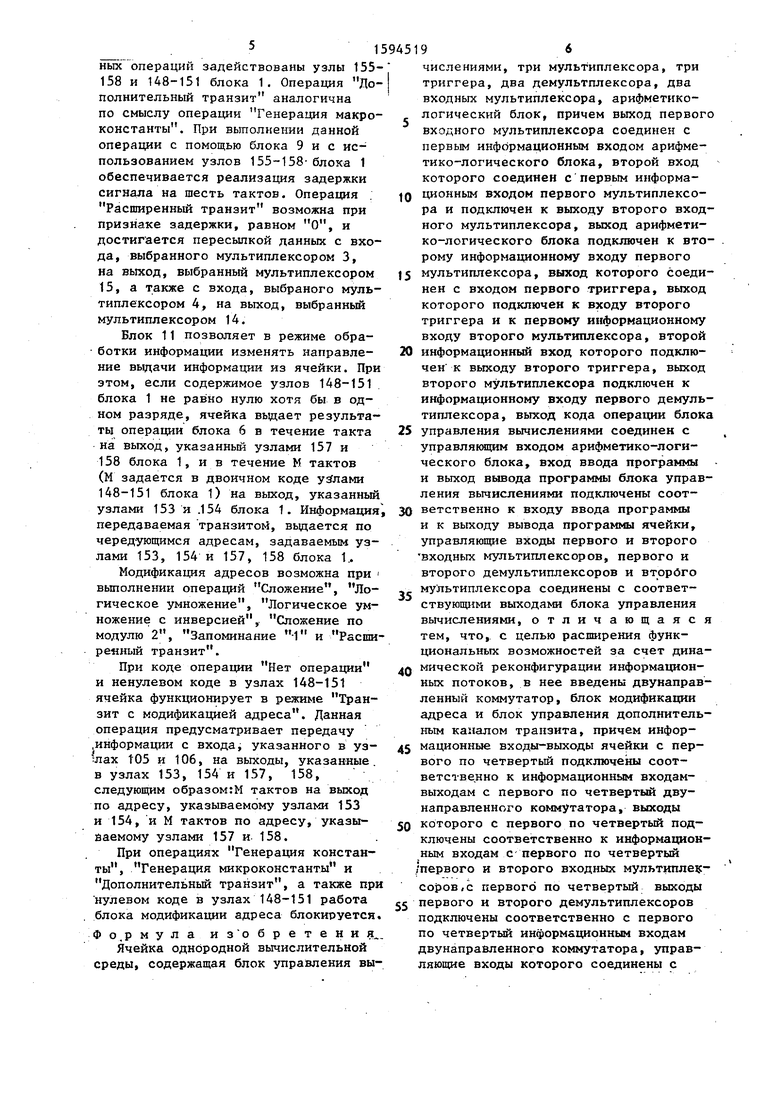

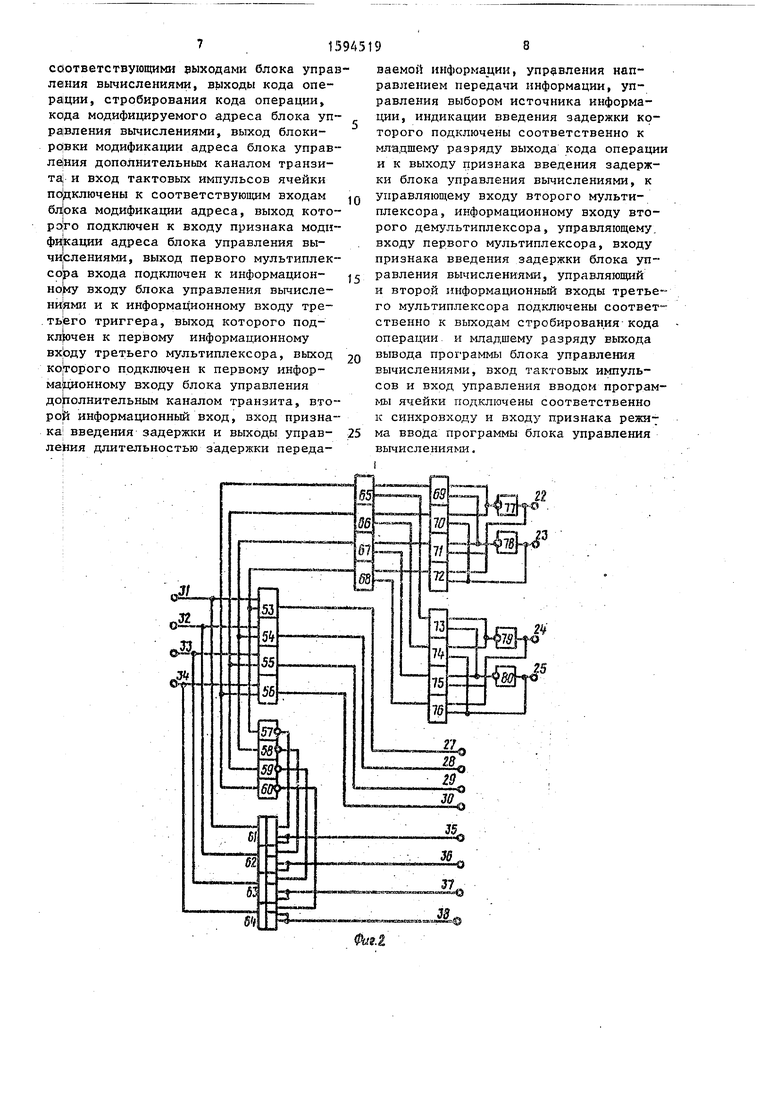

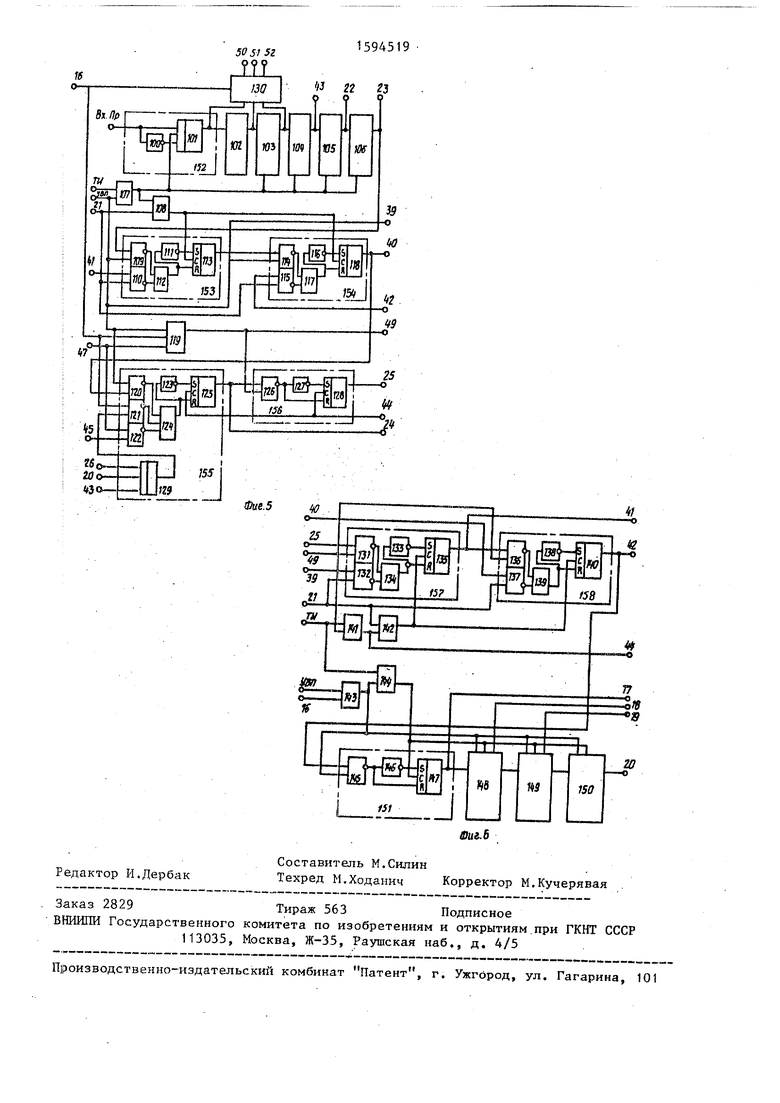

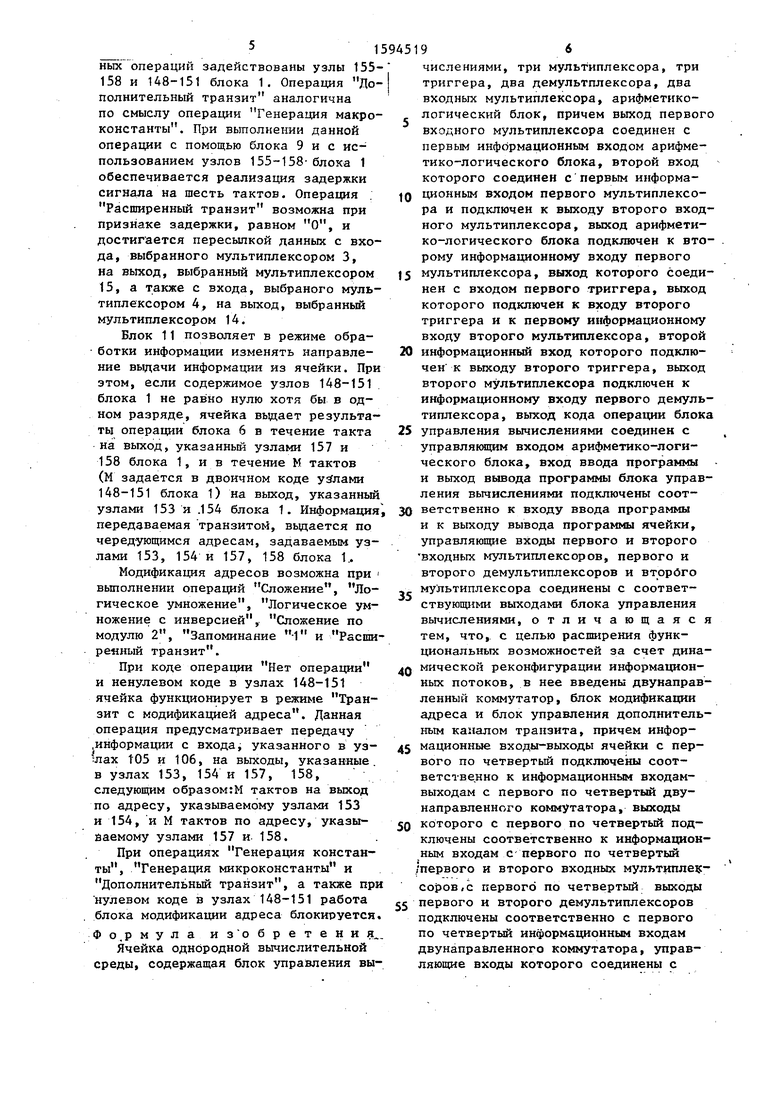

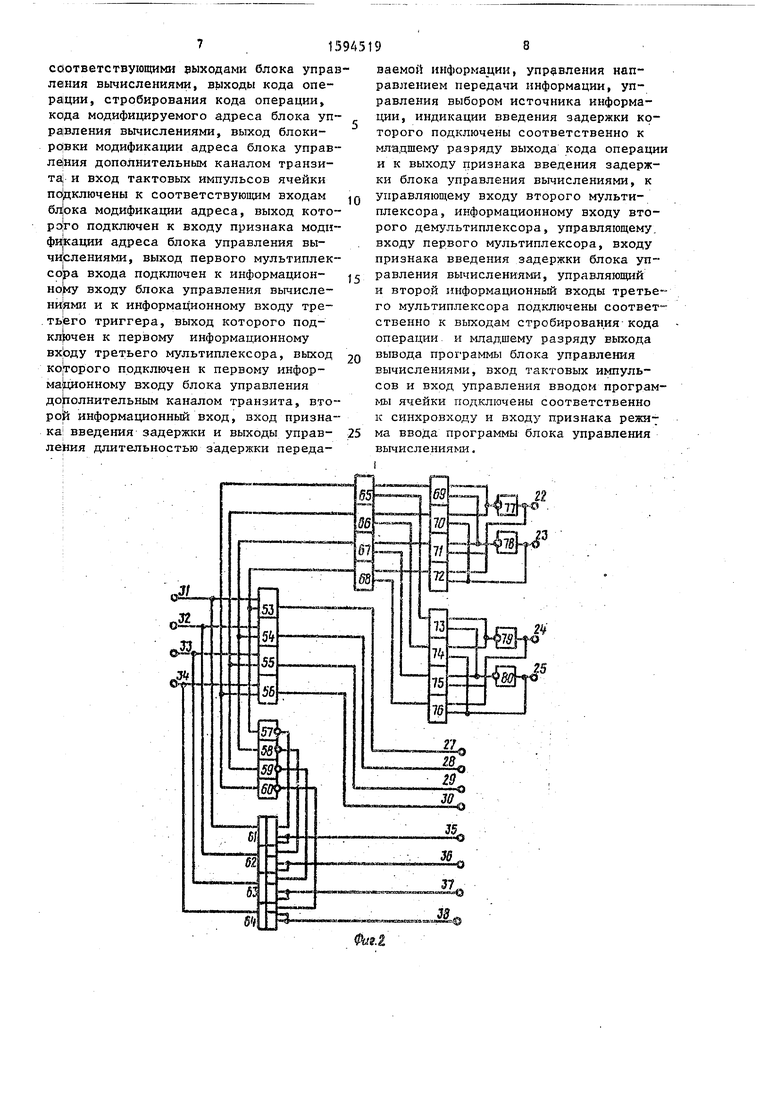

На фиг. 1 приведена с труктурная схема предлагаемой ячейки; на фиг.2 - функциональная схема двунаправленно- fo коммутатора ; на фиг.- 3 - функцио- 1 альная схема блока модификации адре- jc (paj на фиг. 4 - функциональная схема флока управления дополнительным ка- йалом транзита, на фиг. 5 - функцио- цапъпая схема блока управления вычис- ениями; на фиг. 6 - то же, вариант. jQ , Предлагаемая ячейка содержит блок 1 управления вычислениями, двунаправленный коммутатор 2, входные мультиплексоры 3 и 4, триггер 5, арифметико-логический блок 6, мультип- 25 лексоры 7 и 8, блок 9 управления Дополнительным каналом транзита, 1|риггер 10, блок 11 модификации ад- lieca, триггер 12, мультиплексор 13, 7|емультиплексоры 14 и 15, связи 16- 3|0 между элементами ячейки, информа-- ионные входы-выходы 31-34 ячейки, связи 35-52 между элементами ячейки., элементы И 53-56, элементы НЕ 57-60,, элементы И 61-64 с трехстабильным выходом, элементы ИЛИ 65-68, элемен- 35 ты И 69-76, элементы НЕ 77-80, счетчик 81, элемент ИЛИ 82, схемы 83-86 с;равнения, элементы И 87 и ИЖ 88, элемент 89 задержки, элементы И 90, ЛИ 91, И 92, НЕ 93, И 94 и ИЛИ-НЕ 40 95, триггер 96, элементы И 97 и 98, ЛИ 99 и НЕ 100, триггер 101, узлы 102-106 блока управления вычисления- №1, элементы И 107 и ИЛИ 108, элементы И-НЕ 109 и 110, элементы НЕ 111 45 : ИЛИ 112, триггер 113, элементы И- НЕ 114 и 115, элементы НЕ 116 и ИЛИ 117, триггер 118, элемент ИЛИ 119, элементы И-НЕ 120-122, элементы НЕ 123 и ИЛИ 124, триггер 125, элементы 50 -НЕ 126 и НЕ 127, триггер 128, мультиплексор 129, дешифратор 130 кода операций, элементы И-НЕ 131 и 132, элементы НЕ 133 и ИЛИ 134, триггер 135, элементы И-НЕ 136 и 137, элемен- 55 ы НЕ 138 и ИЛИ 139, триггер 140, лемент И 141, элементы ИЛИ 142 и 143, элементы И 144, И-НЕ 145 и НЕ 146, триггер 147, узлы 148-151 и 152158 блока управления вычислениями, причем структура узлов 148-150 идентична структуре узла 151, а структура узлов 102-106 - структуре узла 152.

Ячейка работает по двум режимам: режим программирования и режим обработки информации.

В режиме программирования ячейка настраивается на выполнение требуемых функций.

В режиме обработки информации ячейка функционирует следуюсцим образом.

Ячейка способна принимать данные с двух из четьфех информационных входов-выходов 31-34, обрабатывать их в блоке 6 и передавать результат на один из двух оставшихся незадействованных входов-выходов. Адреса входа первого и второго операндов задаются соответственно узлами 105, 106 и 155, 156 блока 1. Адрес выхода ре- зультата определяется узлами 157 и 158 блока 1.

При необходимости (в зависимости от состояния узла 104 в блоке 1) возможна дополнительная задержка результата блока 6 на один такт с помощью- триггера 12 и мультиплексора 13. Одновременно с операциями блока 6 осуществляется транзит с входа, адрес которого определяется узлами 105 и 106 блок-а 1 на выход, адрес которого определяется узлами 153 и 154 блок-а 1 .

( Однобитовый блок 6 предназначен для вьтолнения операций последова-

тельного сложения с накоплением переноса, логического умножения (с инверсией и без), логического сложения, сложения по модулю два, запомнания 1 (блок 6 работает как D-три гер) .

Все операции блока 6 имеют задержку при.реализации функций в один такт (за исключением операции Запоминание 1, которая имеет внутрен- нюю задержку два такта. Кроме указанных операций ячейка может выполнять следующие операции: Расширенный транзит, Дополнительный транзит, Генерация константы, Генерация макрокоцстанты.

Операция Генерация константы производится при признаке задержки равном О, а операция Генерация макроконстанты - при признаке задержки, равном 1, Для выполнения данJ:лах t05 и 106, на выходы, указанные в узлах 153, 154 и 157, 158, следующим образом:М тактов на вькод по адресу, указываемому узлами 153 и 154, и М тактов по адресу, указываемому узлами 157 и 158.

При операциях Генерация константы, Генерация микроконстанты и Дополнительный транзит, а также пр нулевом коде в узлах 148-151 работа блока модификации адреса блокируется

Фо,рмула из обретения

Ячейка однородной вычислительной среды, содержащая блок управления вы

5

ных операций задействованы узлы 155 158 и 148-151 блока 1, Операция Дополнительный транзит аналогична по смыслу операции Генерация макроконстанты. При вьтолкении данной операции с помощью блока 9 и с использованием узлов 155-158- блока 1 обеспечивается реализация задержки сигнала на шесть тактов. Операция Расширенный транзит возможна при признаке задержки, равном О, и достигается пересылкой данных с входа, выбранного мультиплексором 3, на выход, выбранный мультиплексором 15, а также с входа, выбраного мультиплексором 4, на выход, выбранный мультиплексором 14.

Блок 11 позволяет в режиме обработки информации изменять направление выдачи информации из ячейки. При этом, если содержимое узлов 148-151 блока 1 не равно нулю хотя бы в одном разряде, ячейка вьздает результаты операции блока 6 в течение такта на выход, указанный узлами 157 и 158 блока 1, ив течение М тактов (М задается в двоичном коде углами 148-151 блока 1) на выход, указанный узлами 153 и .154 блока 1. Информация передаваемая транзитов, вьщается по чередующимся адресам, задаваемым узлами 153, 154 и 157, 158 блока 1..

Модификация адресов возможна при вьтолнении операций Сложение, Логическое умножение, Логическое умножение с инверсией, Сложение по модулю 2, Запоминание -1 и Расширенный транзит.

При коде операции Нет операции и ненулевом коде в узлах 148-151 ячейка функционирует в режиме Транзит с модификацией адреса. Данная операция предусматривает передачу .информации с входа, указанного в уз

0

5

0

5

5

0

5

0

5

0

5

196

числениями, три мультиплексора, три триггера, два демультплексора, два входных мультиплексора, арифметико- логический блок, причем выход первого входного мультиплексора соединен с первым информационным входом арифметико-логического блока, второй вход которого соединен с первым информа- ционньм входом первого мультиплексора и подключен к выходу второго входного мультиплексора, выход арифметико-логического блока подключен к вто- . рому информационному входу первого мультиплексора, выход которого соединен с входом первого триггера, выход которого подключен к входу второго триггера и к первому информационному входу второго мультиплексора, второй информационный вход которого подключен к выходу второго триггера, выход второго мультиплексора подключен к информационному входу первого демуль- типлексора, выход кода операции блока управления вычислениями соединен с управляющим входом арифметико-логического блока, вход ввода программы и выход вывода программы блока управления вычислениями подключены соответственно к входу ввода программы и к выходу вывода программы ячейки, управляющие входы первого и второго входных мультиплексоров, первого и второго демультиплексоров и вторбго мультиплексора соединены с соответствующими выходами блока управления вычислениями, отличающаяся тем, что, с целью расширения функциональных возможностей за счет динамической реконфигурации информационных потоков, в нее введены двунаправленный коммутатор, блок модификации адреса и блок управления дополнительным каналом транзита, причем информационные входы-выходы ячейки с первого по четвертый подключены соответственно к информационным входам- выходам с первого по четвертый двунаправленного коммутатора, выходы которого с первого по четвертый подключены соответственно к информационным входам с первого по четвертый /первого и второго входных мультиплексоров, с первого по четвертый выходы первого и второго демультиплексоров подключены соответственно с первого по четвертый информахщонным входам двунаправленного коммутатора, управляющие входы которого соединены с

соответствующими выходами блока управления вычислениями, выходы кода операции, стробирования кода операции, кода модифицируемого адреса блока уп ра вления вычислениями, выход блокировки модификации адреса блока управ- ле|ния дополнительным каналом транзи- Taj и вход тактовых импульсов ячейки по дключены к соответствующим входам бл|ока модификации адреса, выход кото- рфо подключен к входу признака моди- фи|кации адреса блока управления вы- чи слениями, выход первого мультиплексора входа подключен к информацион- но|му входу блока управления вычисле- ни|ями и к информационному входу тре- . ть;его триггера, выход которого под- к первому информационному вх|оду третьего мультиплексора, выход KoJToporo подключен к первому инфор- ма ;ционному входу блока управления до олнительным каналом транзита, второй информационный вход, вход признака введения задержки и выходы управ- леНия длительностью задержки переда0

с n 5

ваемой информа1 ии, управления направлением передачи информации, управления выбором источника информации, индикации введения задержки которого подключены соответственно к младшему разряду выхода кода операции и к выходу признака введения задержки блока управления вычислениями, к У11равляюп1ему входу второго мультиплексора, информационному входу второго демультиплексора, управляющему, входу первого мультиплексора, входу признака введения задержки блока управления вычислениями, управляющий и второй информационный входы третьего мультиплексора подключены соответственно к выходам стробирования-кода операции и младшему разряду выхода вывода программы блока управления вычислениями, вход тактовых импульсов и вход управления вводом програм- ш ячейки подключены соответственно к синхровходу и входу признака режи ма ввода программы блока управления вычислениями.

ТУ

УВП

«J 52

87

27

50о- 510- 5201

91

ffS itl

Фиг.

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бачериков Г.И | |||

| и др | |||

| Мультикон- вейерные вычислительные структуры на однородных средах | |||

| - Львов: Изд- во ФМИ АН УССР, 1985, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

Авторы

Даты

1990-09-23—Публикация

1987-09-29—Подача