При вычислении функции созХ в случае, если аргумент функции cosX находится в I или TV квадранте,на первом управляющем входе мультиплексора 4 и первом входе элемента И 1 1 устанавливаются логические нули или логические единицу. При прохождении на второй вход элемента И 11 единичного управляющего сигнала с выхода 36 блока 1 управления на втором управляющем входе мультиплексора 4 устанавливается нулевой сигнал.

В случае, если аргумент функции cosX отрицателен, то на управляющих входах мультиплексора 4 устанавливается код 01 или 10. При этом на его выходе устанавливается логическая единицао

При вычислении функции ginX для обеспечения запоминания знака функции на второй вход элемента И 11 с выхода 36 поступает нулевой сигнал. В соответствии с таблицей на выходе первого мультиплексора 4 устанавливается нулевой сигнал для sinX О, и единичный дпя sinX J.O, т.е. аналогично функции cosX.

Сигнал с выхода мультиплексора 4 поступает на информационный вход

триггера 10 и по стробирующему импульсу с выхода 17 переводит его в нулевое состояние (для cosX О, sinX 0) или в единичное состояние

(длясо8Х 0, )0

Следующий такт начинается с обращения в блок 3 памяти за константой А .

На выход 34 блока 1 управления с

второго адресного выхода блока 37 памяти микропрограмм через группу 41 мультиплексоров проходит адрес регистра адреса констант регистров группы )4, содержащего адрес константы

е - Содержимое регистра адреса констант поступает на,первый вход арифметико-логического блока 46 к,пройдя через регистр 50 и первый информационный выход коммутатора 53,устанавливается на выходе 14 блока 3 памяти

По сигналам обращения на выходе 16 блока 3 памяти устанавливается константа А, и по управляющему сигналу записывается в регистр 51 операционного блока 2.

В этом же такте в блоке 55 умножения перемножается содержимое регистров 47 и 48 и значение произведения Р Описывается в регистр 49.

;

Кроме того, в этом же

такте

V

формируется адрес константы А Для этоа

го арифметико-логический блок 46 к значению адреса константы Af() добавляет единицу, Адрес константы А Ј записывается в регистр адреса констант регистров 54 группы.

R следующем такте значения константы через арифметико-логический блок 46 с выхода 29 операционного блока 2 через мультиплексоры 7-9 и 6 поступает на вход 24 операционного блока 2 и записывается в регистр 48.

Затем в этом же такте в регистр 47 записывается значение Р„ для чего оно пересылается в него из регистра 49 через мультиплексор 52 и арифметико-логический блок 46,

В очередном такте по очередной микрокоманде аналогично описанному производятся операции: обращение в блок 3 памяти за значением константы At и запись At в регистр 51;

оо

аналогично, увеличением адреса константы A j на единицу определяют адрес константы А и записывают его в регистр адреса констант регистров групгГы 54; в этом же такте содержимо регистров 47 и 48 перемножается и результат ,Р записывается в третий регистр 44.

В следующем такте по очередной микрокоманде А 0 Р через мультиплексор 52 поступает на первый вход арифметико-логического блока 46 и складывается со значением константы -А. Результат сложения Р + А формируется на выходе 29 операционного блока 2 и записывается через мультиплексоры 7 - 9 и 6 и вход 24 операционного блока 2 в регистр 48 операционного блока 2о Далее микрокоманды последних двух тактов циклически пов теряются до тех пор, пока не будет вычислено выражение ((( Р + ) X х Р + А) Р + А) Р + At. Результа записывается в регистр 49„

Следующий такт начинается с обращения в блок 3 памяти за константой А записи ее в регистр 5i . Содержимое регистра 48 умножается на содержимое регистра 47 и результат, как и в предыдущих случаях, записывается в регистр 49

В этом же такте, аналогично формированию очередной константы, формируется адрес очередного командно

1

10

15

20

30

4045

47К Л 18

го спорт. В случае с выходя 34 блока f управления поступает адрес регистра группы 54, отведенного под счетчик команд.

В следующем.такте содержимое регистра 49 пересылается на первый вход арифметико-логического блока 46, складывается с полученный результат F(X) формируется на четвертом выходе 29 операционного устройства 2.

Значение функции F(x) сдвигается на один разряд, т„е0 по управляющим сигналам с выхода 36 блока 1 управления пропускается информация с вторых входов мультиплексоров 6-9. При этом на выходе мультиплексора 8 устанавливается нулевой сигнал, а на выходах остальных мультиплексоров - информация с 1 по 31 разряды. Сдвинутое на один разряд значение F(X) записывается в один из регистров группы 54 по адресу, поступившему из блока 1 управления.

В этом же такте с выходов 36 формируется управляющий сигнал анализа перехода по условию, который разрешает прохождение информации о знаке функции с выхода триггера 10 через мультиплексор 39 на вход установки в триггера 42,Начальный адрес, микропрограммы функции выбирается так, что в данном такте адрес очередной микрокоманды имеет четное значение (триггер 42 находится в нулевом состоянии)

В случае, если на выходе триггера 10 устанавливается логический О (функция П), то состояние триггера 42 не изменяется На этом вычисление функции cosX заканчивается

25

и в следующем такте по изменившемуся адресу формируется набор управляющих сигналов, необходимых для обращения за очередным командным словом и его приемом.,

В случае, если на выходе триггера 10 устанавливается логическая I (функция 0) триггер 42 переходит в единичное состояние, увеличивая,тем самым, значения адреса микрокоманды на единицу.

В следующем такте по этому адресу на выходах 17,35, 36 и 34, выходах блока i управления формируются сигналы, в соответствии с которыми значение функции F(X) появляется на первом входе арифметико-логического

блока Д6, которое инпертирует содержимое первого входа и добавляет единицу в младший разряд, Тгвс функции присваивается отрицательное значение

На этом вычисление функции (для сокХ 0) заканчивается,,

Для вычисления функции sinX необходимо при формировании приведенного аргумента Xv изменить значение тридцатого разряда, кода аргумента на противоположное. Для этого при формировании X управляющим сигналом с выходов 36 блока 1 управления открывается второй информационный

вход мультиплексора 5„ При этом на первый информационный вход мультиплексора 6 поступает проинвертиро- ванное значение тридцатого разряда кода аргумента.

R остальном вычисление функции sinX аналогично вычислению функции cosX.

Формула изобретения

Устройство для вычисления функций синуса и косинуса, содержащее арифметико-логический блок, блок ум-

ствл и рходу признака знака функции блока управления, соответствующие разряды третьего выхода блока управления .подключены к управляющим входам третьего мультиплексора и коммутатора, соответствующие разряды четвертого выхода блока управления подключены к управляющим входам четвертого, пятого, шестого и седьмого мультиплексоров, выходы которых подключены через шину к информационным входам первого и второго регистров и регистров группы, выход признака результата операции арифметико-логи- ческбго блока подключен к входу признака результата операции блока управления, вход кода операции блока управления подключен к выходу блока памяти и к информационному входу пятого регистра, выход которого подключен к первому информационному входу арифметико-логического блока, вход пуска устройства подключен к установочным входам регистров с первого по пятый, выход первого старшего разряда пятого регистра подключен к первому управляющему входу второго мультиплексора, с первого по четвертый

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тригонометрических функций | 1985 |

|

SU1257639A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1061136A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

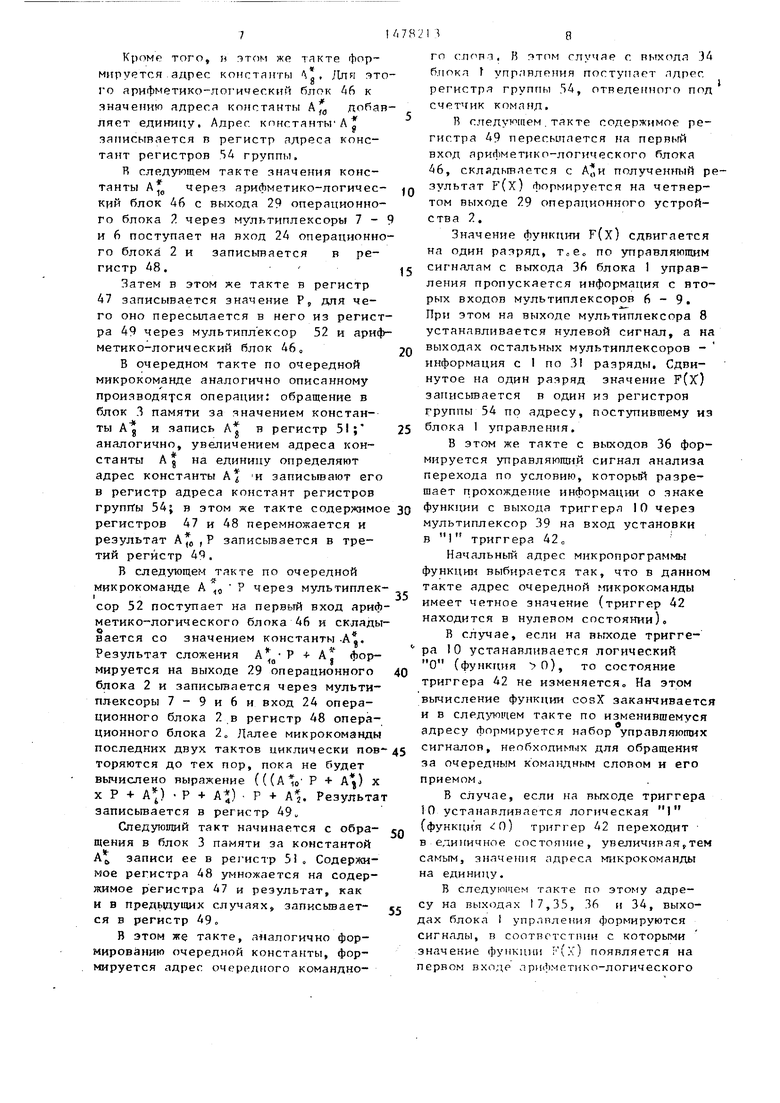

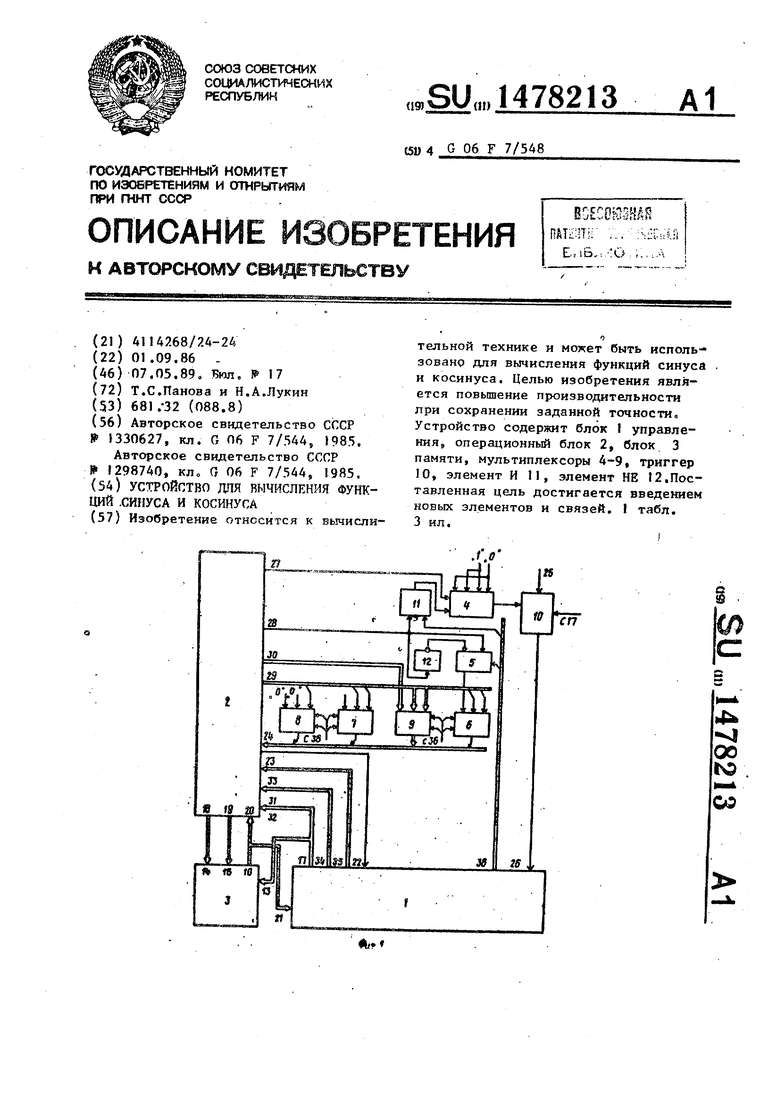

Изобретение относится к вычислительной технике и может быть использовано для вычисления функций синуса и косинуса. Целью изобретения является повышение производительности при сохранении заданной точности. Устройство содержит блок 1 управления, операционный блок 2, блок 3 памяти, мультиплексоры 4-9, триггер 10, элемент И 11, элемент НЕ 12. Поставленная цель достигается введением новых элементов и связей. 3 ил.

ножения, блок управления, два регист- зо информационные входы которого под

р а, группу регистров и блок памяти, причем разряды первого выхода блока управления подключены к входу выборки блока памяти, к синхровходам первого и второго регистров и регистров группы, разряды выхода блока управления подключены к разрядам входа выбора регистров группы, разряды третьего управляющего выхода блока управления подключены к управляющим входам блока умножения и арифметико-логического блока, отличающееся тем, что, с целью повышения производительности при сохранении заданной

точности, в него введены семь мульти- „ формационным входам четвертого,пято-о

плексоров, коммутатор, триггер, эле- И, элемент НЕ и три регистра, причем соответствующие разряды четвертого выхода блока управления под- 1ключены к первому входу элемента И ;и к управляющему входу первого муль- типлексора, соответствующие разряды первого выхода блока управления подключены к синхровходам третьего,четвертого и пятого регистров и триггера, информационный вход, вход установки в I и выход которого подключены соответственно к выходу второго мультиплексора, входу пуска устрой-

50

55

го и шестого мультиплексоров, выход второго старшего разряда арифметико- логического блока подключен к вторым информационным входам, четвертого и шестого мультиплексоров, выход первого мультиплексора подключен к третьему информационному входу четвертого мультиплексора, вход логического нуля устройства подключен к третьему информационному входу шестого мультиплексора и второму и третьему информационным входам пятого мультиплексора, выход младших разрядов пятого регистра подключен к первому

5

Q

ключены соответственно к входам логического нуля, логической единицы9ло- гической единицы и логического нуля устройства, выход второго старшего разряда пятого регистра подключен к второму входу элемента И, первому информационному входу первого мультиплексора и через элемент НЕ к второму информационному входу первого мультиплексора, выход элемента И под™ ключей к второму управляющему входу второго мультиплексора9 выход первого старшего разряда арифметико-логического блока подключен к первым ин

5

го и шестого мультиплексоров, выход второго старшего разряда арифметико- логического блока подключен к вторым информационным входам, четвертого и шестого мультиплексоров, выход первого мультиплексора подключен к третьему информационному входу четвертого мультиплексора, вход логического нуля устройства подключен к третьему информационному входу шестого мультиплексора и второму и третьему информационным входам пятого мультиплексора, выход младших разрядов пятого регистра подключен к первому

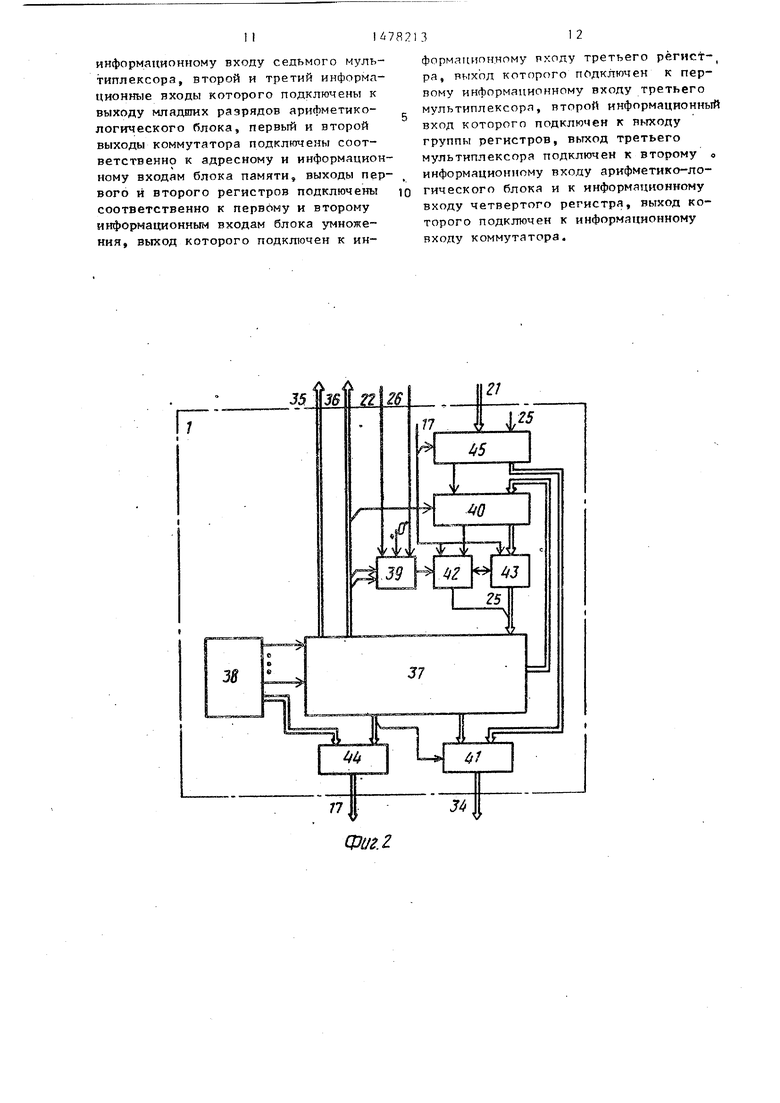

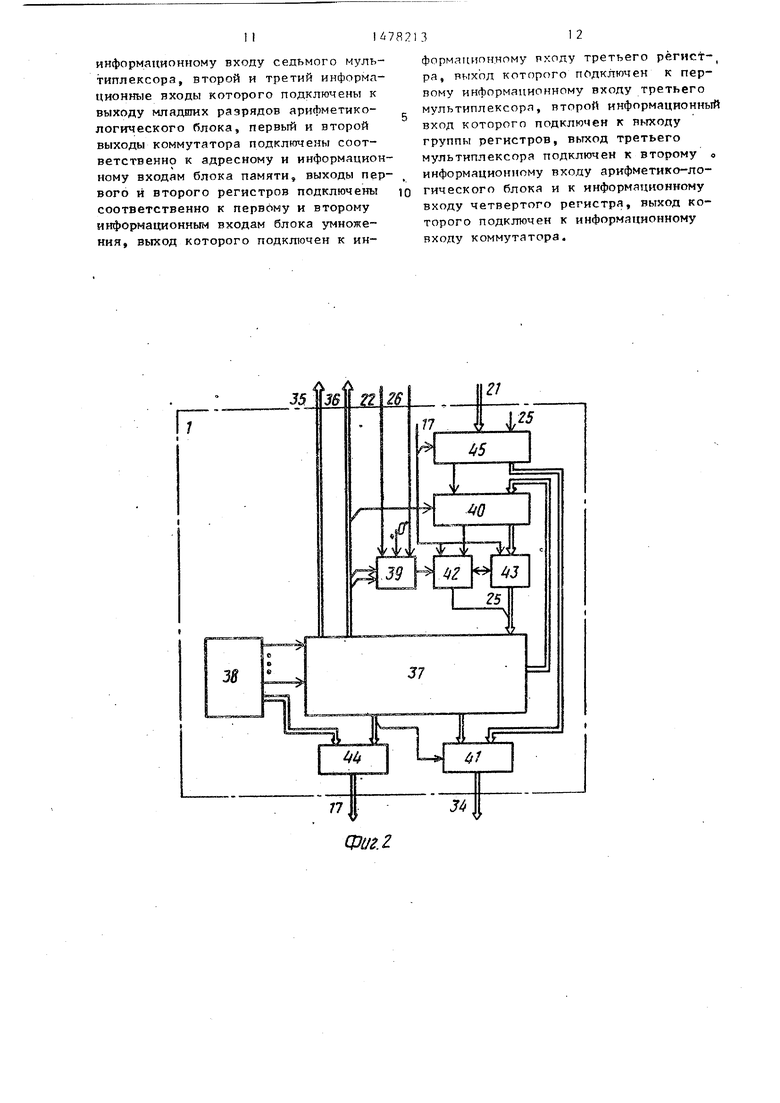

информационному входу седьмого мультиплексора, второй и третий информационные нходы которого подключены к выходу младших разрядов арифметико- логического блока, первый и второй выходы коммутатора подключены соответственно к адресному и информационному входам блока памяти, выходы первого и второго регистров подключены соответственно к первому и второму информационным входам блока умножения, выход которого подключен к ин77

Фиг. г

формационному пходу третьего рёгист-( ра, выход которого подключен к первому информационному входу третьего мультиплексора, второй информационный вход которого подключен к выходу группы регистров, выход третьего мультиплексора подключен к второму 0 информационному входу арифметико-логического блока и к информационному входу четвертого регистра, выход которого подключен к информационному входу коммутатора.

34

Фиг.з

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298740A1 |

Авторы

Даты

1989-05-07—Публикация

1986-09-01—Подача