/у

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

| Арифметико-логический модуль | 1988 |

|

SU1501032A1 |

| Многофункциональный модуль | 1984 |

|

SU1238098A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1109735A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1531086A1 |

| Многофункциональный запоминающий модуль для логической матрицы | 1989 |

|

SU1642525A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

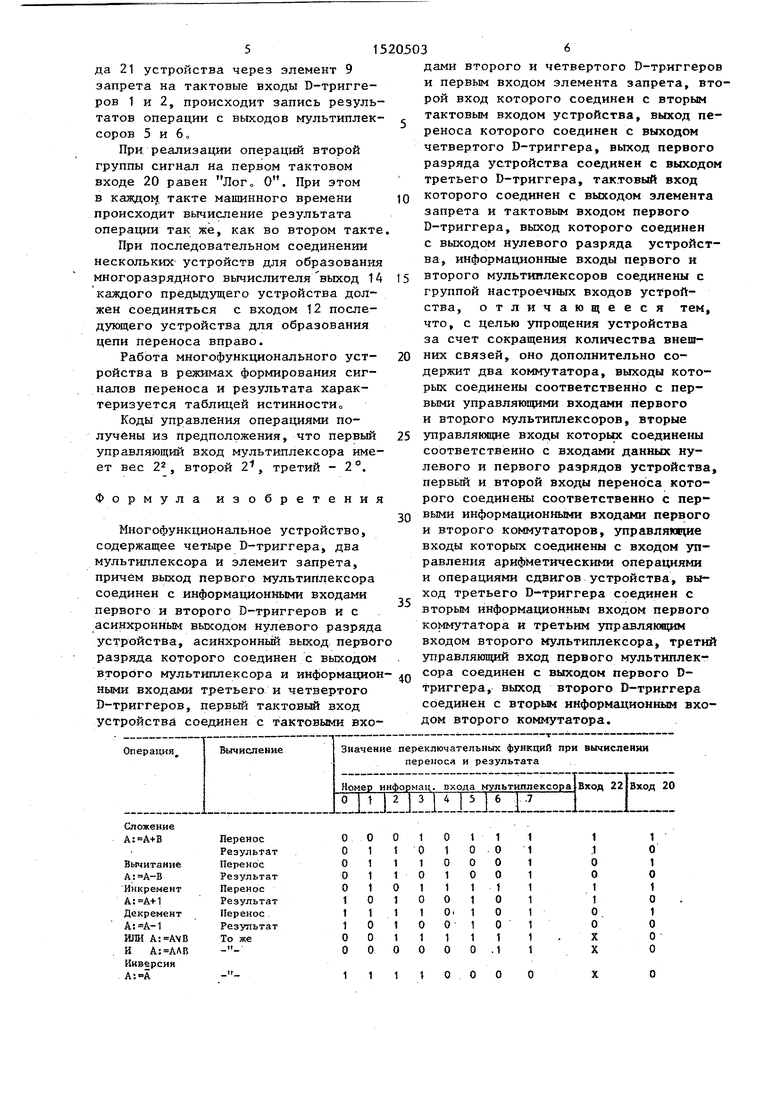

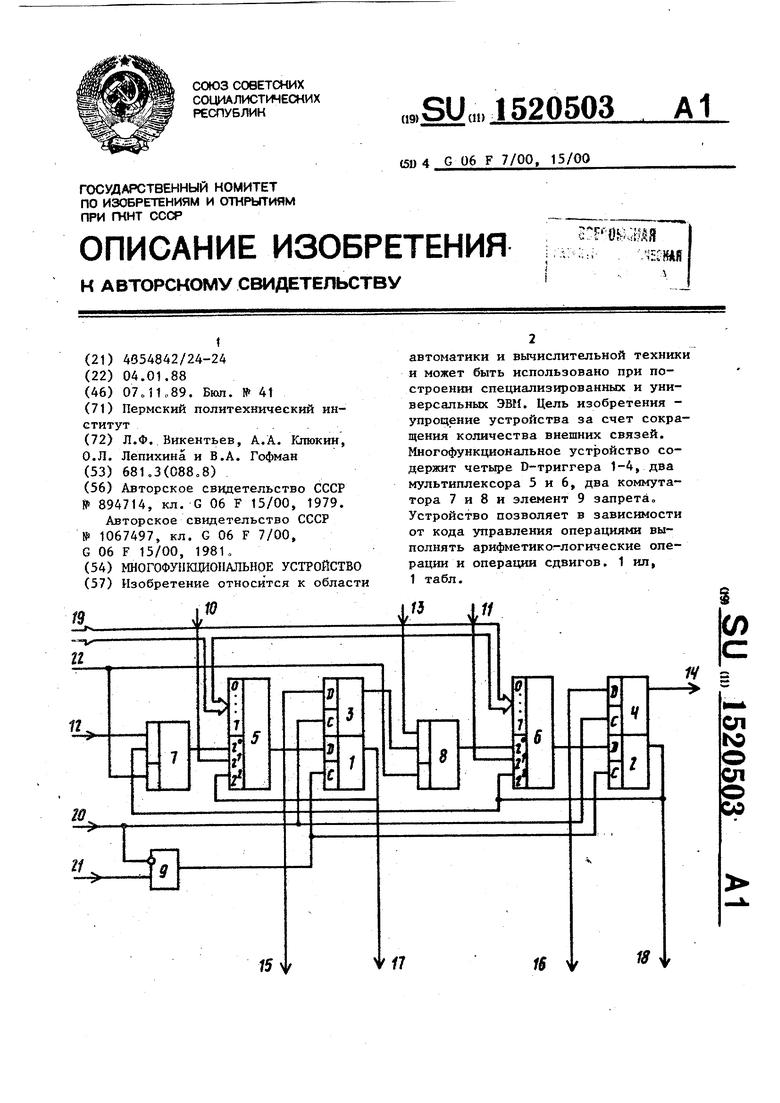

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении специализированных и универсальных ЭВМ. Цель изобретения - упрощение устройства за счет сокращения количества внешних связей. Многофункциональное устройство содержит четыре D - триггера 1-4, два мультиплексора 5 и 6, два коммутатора 7 и 8 и элемент 9 запрета. Устройство позволяет в зависимости от кода управления операциями выполнять арифметико-логические операции и операции сдвигов. 1 ил. 1 табл.

СП N9

О

сл

о

00

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении спеиуналиэированных и универсальных ЭВМ.

Цель изобретения - з рощение устройства за счет сокращения коли- чества внешних связей,

На чертеже представлена функциональная скема многофункционального устройства

Многофункциональное устройство содержит четыре D-триггера t-4, два мультиплексора 5 и 6, два коммутатора 7 и 8, элемент 9 запрета, вход 10 данных нулевого разряда, вход 11 данных первого разрдда, пер вьй вход 12 переноса, второй вход .13 переноса, викод 4 переноса, асинхронный выход 15 нулевого разря I да, асийхронный выход 16 первого. разряда, выход 17 нулевого разряда, выход 18 nepBoto разряда, группу .настроечных входов J9, первый так товьй вход 20, второй тактовый вход 21, вход 22 управления арифметическими операциями и операхщнми сдвигов о

Многофункциональное устройство работает следующим образом.

Все арифметико-логические операции, выполняемые устройством, могут быть разбиты на две группы, В первой из них результат формируется как функция Четырех аргументов; входньЕх данных разрядов, значений разрядов, переносов слева и справа Во второй группе комавд результат формируется без учета переносов.

В многофункциональном устройстве для вычисления переносов и результатов операций используются одни и те же мультиплексоры 5 и 6, при этом арифметико-логические операции первой группы реализуются за два такта машинного времени, в первом иэ вычисляется значение переносов из нзшевого и первого разрядов, запоминаемое в D- Триггерах 3 и 4 соответственно, а втором - значение операции в этом разряде с учетом переноса.

Команды второй группы вьтолня- ются обычным образом за один такт машинного времени;

Двоичный 8-разр дньй код, подаваемый на группу настроечных входо 19, и значение сигнала на входе

S

0

5

0

5

0

5

0

55

управления арифметическими операциями и операциями сдвигов определяют вид операции, реализуемой в данном такте машинного времени Если значение сигнала на первом тактовом входе 20 устройства принимает значение Лог. 1, то в устройстве осуществляется вычисление значения переноса каждого из разрядов (в зависимости от значения информации на группе настроечных входов 19) от значения сигналов на входах 10 н 1t данных нулевого и первого разрядов, а также от сигналов, сформированных на D-триггерах 1 и.2, и от выходных сигналов, сформированных на коммутаторах 7 и 8. На выходах коммутаторов 7 и 8 сигналы формируются в соответствии со значением сигнала на входе 22 управ ления арифметическими операциями и операциями сдвигов, поступающего rfa управляющие входы этих коммутаторов, на первые и вторые информационные входы коммзггаторов 7 и 8 подаются значения сигналов переноса слева и справа.

В этом такте в D-триггеры 3 и 4 происходит запись вычисленных значений переносов,, При этом через элемент 9 запрета блокируется сигнал синхронизации па тактовых входах D-триггеров 1 и 2j в результате чего в данном такте машинного

. времени эти триггеры сохраняют свое I

предьщущее значение.

При переходе к следующему такту машинного времени (такту вычисления результата операции) сигнал на первом тактовом входе 20 устройства должен принять значение Лог..0, что обеспечит сохранение записанных в D-триггеры 3 и 4 значений переносов из нулевого и первого разрядов соответственно и пропускание синхронизи- рующего сигнала через элемент 9 запрета, на тактовые входы D-триггеров 1 и 2 (нулевого и первого разрядов).

В этом такте машинного времени мультиплексоры 5 и 6 формируют значение результата операции, заданной 8-разрядным кодом на группе настроечных входов 19 в зависимости от значений сигналов на входах 10 и 11 данных, на выходах коммутаторов 7 и 8 и на выходах D-триггеров 1 и 2.

По фронту тактового сигнала, поступающего с второго тактового входа 21 устройства через элемент 9 запрета на тактовые входы D-тригге- ров 1 и 2, происходит запись результатов операции с выходов мультиплексоров 5 и 6о

При реализации операций второй группы сигнал на первом тактовом входе 20 равен ЛоГо О. При этом в каждого, такте машинного времени происходит вычисление результата операции так же, как во втором такте

При последовательном соединении нескольких устройств для образования многоразрядного вычислителя выход 14 каждого предьщущего устройства должен соединяться с входом 12 последующего устройства для образования цепи переноса вправо.

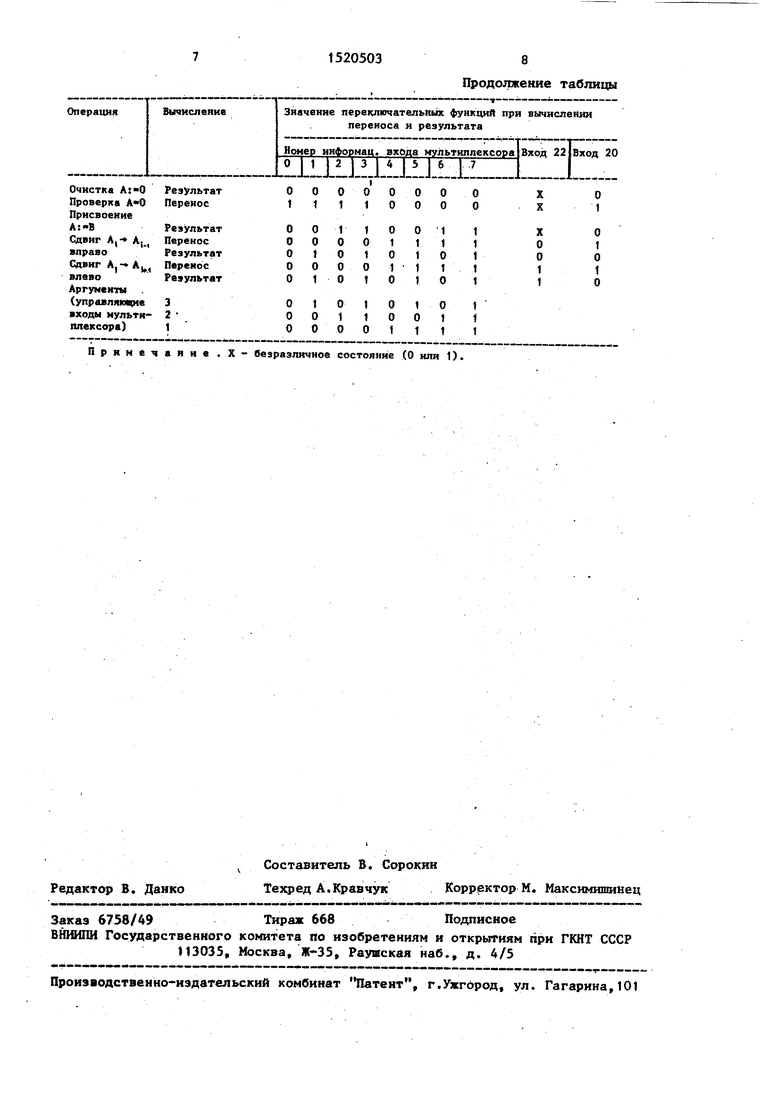

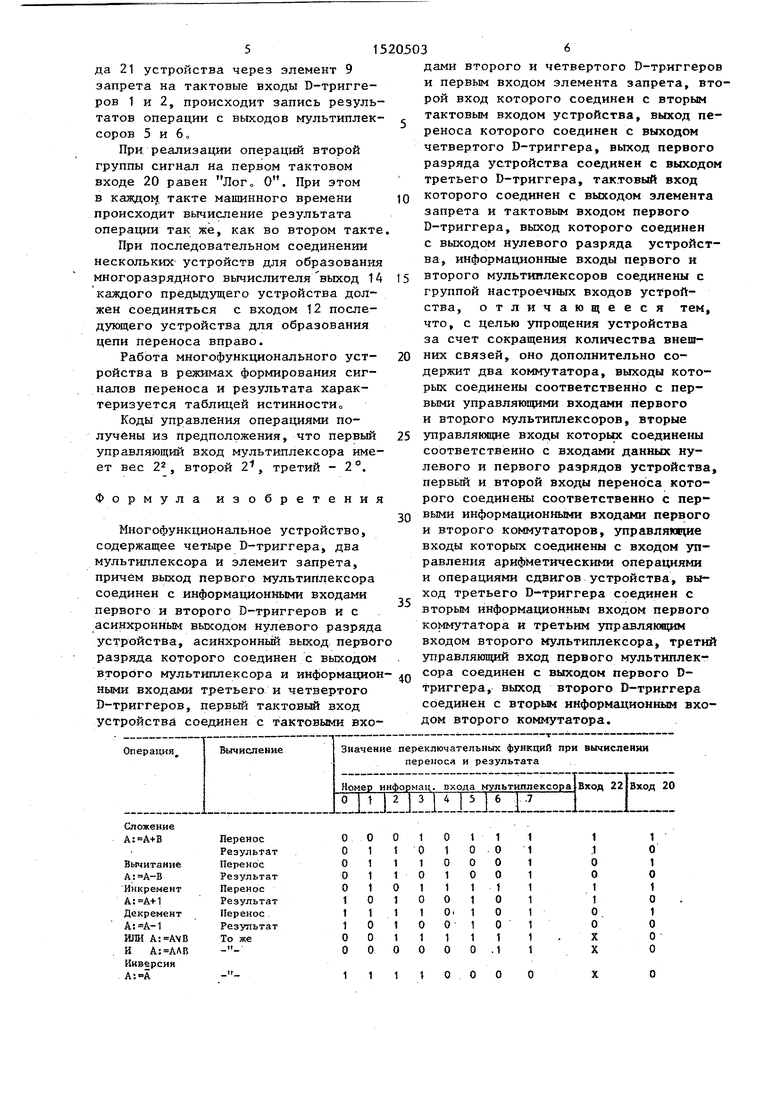

Работа многофункционального устройства в режимах формирования сигналов переноса и результата характеризуется таблицей истинности

Коды управления операциями получены из предположения, что первый управляющий вход мультиплексора имеет вес 2 , второй 2, третий - 2 °.

Формула изобретения

Многофункциональное устройство, содержащее четыре D-триггера, два мультиплексора и элемент запрета, причем выход первого мультиплексора соединен с информационными входами первого и второго D-триггеров и с асинхронным выходом нулевого разряда устройства, асинхронный выход первого разряда которого соединен с выходом второго мультиплексора и информацион- ными входами третьего и четвертого D-триггеров, первый тактовый вход устройства соединен с тактовыми вхо0

5

0

5

0

35

Q

дами второго и четвертого D-триггеров и первым входом элемента запрета, второй вход которого соединен с вторым тактовым входом устройства, выход переноса которого соединен с выходом четвертого D-триггера, выход первого разряда устройства соединен с выходом третьего D-триггера, тактовый вход которого соединен с выходом элемента запрета и тактовым входом первого D-триггера, выход которого соединен с выходом нулевого разряда устройства, информационные входы первого и второго мультиплексоров соединены с группой настроечных входов устройства, отличающееся тем, что, с целью упрощения устройства за счет сокращения количества внешних связей, оно дополнительно содержит два коммутатора, выходы которых соединены соответственно с первыми управляющими входами первого и второго мультиплексоров, вторые управлякщие входы которьрс соединены соответственно с входами данных нулевого и первого разрядов устройства, первьй и второй входы переноса которого соединены соответственно с первыми информационными входами первого и второго коммутаторов, управлякщие входы которых соединены с входом управления арифметическими операциями и операциями сдвигов устройства, выход третьего D-триггера соединен с вторым информационным входом первого коммутатора и третьим управляющим входом второго мультиплексора, третий управляющий вход первого мультиплексора соединен с выходом первого D- триггера, выход второго D-триггера соединен с втор)ым информационшлм входом второго коммутатора.

Примечание . Х- беэразлячное состояние (О или 1).

Продолжение таблицы

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1988-01-04—Подача