Изобретение относится к вычислительной технике и может найти применение при построении специализированных и универсальных ЭВМ.

Цель изобретения - сокращение чис- ла внешних выводов.

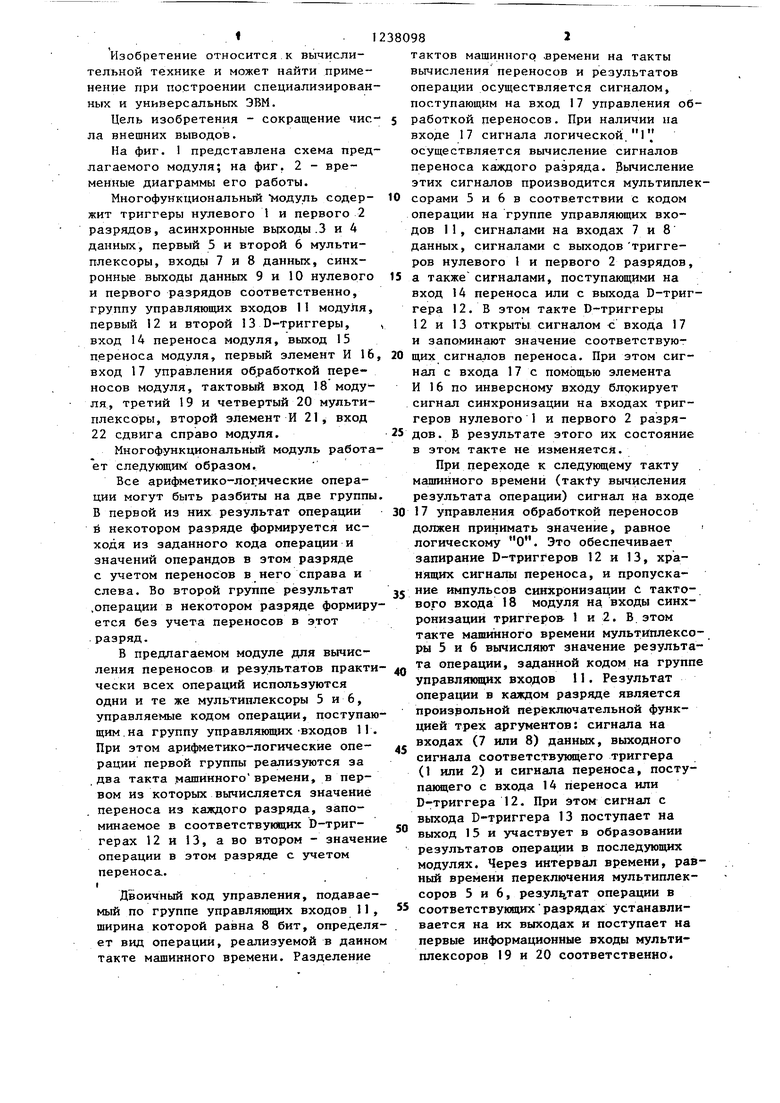

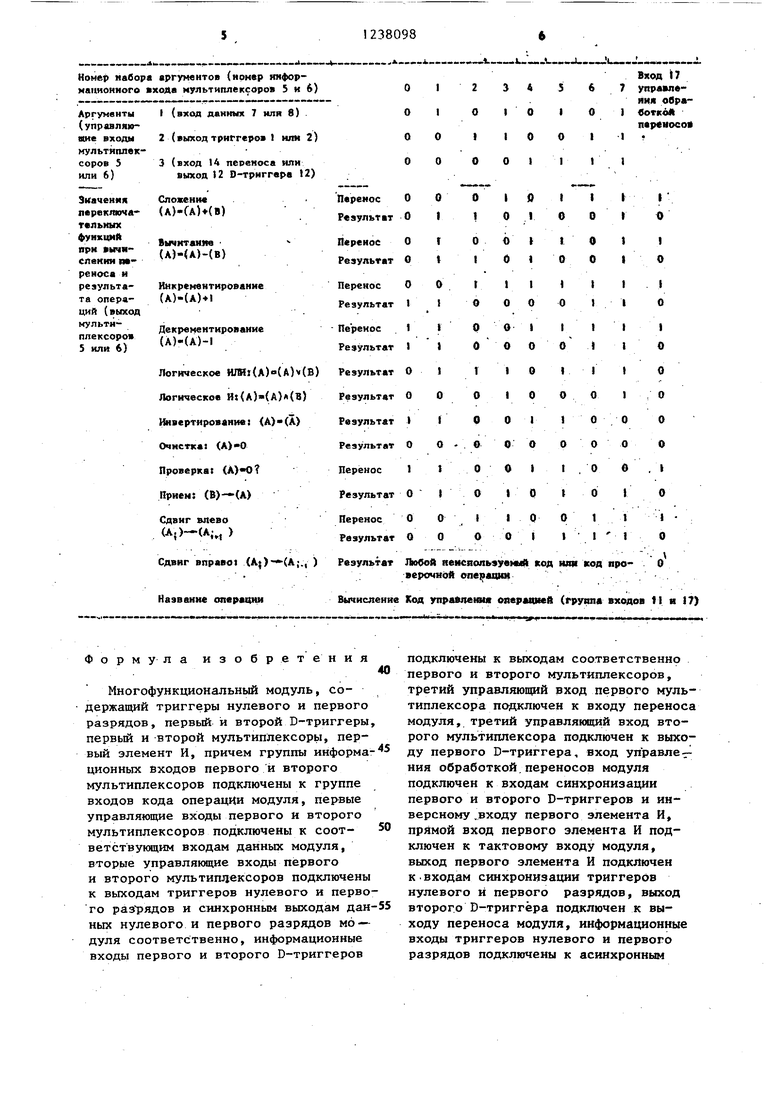

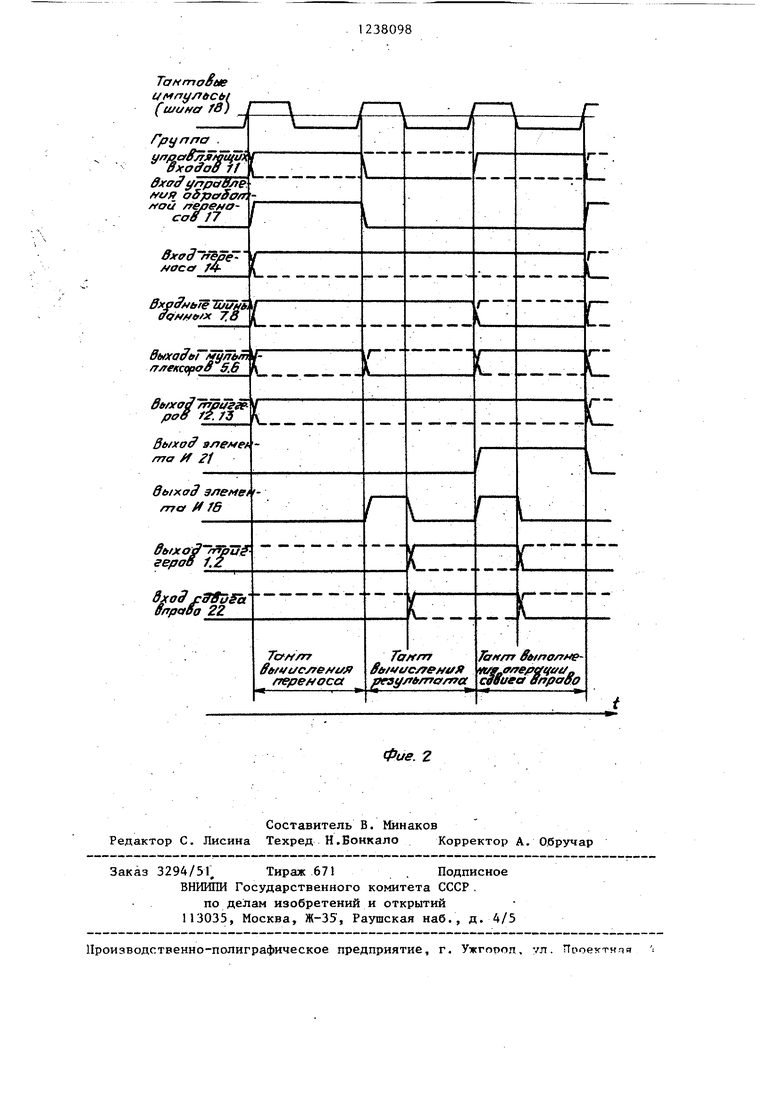

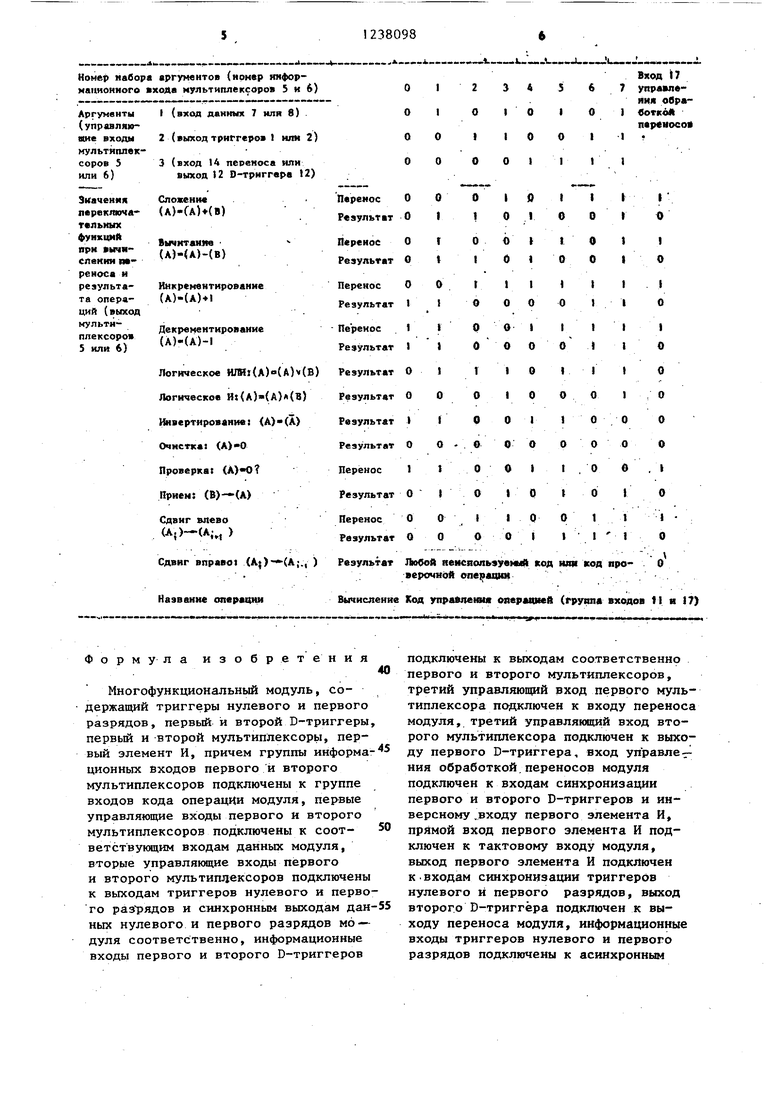

На фиг. 1 представлена схема предлагаемого модуля; на фиг. 2 - временные диаграммы его работы.

Многофункциональный модуль содержит триггеры нулевого I и первого 2 разрядов, асинхронные вьрсоды .3 и 4 данных, первый 5 и второй 6 мультиплексоры, входы 7 и 8 данных, синхронные выходы данных 9 и 10 нулевого и первого разрядов соответственно, группу управляющих входов 11 модуля, первый 12 и второй 13 D-триггеры, вход 14 переноса модуля, вькод 15 переноса модуля, первый элемент И 16 вход 17 управления обработкой переносов модуля, тактовый вход 18 моду

ля, третий 19 и четвертый 20 мультиплексоры, второй элемент И 21, вход 22 сдвига справе модуля.

Многофункциональный модуль работает следующим образом.

Все арифметико-логические операции могут быть разбиты на две группы В первой из них результат операции и некотором разряде формируется исходя из заданного кода операции и значений операндов в этом разряде с учетом переносов в него справа и слева. Во второй группе результат .операции в некотором разряде формируется без учета переносов в этот разряд.

В предлагаемом модуле для вычисления переносов и результатов практи чески всех операций используются одни и те же мультиплексоры 5 и 6, управляемые кодом операции, поступающим, на группу управляющих ВХОДОВ 11. При этом арифметико-логические операции первой группы реализуются за два такта машинного времени, в первом из которых вычисляется значение переноса из каждого разряда, запоминаемое в соответствующих D-триг- герах 12 и 13, а во втором - значени операции в этом разряде с учетом переноса.

Двоичный код управления, подаваемый по группе управляющих входов 11, ширина которой равна 8 бит, определяет вид операции, реализуемой в данном такте мащинного времени. Разделение

тактов машинного .времени на такты вычисления переносов и результатов операции осуществляется сигналом, поступающим на вход 17 управления обработкой переносов. При наличии на входе 17 сигнала логической. осуществляется вычисление сигналов переноса каждого разряда. Вычисление этих сигналов производится мультиплексорами 5 и 6 в соответствии с кодом операции на группе управляющих входов 11, сигналами на входах 7 и 8 данных, сигналами с выходов триггеров нулевого 1 и первого 2 разрядов, а также сигналами, поступающими на вход 14 переноса или с выхода D-триг- гера 12. В этом такте D-триггеры 12 и 13 открыты сигналом с входа 17 и запоминают значение соответствующих сигналов переноса. При этом сигнал с входа 17 с помощью элемента И 16 по инверсному входу блокирует сигнал синхронизации на входах триггеров нулевого 1 и первого 2 разрядов. В результате этого их состояние в этом такте не изменяется.

При переходе к следующему такту мащинного времейи (TaKty вычисления результата операции) сигнал на входе

17 управления обработкой переносов

должен принимать значение, равное логическому О. Это обеспечивает запирание В-триггеров 12 и 13, хранящих сигналы переноса, и пропуска- ние импульсов синхронизации с такто-. вого входа 18 модуля на входы синхронизации триггеров 1 и 2. В. этом такте машинного времени мультиплексоры 5 и 6 вычисляют значение результата операции, заданной кодом на группе управляющих вхрдов П. Результат операции в каждом разряде является произэольной пер(еключательной функцией трех аргументов: сигнала на входах (7 или 8) данных, выходного сигнала соответствующего триггера (1 или 2) и сигнала переноса, поступающего с входа 14 переноса или D-триггера 12. При этом сигнал с выхода D-триггера 13 поступает на выход 15 и участвует в образовании результатов операции в последующих модулях. Через интервал времени, равный времени переключения мультиплексоров 5 и 6, рез.ул11тат операции в соответствующих разрядах устанавливается на их выходах и поступает на первые информационные входы мультиплексоров 19 н 20 соответственно.

Мультиплексоры 19 и 20 управляются выходным сигналом элемента И 21, настроенным на декодирование кода операции сдвига вправо, поступающего на труппу управляющих входов 11. Поэтому при реализации всех остальных операций выходной сигнал элемента И 21 равен Логическому О, что обеспечивает в этом случае поступление

на выход мультиплексоров I9 и 20 информации, поступающей на их первьтй информационный вход. Таким образом, результат выполняемой операции в соответствующих разрядах устанавливается на информационных входах триг геров нулевого 1 и первого 2 разряда и соответствующих асинхронных выхода .3 и 4 данных. По фронту тактового им .пульса, поступающего с входа 18 чере открытый элемент И 16 на вход синх- ронизации триггеров 1 и 2, происходи запись этого результата в триггеры - нулевого 1 и первого 2 разрядов и ег формирование на синхронных выходных шинах 9 и 10 данных.

При реализации операций второй группы сигнал на входе 17 равен всегда логическому нулю и в каждом такте машинного времени (аналогично указанному) формируются результаты операций, задаваемых кодом на группе управляющих входов 11. К операциям второй группы относится и операция сдвига вправо, реализуемая в предлагаемом устройстве иначе, чем все остальные операции. При вычислении результата операции сдвига вправо, в отличие от прочих операций, не используются мультиплексоры 5 и 6. При поступлении кода операции .сдвига вправо на группу управлякицих входов 11 срабатьгоает элемент И 21, выходной сигнал которого переключает мультиплексоры 19 и 20. В результате этого, образуется прямая цепь сдвига вправо в которой выход каждого предыдущего старшего разряда непосредственно (через открытые по вторым входам мультиплексоры 19 и 20) соединены с информационным входом последующего младшего разряда. По фронту тактового импульса результат операции сдвига вправо гшалогичным о 5разом записывается в триггеры 1 и 2 и устанавливается на синхронных выходах данных. При последовательном соединении нескольких микропроцессорных модулей

10

30

15 : 20 25

5

0

5

0

5

для образования многоразрядного вычислителя выход 9 каждого последующего модуля должен соединяться с входом 22 предыдущего, модуля для образования общей цепи переноса вправо.

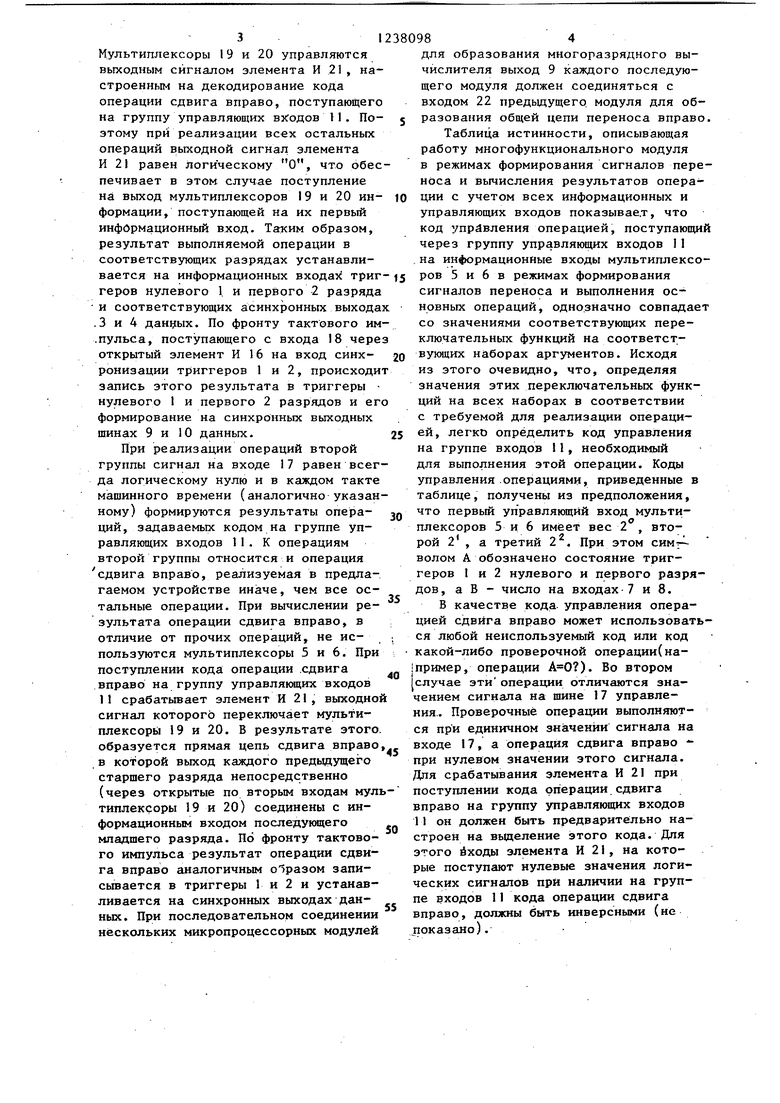

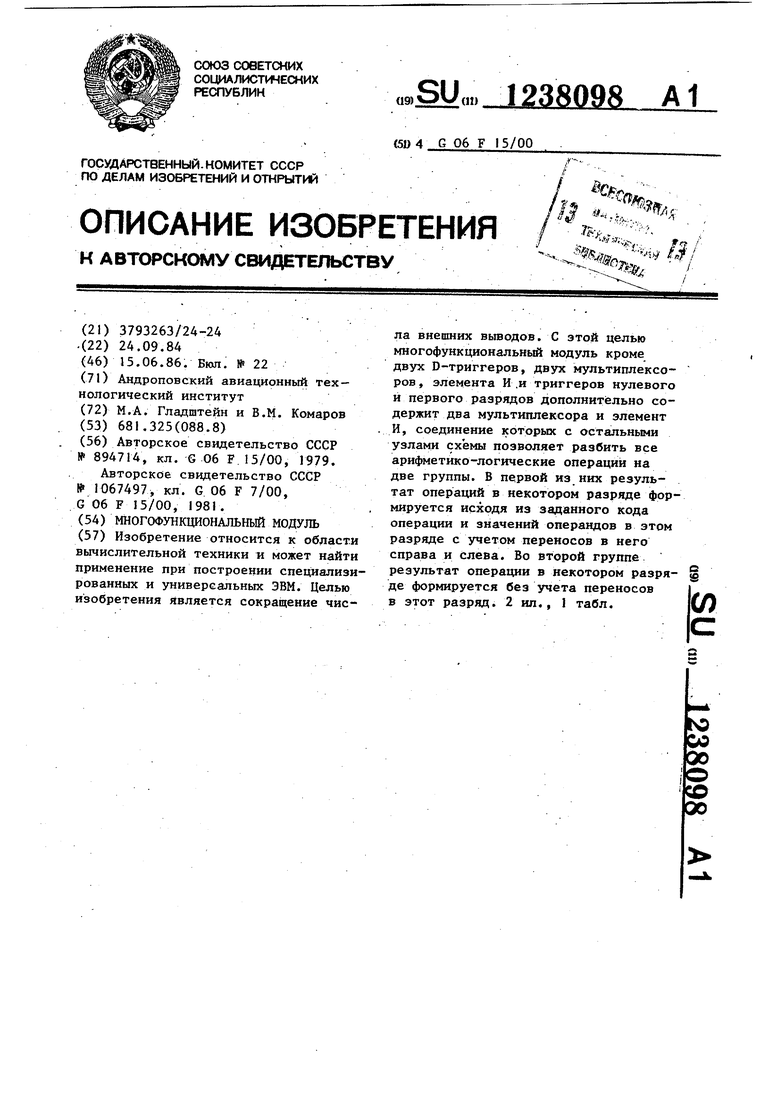

Таблица истинности, описывающая работу многофункционального модуля в режимах формирования сигналов переноса и вычисления результатов операции с учетом всех информационных и управляющих входов показывает, что код управления операцией, поступающий через группу управляющих входов I1 ,на информационные входы мультиплексоров 5 и 6 в режимах формирования сигналов переноса и выполнения основных операций, однозначно совпадает со значениями соответствующих переключательных функций на соответствующих наборах аргументов. Исходя из этого очевидно, что, определяя значения этих переключательных функций на всех наборах в соответствии с требуемой для реализации операцией, легко определить код управления на группе входов II, необходимый для выполнения этой операции. Коды управления операциями, приведенные в таблице, получены из предположения, что первый управляющий вход мультиплексоров 5 и 6 имеет вес 2 , второй 2 , а третий 2, При этом сим волом А обозначено состояние триггеров 1 и 2 нулевого и первого разрядов, а В - число на входах 7 и 8.

В качестве кода управления операцией сдвига вправо может использоваться любой неиспользуемый код или код какой-либо проверочной операции(на- пример, операции ). Во втором 1случае эти операции отличаются значением сигнала на шине 17 управления.. Проверочные операции выполняются при единичном значении сигнала на входе 17, а операция сдвига вправо - при нулевом значении этого сигнала. Для срабатывания элемента И 21 при постуггаении кода операции сдвига вправо на группу управляющих входов 11 он должен быть предварительно настроен на вьделение этого кода. Для этого йходы элемента И 21, на которые поступают нулевые значения логических сигналов при наличии на группе входов 11 кода операции сдвига вправо, должны быть инверсными (не показано).

Формула изобретения

Многофункциональный модуль, содержащий триггеры нулевого и первого разрядов, первый и второй D-триггеры, первый и второй мультиплексоры, первый элемент И, причем группы информа- ционньпс входов первого и второго мультиплексоров подключены к группе входов кода операции модуля, первые управляющие входы первого и второго мультиплексоров подключены к соответствующим входам данных модуля, вторые управляющие входы первого и второго мультиплексоров подключены к выходам триггеров нулевого и первого раз рядов и синхронным выходам дан-55 ных нулевого и первого разрядов модуля соответственно, информационные входы первого и второго D-триггеров

50

подключены к выходам соответственно первого и второго мультиплексоров, третий управляющий вход первого мультиплексора подключен к входу переноса модуля, третий управляющий вход второго мультиплексора подключен к выходу первого D-триггера, вход управления обработкой.переносов модуля подключен к входам синхронизации первого и второго D-триггеров и инверсному .входу первого элемента И, прямой вход первого элемента И подключен к тактовому входу модуля, выход первого элемента И подключен к.входам синхронизации триггеров нулевого и первого разрядов, выход второго D-триггёра подключен к выходу переноса модуля, информационные входы триггеров нулевого и первого разрядов подключены к асинхроннЕШ

выходам данных модуля, выходы триггеров нулевого и первого разрядов подключены к синхронным выходам данных модуля, отличающий- с я тем что, с целью сокращения числа внешних выводов, он содержит третий и четвер тый мультиплексоры, второй элемент И, причем группа входов второго элемента И подключена к группе входов кода операции модуля , выход второго элемента И подключен к управлякидим входам третьего и четвертого мультиплексоров, первые

информационные входы третьего и четвертого мультиплексоров подключены к выходам соответственно первого и второго мультиплексоров, выходы третьего и четвертого мультиплексоров подключены к информационным входам соответственно, триггеров нулевого и первого разрядов, второй информационный вход третьего мультиплексора подключен к выходу триг.гера первого разряда, второй информацион- ньш вход четвертого мультиплексора .подключен к в ходу сдвига вправо модуля,

TaHmoStK и(лу/гйсь(

Составитель В. Минаков Редактор С. Лисина Техред Н.Бонкало Корректор А. Обручар

Заказ 3294/5Г Тираж 67 . Подписное ВНИШИ Государственного комитета СССР .

по делам изобретений и открытий П3035, Москва, Ж-35 , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгороп, ул. ГТооектнля

Фие. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

| Арифметико-логический модуль | 1988 |

|

SU1501032A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Арифметико-логический модуль | 1980 |

|

SU962916A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Накапливающий сумматор | 1979 |

|

SU920708A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

Изобретение относится к области вычислительной техники и может найти применение при построении специализированных и универсальных ЭВМ. Целью изобретения является сокращение числа внешних выводов. С этой целью многофункциональный модуль кроме двух D-триггеров, двух мультиплексоров , элемента И .и триггеров нулевого и первого разрядов дополнительно содержит два мультиплексора и элемент И, соединение которых с остальными узлами схемы позволяет разбить все арифметико-логические операций на две группы. В первой из них результат операций в некотором разряде формируется исходя из заданного кода операции и значений операндов в этом разряде с учетом переносов в него справа и слева. Во второй группе результат операции в некотором разряде формируется без учета переносов в этот разряд. 2 ип., 1 табл. (Л

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-09-24—Подача