Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства систем сбора, регистрации и обработки измерительной информации.

Цель изобретения - повышение надеж- нести и расширение области применения устройства за счет возможности определения размера зоны записи.

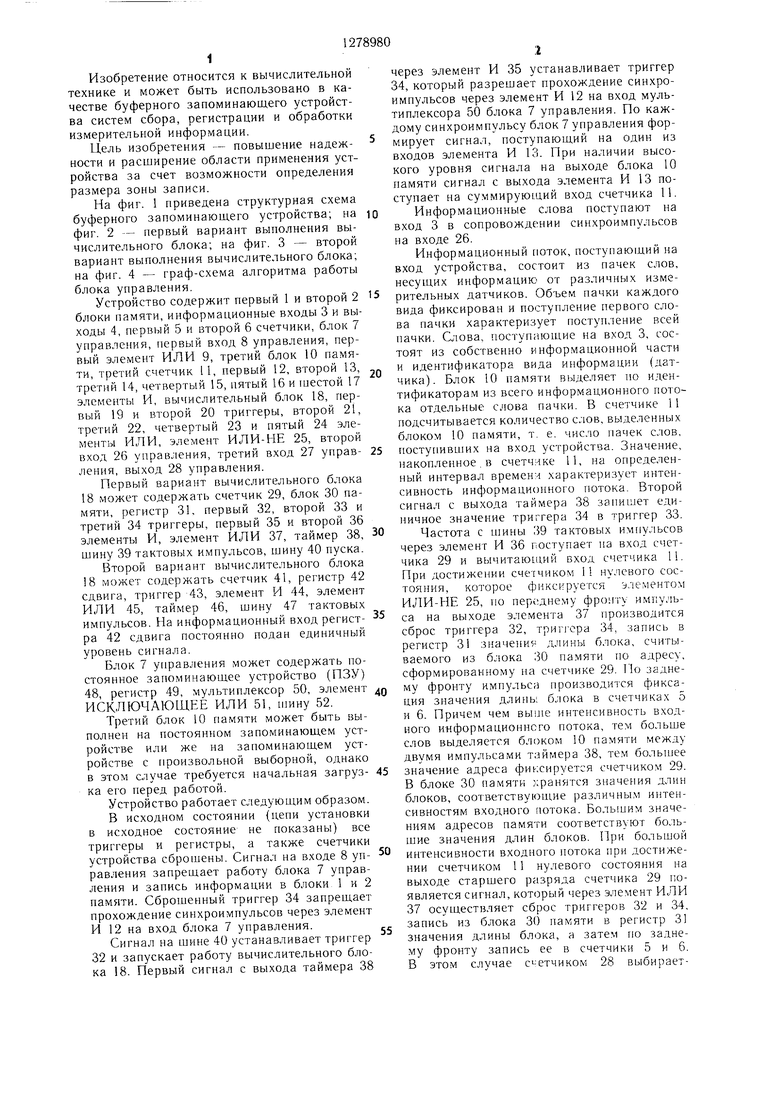

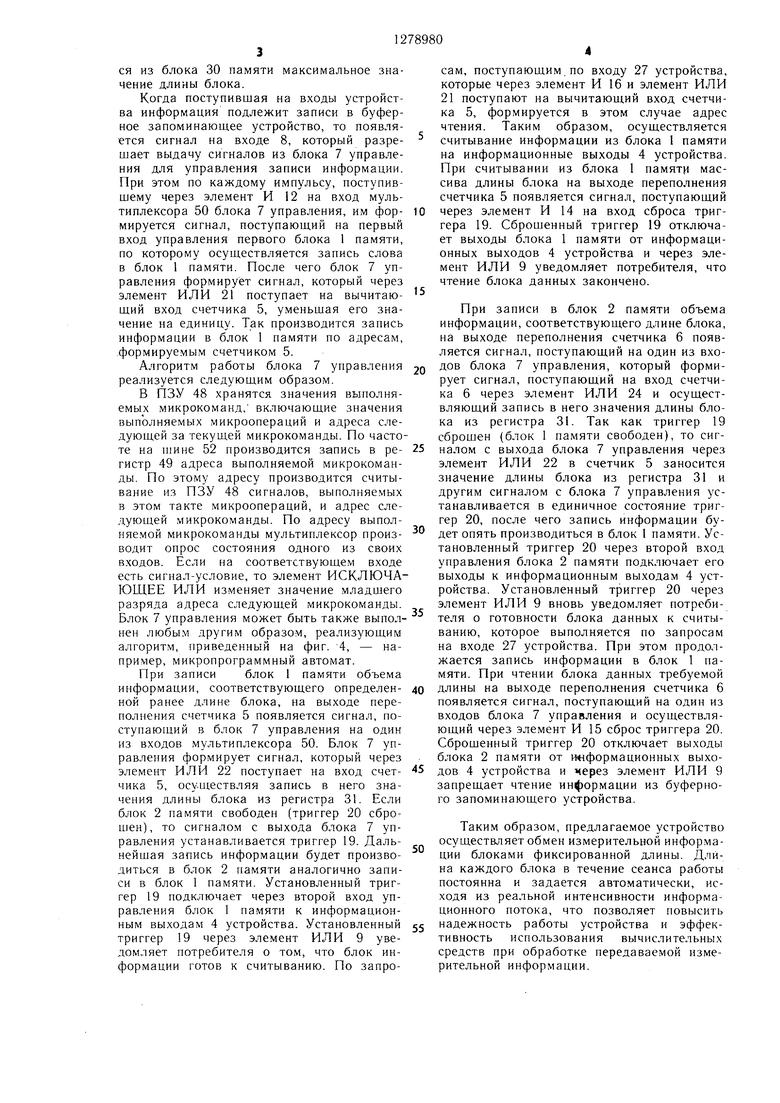

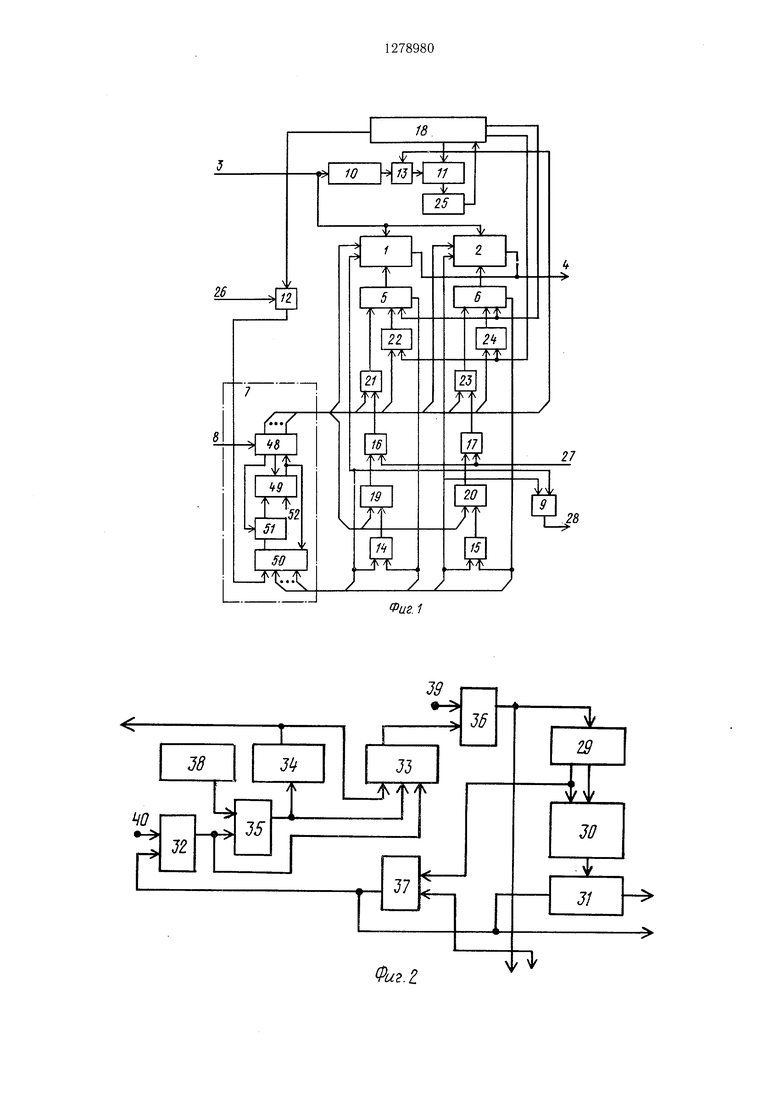

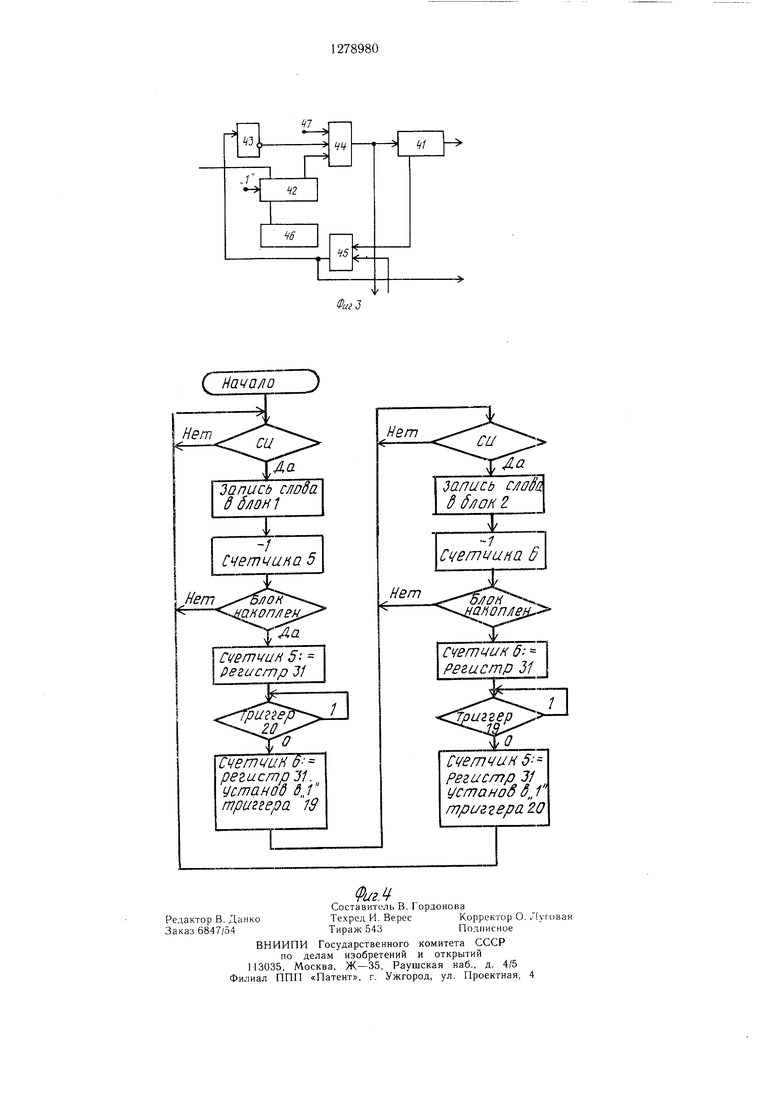

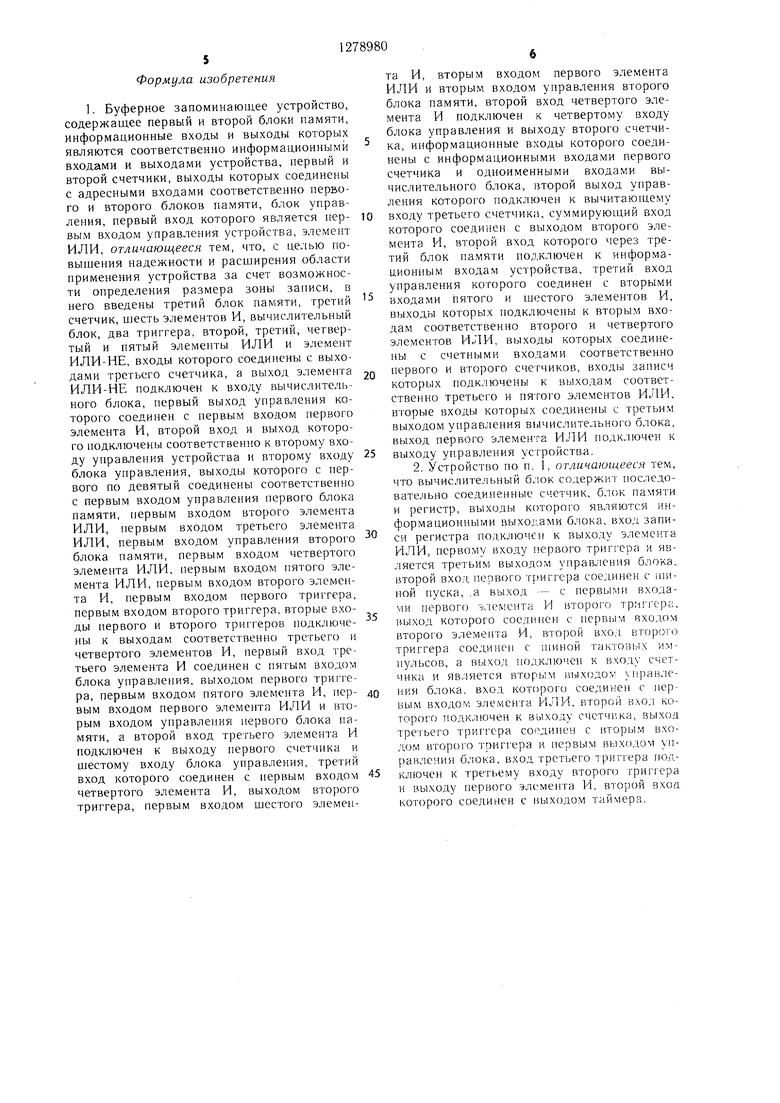

На фиг. 1 приведена структурная схема буферного запоминающего устройства; на ю фиг. 2 - первый вариант выполнения вычислительного блока; на фиг. 3 - второй вариант выполнения вычислительного блока; на фиг. 4 - граф-схема алгоритма работы блока управления.

через элемент И 35 устанавливает триггер 34, который разрешает прохождение синхроимпульсов через элемент И 12 на вход мультиплексора 50 блока 7 управления. По каждому синхроимпульсу блок 7 управления формирует сигнал, поступающий на один из входов элемента И 13. При наличии высокого уровня сигнала на выходе блока 10 памяти сигнал с выхода элемента И 13 поступает на суммирую1ций вход счетчика 11.

Информационные слова поступают на вход 3 в сопровождении синхроимпульсов на входе 26.

Информационный юток, поступающий на вход устройства, состоит из пачек слов, несущих информацию от различных измеУстройство содержит первый 1 и второй 2 15 рительных датчиков. Объем пачки каждого

блоки памяти, информационные входы 3 и выходы 4, первый 5 и второй 6 счетчики, блок 7 управления, первый вход 8 управления, первый элемент ИЛИ 9, третий блок 10 памявида фиксирован и поступление первого слова пачки характеризует поступление всей пачки. Слова, поступающие на вход 3, состоят из собственно информационной части

ги, третий счетчик 11, первый 12, второй 13, j и идентификатора вида информации (даттретий 14, четвертый 15, пятый 16 и шестой 17 элементы И, вычислительный блок 18, первый 19 и второй 20 триггеры, второй 21, третий 22, четвертый 23 и пятый 24 элементы ИЛИ, элемент ИЛИ-НЕ 25, второй

чика). Блок 10 памяти выделяет по иден- тификатора.м из всего информационного потока отдельные слова пачки. В счетчике 11 подсчитывается количество слов, выделенных блоком 10 памяти, т. е. число пачек слов.

вход 26 управления, третий вход 27 управ- 25 поступивших на вход устройства. Значение,

ления, выход 28 управления.

Первый вариант вычислительного блока 18 может содержать счетчик 29, блок 30 памяти, регистр 31, первый 32, второй 33 и третий 34 триггеры, первый 35 и второй 36 элементы И, элемент ИЛИ 37, таймер 38, 30 шину 39 тактовых импульсов, шину 40 пуска.

Второй вариант вычислительного блока 18 может содержать счетчик 41, регистр 42 сдвига, триггер 43, элемент И 44, элемент ИЛИ 45, таймер 46, шину 47 тактовых

импульсов. На информационный вход регист- 5 .д на выходе элемента 37 ра 42 сдвига постоянно подан единичный уровень сигнала.

Блок 7 управления может содержать постоянное запоминающее устройство (ПЗУ) 48, регистр 49, мультиплексор 50, элемент Q ИСКЛЮЧАЮЩЕЕ ИЛИ 51, 52.

Третий блок 10 памяти может быть выполнен на постоянном запоминающем устройстве или же на запоминающем устройстве с фоизвольной выборной, однако

накопленное,в счетчике 11, на определенный интервал времени характеризует интенсивность информационного потока. Второй сигнал с выхода таймера 38 занишет единичное значение триггера 34 в триггер 33. Частота с шины 39 тактовых импульсов через элемент И 36 поступает на вход счетчика 29 и вычитающий вход счетчика 11. При достижении счетчиком 1 нулевого состояния, которое фиксируется элементом ИЛИ-НЕ 25, по переднему фронту имггу льпроизводится

сброс триггера 32, трип-ера 34, запись в регистр 31 значени5- длины блока, считываемого из блока 30 памяти по адресу, сформированному на счетчике 29. По заднему фронту импульса производится фиксация значения длины блока в счетчиках 5 и 6. Причем чем выше интенсивность входного информационного потока, тем больше слов выделяется блоком 10 памяти между двумя импульсами таймера 38, тем больн1ее

в этом случае требуется начальная загруз- 45 значение адреса фиксируется счетчиком 29.

ка его перед работой.

Устройство работает следующим образом.

В исходном состоянии (цепи установки в исходное состояние не показаны) все триггеры и регистры, а также счетчики

В блоке 30 памяти /хранятся значения длин блоков, соответствующие различным иптен- сивностям входного потока. Больп:им значениям адресов памяти соответствуют большие значения длин блоков. При большой

устройства сброшены. Сигнал на входе 8 уп- интенсивности входного потока при достижеравления запрещает работу блока 7 управления и запись информации в блоки 1 и 2 памяти. Сброшенный триггер 34 запрещает прохождение синхроимпульсов через элемент И 12 на вход блока 7 управления.

Сигнал на щине 40 устанавливает триггер 32 и запускает работу вычислительного блока 18. Первый сигнал с выхода таймера 38

55

НИИ счетчиком 11 нулевого состояния на выходе старщего разряда счетчика 29 появляется сигнал, который через элемент ИЛИ 37 осуществляет сброс триггеров 32 и 34, запись из блока 3() памяти в регистр 31 значения длины блока, а затем но заднему фронту запись ее в счетчики 5 и 6. В этом случае С1 етчиком 28 выбирает

ю

2

через элемент И 35 устанавливает триггер 34, который разрешает прохождение синхроимпульсов через элемент И 12 на вход мультиплексора 50 блока 7 управления. По каждому синхроимпульсу блок 7 управления формирует сигнал, поступающий на один из входов элемента И 13. При наличии высокого уровня сигнала на выходе блока 10 памяти сигнал с выхода элемента И 13 поступает на суммирую1ций вход счетчика 11.

Информационные слова поступают на вход 3 в сопровождении синхроимпульсов на входе 26.

Информационный юток, поступающий на вход устройства, состоит из пачек слов, несущих информацию от различных изме15 рительных датчиков. Объем пачки каждого

рительных датчиков. Объем пачки каждого

вида фиксирован и поступление первого слова пачки характеризует поступление всей пачки. Слова, поступающие на вход 3, состоят из собственно информационной части

и идентификатора вида информации (датчика). Блок 10 памяти выделяет по иден- тификатора.м из всего информационного потока отдельные слова пачки. В счетчике 11 подсчитывается количество слов, выделенных блоком 10 памяти, т. е. число пачек слов.

.д на выходе элемента 37

накопленное,в счетчике 11, на определенный интервал времени характеризует интенсивность информационного потока. Второй сигнал с выхода таймера 38 занишет единичное значение триггера 34 в триггер 33. Частота с шины 39 тактовых импульсов через элемент И 36 поступает на вход счетчика 29 и вычитающий вход счетчика 11. При достижении счетчиком 1 нулевого состояния, которое фиксируется элементом ИЛИ-НЕ 25, по переднему фронту имггу льпроизводится

сброс триггера 32, трип-ера 34, запись в регистр 31 значени5- длины блока, считываемого из блока 30 памяти по адресу, сформированному на счетчике 29. По заднему фронту импульса производится фиксация значения длины блока в счетчиках 5 и 6. Причем чем выше интенсивность входного информационного потока, тем больше слов выделяется блоком 10 памяти между двумя импульсами таймера 38, тем больн1ее

В блоке 30 памяти /хранятся значения длин блоков, соответствующие различным иптен- сивностям входного потока. Больп:им значениям адресов памяти соответствуют большие значения длин блоков. При большой

интенсивности входного потока при достиже

НИИ счетчиком 11 нулевого состояния на выходе старщего разряда счетчика 29 появляется сигнал, который через элемент ИЛИ 37 осуществляет сброс триггеров 32 и 34, запись из блока 3() памяти в регистр 31 значения длины блока, а затем но заднему фронту запись ее в счетчики 5 и 6. В этом случае С1 етчиком 28 выбирается из блока 30 памяти максимальное значение длины блока.

Когда поступившая на входы устройства информация подлежит записи в буферное запоминающее устройство, то появляется сигнал на входе 8, который разрешает выдачу сигналов из блока 7 управления для управления записи информации. При этом по каждому импульсу, поступившему через элемент И 12 на вход мульсам, поступающим по входу 27 устройства, которые через элемент И 16 и элемент ИЛИ 21 поступают на вычитающий вход счетчика 5, формируется в этом случае адрес чтения. Таким образом, осуществляется считывание информации из блока 1 памяти на информационные выходы 4 устройства. При считывании из блока 1 памяти массива длины блока на выходе переполнения счетчика 5 появляется сигнал, поступающий

типлексора 50 блока 7 управления, им фор- 10 через элемент И 14 на вход сброса триг- мируется сигнал, поступающий на первыйгера 19. Сброщенный триггер 19 отключает выходы блока 1 памяти от информационных выходов 4 устройства и через элевход управления первого блока 1 памяти, по которому осуществляется запись слова в блок 1 памяти. После чего блок 7 управления формирует сигнал, который через элемент ИЛИ 21 поступает на вычитаю- щий вход счетчика 5, уменьшая его значение на единицу. Так производится запись информации в блок 1 памяти по адресам, .формируемым счетчиком 5.

мент ИЛИ 9 уведомляет потребителя, что чтение блока данных закончено.

ка 6 через элемент ИЛИ 24 и осуществляющий запись в него значения длины блока из регистра 31. Так как триггер 19

сброшен (блок 1 памяти свободен), то сигПри записи в блок 2 памяти объема информации, соответствующего длине блока, на выходе переполнения счетчика 6 появляется сигнал, поступающий на один из вхоАлгоритм работы блока 7 управления 20 блока 7 управления, который форми- реализуется следующим образом.рует сигнал, поступающий на вход счетчиВ ПЗУ 48 хранятся значения выполняемых микрокоманд, включающие значения выполняемых микроопераций и адреса следующей за текущей микрокоманды. По частоте на тине 52 производится запись в ре- 25 налом с выхода блока 7 управления через гистр 49 адреса выполняемой микрокоман-элемент ИЛИ 22 в счетчик 5 заносится

ды. По этому адресу производится считы-значение длины блока из регистра 31 и

вание из ПЗУ 48 сигналов, выполняемыхдругим сигналом с блока 7 управления усв этом такте микроопераций, и адрес еле-танавливается в единичное состояние тригдующей микрокоманды. По адресу выпол-гер 20, после чего запись информации буняемой микрокоманды мультиплексор произ- дет опять производиться в блок 1 памяти. Установленный триггер 20 через второй вход управления блока 2 памяти подключает его выходы к информационным выходам 4 устройства. Установленный триггер 20 через

,.„,.,.,„ „,,,,„ „.„,.I„..„„..элемент ИЛИ 9 вновь уведомляет потребиБлок 7 управления может быть также выпол- теля о готовности блока данных к считы- нен любы.м другим образом, реализующимванию, которое выполняется по запросам

алгоритм, приведенный на фиг. -4, - на-на входе 27 устройства. При этом продолпример, микропрограммный автомат.жается запись информации в блок 1 паПри записи блок 1 памяти объемамяти. При чтении блока данных требуемой

информации, соответствующего определен- 40 длины на выходе переполнения счетчика б ной ранее длине блока, на выходе пере-появляется сигнал, поступающий на один из

полнения счетчика 5 появляется сигнал, по-входов блока 7 управления и осуществляступающий в блок 7 управления на одинющий через элемент И 15 сброс триггера 20.

из входов мультиплексора 50. Блок 7 уп-Сброщенный триггер 20 отключает выходы

равления формирует сигнал, который черезблока 2 памяти от информационных выхоэлемент ИЛИ 22 поступает на вход счет- 5 дов 4 устройства и через элемент ИЛИ 9 чика 5, осуществляя запись в него зна-запрещает чтение информации из буферноводит опрос состояния одного из своих входов. Если на соответствующем входе есть сигнал-условие, то элемент ИСКЛЮЧАЮЩЕЕ ИЛИ изменяет значение младшего разряда адреса следующей микрокоманды.

чения длины блока из регистра 31. Если блок 2 памяти свободен (триггер 20 сброшен), то сигналом с выхода блока 7 управления устанавливается триггер 19. Дальнейшая запись информации будет производиться в блок 2 памяти аналогично записи в блок 1 памяти. Установленный триггер 19 подключает через второй вход управления блок 1 памяти к информацион50

го запоминающего устройства.

Таким образом, предлагаемое устройство осуществляет обмен измерительной информации блоками фиксированной длины. Длина каждого блока в течение сеанса работы постоянна и задается автоматически, исходя из реальной интенсивности информационного потока, что позволяет повысить

ным выходам 4 устройства. Установленный55 надежность работы устройства и эффектриггер 19 через элемент ИЛИ 9 уве-тивность использования вычислительных

домляет потребителя о том, что блок ин-средств при обработке передаваемой измеформации готов к считыванию. По запро-рительной информации.

сам, поступающим по входу 27 устройства, которые через элемент И 16 и элемент ИЛИ 21 поступают на вычитающий вход счетчика 5, формируется в этом случае адрес чтения. Таким образом, осуществляется считывание информации из блока 1 памяти на информационные выходы 4 устройства. При считывании из блока 1 памяти массива длины блока на выходе переполнения счетчика 5 появляется сигнал, поступающий

через элемент И 14 на вход сброса триг- гера 19. Сброщенный триггер 19 отключает выходы блока 1 памяти от информационных выходов 4 устройства и через элемент ИЛИ 9 уведомляет потребителя, что чтение блока данных закончено.

ка 6 через элемент ИЛИ 24 и осуществляющий запись в него значения длины блока из регистра 31. Так как триггер 19

сброшен (блок 1 памяти свободен), то сиг блока 7 управления, который форми- рует сигнал, поступающий на вход счетчи налом с выхода блока 7 управления через элемент ИЛИ 22 в счетчик 5 заносится

го запоминающего устройства.

Таким образом, предлагаемое устройство осуществляет обмен измерительной информации блоками фиксированной длины. Длина каждого блока в течение сеанса работы постоянна и задается автоматически, исходя из реальной интенсивности информационного потока, что позволяет повысить

Формула изобретения

1. Буферное запоминающее устройство, содержащее первый и второй блоки памяти, информационные входы и выходы которых являются соответственно информационными входами и выходами устройства, первый и второй счетчики, выходы которых соединены с адресными входами соответственно первого и второго блоков намяти, блок управления, первый вход которого является первым вхолтом управления устройства, элемент ИЛИ, отличающееся тем, что, с целью повышения надежности и расширения области применения устройства за счет возможности определения размера зоны записи, в него введены третий блок памяти, третий счетчик, шесть элементов И, вычислительный блок, два триггера, второй, третий, четвертый и пятый элементы ИЛИ и элемент ИЛИ-НЕ, входы которого соединены с выходами третьего счетчика, а выход элемента ИЛИ-НЕ подключен к входу вычислительного блока, первый выход управления которого соединен с первым входом первого элемента И, второй вход и выход которого подключен з1 соответственно к второму входу управления устройства и второму входу блока управления, выходы которого с первого по девятый соединены соответственно с первым входом управления первого блока намяти, первым входом второго элемента ИЛИ, первым входом третьего элемента ИЛИ, первым входом управления второго блока памяти, первым входом четвертого элемента ИЛИ, первым входом пятого элемента ИЛИ, первым входом второго элемента И, первым входом первого триггера, первым входом второго триггера, вторые входы первого и второго триггеров подключены к выходам соответственно третьего и четвертого элементов И, первый вход третьего элемента И соединен с пятым входом блока управления, выходом первого триггера, первым входом пятого элемента И, первым входом первого элемента ИЛИ и вторым входом управления первого блока памяти, а второй вход третьего элемента И подключен к выходу первого счетчика и шестому входу блока управления, третий вход которого соединен с первым входом четвертого элемента И, выходом второго триггера, первым входом шестого элемеп

та И, вторым входом первого элемента ИЛИ и вторым входом управления второго блока памяти, второй вход четвертого элемента И подключен к четвертому входу блока управления и выходу второго счетчи- ка, информационные входы которого соединены с информационными входами первого счетчика и одноименными входами вычислительного блока, второй выход управления которого подключен к вычитаюпхему

входу третьего счетчика, суммирующий вход которого соединен с выходом второго элемента И, второй вход которого через третий блок памяти подключен к информационным входам устройства, третий вход управления которого соедине 1 с вторыми входами пятого и шестого элементов И, выходы которых подключены к вторым входам соответственно второго и четвертого элементов ИЛИ, выходы которых соединены с счетными входами соответственно

первого и второго счетчиков, входы записи которых подключены к выходам соответственно третьего и пятого элементов ИЛИ, вторые входы которых соединены с третьим выходом управления вычис.чительного блока, выход первого элемента ИЛИ подключен к

выходу управления устройства.

2. Устройство по п. 1, отличающееся тем, что вычислительный блок содержит последо- вате.пьно соединенные счетчик, блок памяти и регистр, выходы которого являются информационными выходами блока, вход записи регистра подключен к выходу элемента ИЛИ, первому входу первого триггера и является третьим выходом управления блока, второй вход первого т)иггера соединен с шиной пуска, ,а выход - с первыми входами первого -).лемснта И второго триггера, выход которого соедипеп с первым входом второго элемеш а И, второй вход второго триггера соедипеп с шиной тактовгчх импульсов, а выход подключен к счетчика и является вторым ИЫХОДОУ Г paвлeПИЯ блока, вход которого соединен с первым входом элемента ИЛИ, второй 15ло;1 которого подключен к выходу счстчг.ка, выход третьего триггера соединен с вторым входом второго триггера и первым выход.ом управления блока, вход третьего триггера по.ак.пючен к третьему входу второго триггера и выходу первого элемепта И, второй вход которого соединен с выходом таймера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для магнитной записи цифровой информации | 1985 |

|

SU1224823A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для буферизации информации | 1988 |

|

SU1559350A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1316050A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

Изобретение может быть использовано для группирования данных информационных потоков неравномерной интенсивности. имеющих определенную цикличность и постоянное среднее значенпе интенсивности в блоке обмена. Цель изобретения состоит в повышении надежности и расширении области применения устройства за счет автоматического определения размера блоков обмена, исходя из реальной интенсивности потока с учетом требований исключения потерь информации и удобства последующей ее обработки. Устройство может быть использовано в качестве буферного в блоках регистрации цифровой информации на основе стартстопных накопителей на магнитной ленте для предварительной регистрации информационных потоков. I 3.11. ф-ЛЫ, 4 И.1. со 00

(ача/10 j

Запись слода д длои 1

запись cjjoHi. 8 блок 2

I

-/ Счет1-{ика 5

Ci/emL/ина о

Нет

Ла

5- - Dezacmp J/

, --..jmftQnj ti

Счвтцин 6: 1

Регистр J/ J

3

СчетциН 6 регисглр Л. Устаноб dj триггера 19

Фиг

Редактор В. Данко Заказ 6847/54

. гМ

Составитель В. Гордонова

Техред И. ВересКорректор О

Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, , Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная,

Cvenr UH 5- регистр J/ у ста нов dj триггера 20

Фиг

. г

авит

| Буферное запоминающее устройство | 1979 |

|

SU822293A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1978 |

|

SU767836A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-10—Подача