Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, а также в станках с программным управлением, в которых использованы линейные и матричные исполнительные органы.

Цель изобретения повышение быстродействия интерполятора.

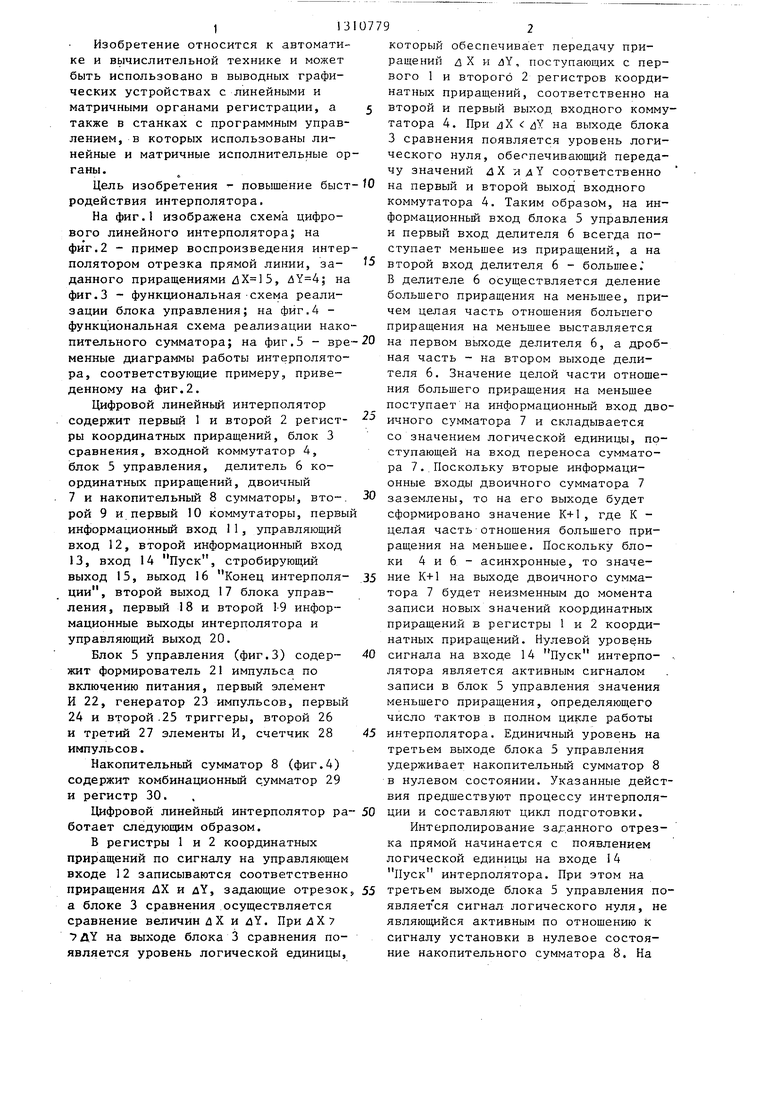

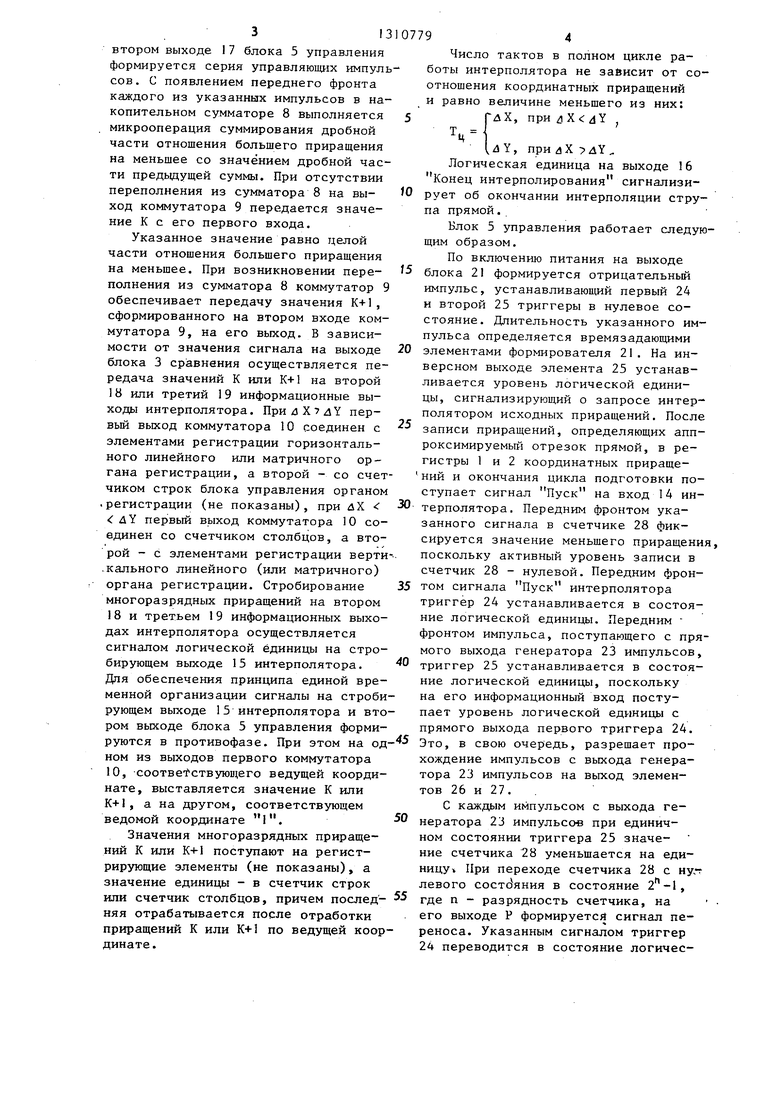

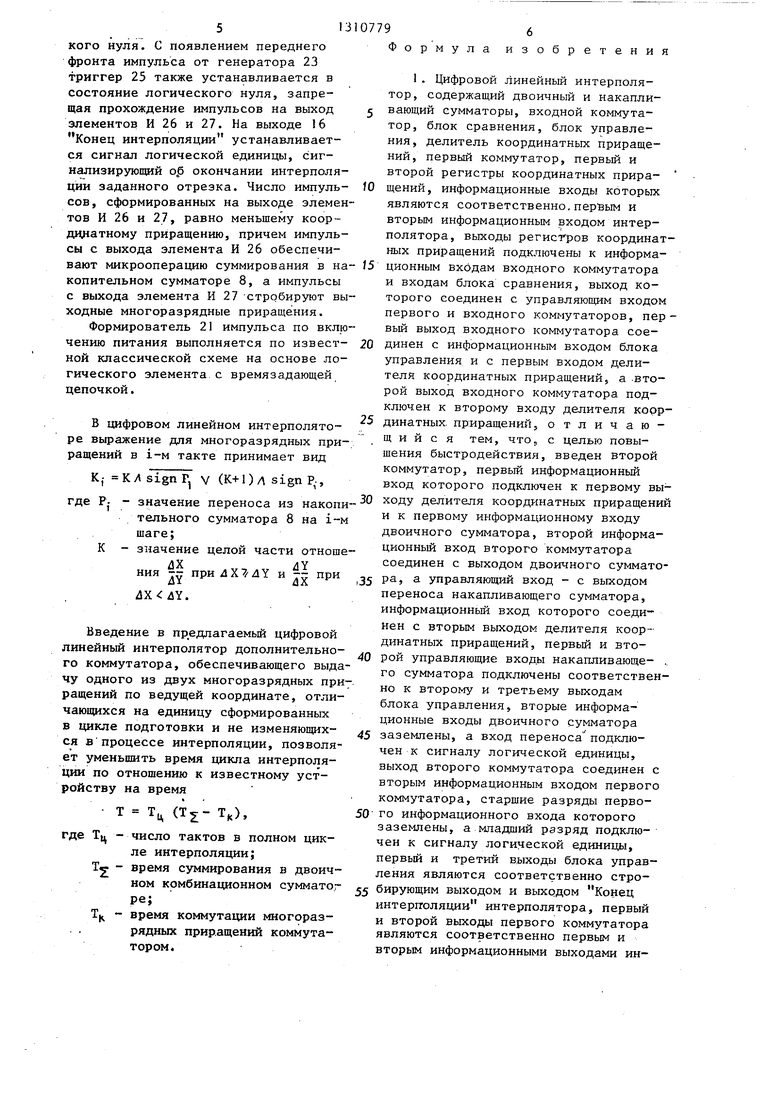

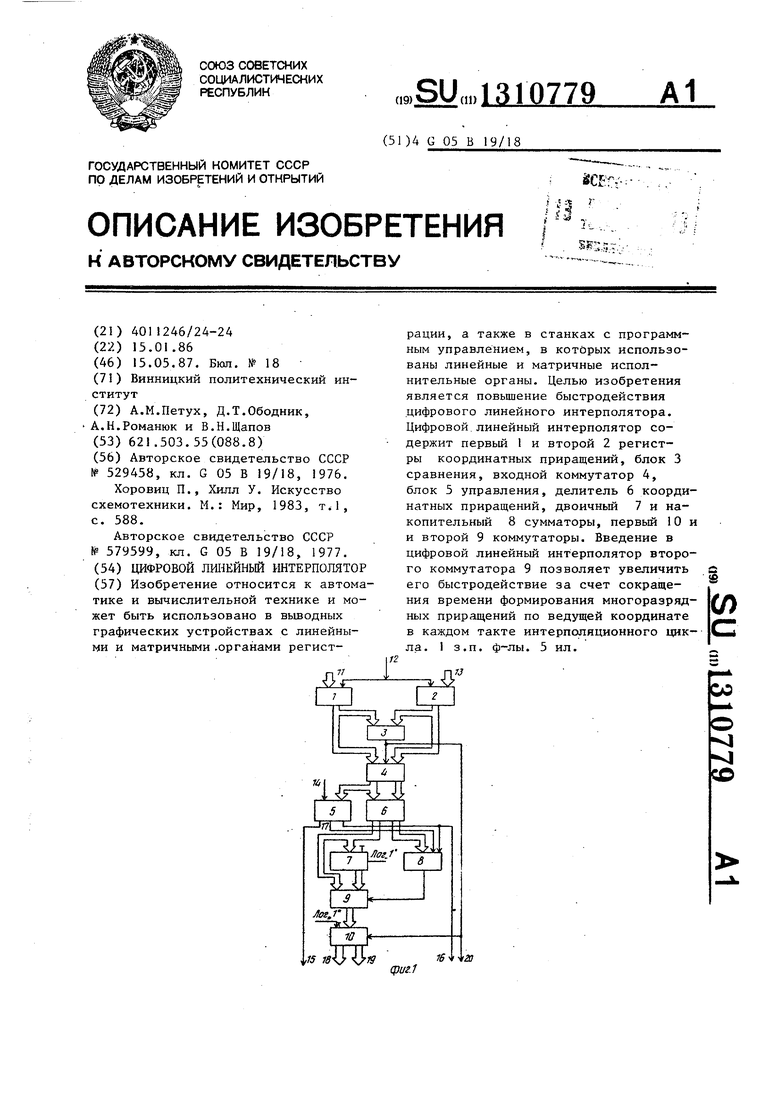

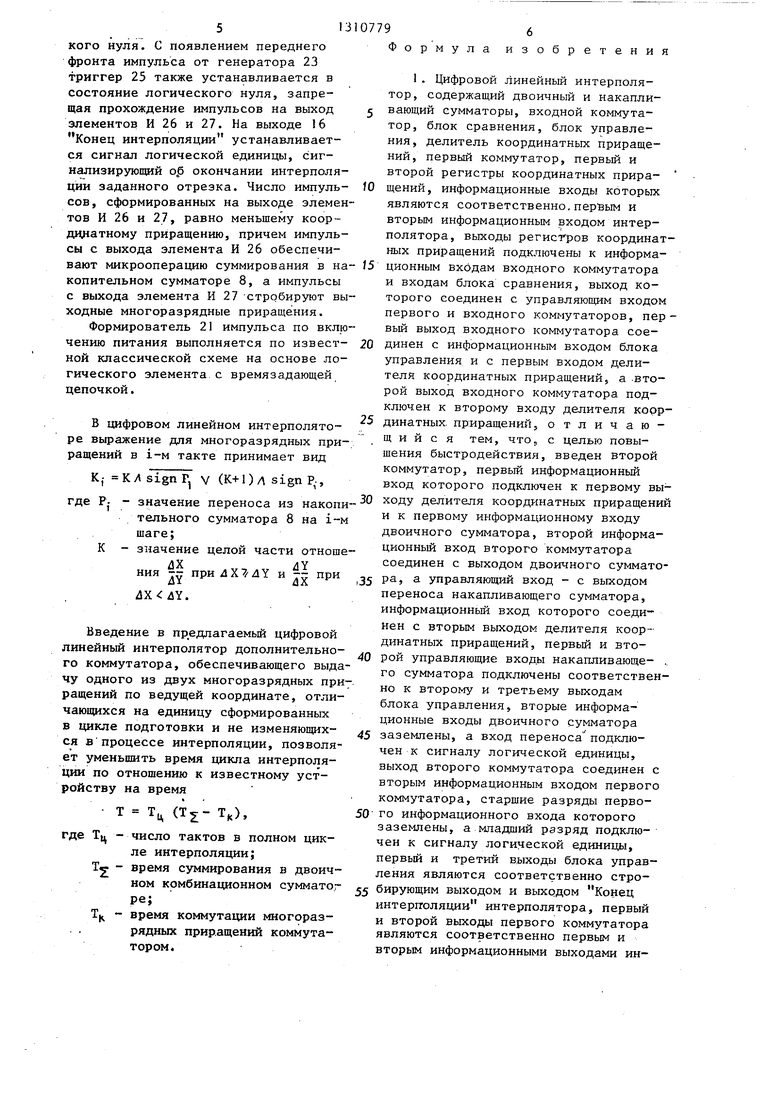

На фиг.1 изображена схема цифрового линейного интерполятора; на фи г.2 - пример воспроизведения интерполятором отрезка прямой линии, заданного приращениями , на фиг.З - функциональная схема реализации блока управления; на фиг.4 - функциональная схема реализации накопительного сумматора; на фиг.З - временные диаграммы работы интерполятора, соответствующие примеру, приведенному на фиг.2.

Цифровой линейный интерполятор содержит первый 1 и второй 2 регистры координатных приращений, блок 3 сравнения, входной коммутатор 4, блок 5 управления, делитель 6 координатных приращений, двоичный 7 и накопительный 8 сумматоры, вто-. рой 9 и первый 10 коммутаторы, первы информационный вход 11, управляющий вход 12, второй информационный вход 13, вход 14 Пуск, стробирующий выход 15, выход 16 Конец интерполяции , второй выход 17 блока управления, первый 18 и второй 1-9 информационные выходы интерполятора и управляющий выход 20.

Блок 5 управления (фиг.З) содержит формирователь 21 импульса по включению питания, первый элемент И 22, генератор 23 импульсов, первый 24 и второй .25 триггеры, второй 26 и третий 27 элементы И, счетчик 28 импульсов.

Накопительный сумматор 8 (фиг.4) содержит комбинационный с.умматор 29 и регистр 30.

Цифровой линейный интерполятор работает следующим образом.

В регистры 1 и 2 координатных приращений по сигналу на управляющем входе 12 записываются соответственно приращения ЛХ и дУ, задающие отрезок а блоке 3 сравнения осуществляется сравнение величин лХ и aY. При 4X7 7 ДУ на выходе блока 3 сравнения появляется уровень логической единицы.

5

779 .2

который обеспечивает передачу приращений лХ и лУ, поступающих с первого 1 и второго 2 регистров координатных приращений, соответственно на

5 второй и первый выход, входного коммутатора 4. При Х : У на выходе блока 3 сравнения появляется уровень логического нуля, обеспечивающий передачу значений лХ идУ соответственно

O на первый и второй выход входного коммутатора 4. Таким образом, на ин- формационньй вход блока 5 управления и первый вход делителя 6 всегда поступает меньшее из приращений, а на

5 второй вход Делителя 6 - большее. В делителе 6 осуществляется деление большего приращения на меньшее, причем целая часть отношения болычего приращения на меньшее выставляется

0 на первом выходе делителя 6, а дробная часть - на втором выходе делителя 6. Значение целой части отношения большего приращения на меньшее поступает на информационный вход двоичного сумматора 7 и складывается со значением логической единицы, поступающей на вход переноса сумматора 7..Поскольку вторые информационные входы двоичного сумматора 7 заземлены, то на его выходе будет сформировано значение К+1, где К - целая часть отношения большего приращения на меньшее. Поскольку блоки 4 и 6 - асинхронные, то значе5 ние К+1 на выходе двоичного сумматора 7 будет неизменным до момента записи новых значений координатных приращений в регистры 1 и 2 координатных приращений. Нулевой уровень

0 сигнала на входе 14 Пуск интерполятора является активным сигналом записи в блок 5 управления значения меньшего приращения, определяющего число тактов в полном цикле работы

5 интерполятора. Единичный уровень на третьем выходе блока 5 управления удерживает накопительный сумматор 8 в нулевом состоянии. Указанные действия предшествуют процессу интерполя0 ции и составляют цикл подготовки.

Интерполирование зар.анного отрезка прямой начинается с появлением логической единицы на входе 14 Пуск интерполятора. При этом на

5 третьем выходе блока 5 управления по- являет ся сигнал логического нуля, не являющийся активным по отношению к сигналу установки в нулевое состояние накопительного сумматора 8. На

0

313

втором выходе 17 блока 5 управления формируется серия управляющих импуль сов. С появлением переднего фронта каждого из указанных импульсов в накопительном сумматоре 8 выполняется микрооперация суммирования дробной части отношения большего приращения на меньшее со значением дробной части предьщущей суммы. При отсутствии переполнения из сумматора 8 на выход коммутатора 9 передается значение К с его первого входа.

Указанное значение равно целой части отношения большего приращения на меньшее. При возникновении переполнения из сумматора 8 коммутатор 9 обеспечивает передачу значения К+1, сформированного на втором входе коммутатора 9, на его выход. В зависимости от значения сигнала на выходе блока 3 сравнения осуществляется передача значений К или К+1 на второй 18 или третий 19 информационные выходы интерполятора. ПрилХ лУ первый выход коммутатора 10 соединен с элементами регистрации горизонтального линейного или матричного органа регистрации, а второй - со счетчиком строк блока управления органом .регистрации (не показаны), при ДХ Г ДУ первый выход коммутатора 10 соединен со счетчиком столбцов, а второй - с элементами регистрации верти .кального линейного (или матричного) органа регистрации. Стробирование многоразрядных приращений на втором 18 и третьем 19 информационных выходах интерполятора осуществляется сигналом логической единицы на стро- бирующем выходе 15 интерполятора. Для обеспечения принципа единой временной организации сигналы на строби рующем выходе 15 интерполятора и втором выходе блока 5 управления формируются в противофазе. При этом на одном из выходов первого коммутатора 10, соответствующего ведущей координате, выставляется значение К или К+1, а на другом, соответствующем ведомой координате 1.

Значения многоразрядных приращений К или Кн-1 поступают на регистрирующие элементы (не показаны), а значение единицы - в счетчик строк или счетчик столбцов, причем последняя отрабатывается после отработки приращений К или К+1 по ведущей коор динате.

94

Число тактов в полном цикле работы интерполятора не зависит от соотношения координатных приращений и равно величине меньшего из них:

ГЛХ, при /3 X dY

1,4 Y, при dX ул1

Логическая единица на выходе 16 Конец интерполирования сигнализирует об окончании интерполяции струпа прямой.

Блок 5 управления работает следующим образом.

По включению питания на выходе

блока 21 формируется отрицательный импульс, устанавливающий первый 24 и второй 25 триггеры в нулевое состояние. Длительность указанного импульса определяется времязадающими

элементами формирователя 21. На инверсном выходе элемента 25 устанавливается уровень логической единицы, сигнализирующий о запросе интерполятором исходных приращений. После

записи приращений, определяющих аппроксимируемый отрезок прямой, в регистры 1 и 2 координатных прираще- ний и окончания цикла подготовки поступает сигнал Пуск на вход 14 интерполятора. Передним фронтом указанного сигнала в счетчике 28 фиксируется значение меньшего приращения, поскольку активный уровень записи в счетчик 28 - нулевой. Передним фронтом сигнала Пуск интерполятора

триггер 24 устанавливается в состояние логической единицы. Передним фронтом импульса, поступающего с прямого выхода генератора 23 импульсов,

триггер 23 устанавливается в состояние логической единицы, поскольку на его информационный вход поступает уровень логической единицы с прямого выхода первого триггера 24.

Это, в свою очередь, разрешает прохождение импульсов с выхода генератора 23 импульсов на выход элементов 26 и 27.

С каждым импульсом с выхода генератора 23 импульсов при единичном состоянии триггера 25 значение счетчика 28 уменьшается на единицу При переходе счетчика 28 с ну,-;- левого состо яния в состояние ,

где п - разрядность счетчика, на его выходе Р формируете } сигнал переноса. Указанным сигналом триггер 24 переводится в состояние логичес513

кого нуля, с появлением переднего фронта импульса от генератора 23 триггер 25 также устанавливается в состояиие логического нуля, запрещая прохождение импульсов на выход элементов И 26 и 27. На выходе 16 Конец интерполяции устанавливается сигнал логической единицы, сигнализирующий ор окончании интерполяции заданного отрезка. Число импульсов, сформированных на выходе элементов И 26 и 27, равно меньшему коор- дчдатному приращению, причем импульсы с выхода элемента И 26 обеспечивают микрооперацию суммирования в накопительном сумматоре 8, а импульсы с выхода элемента И 27 -стробируют выходные многоразрядные приращения.

Формирователь 21 импульса по включению питания выполняется по известной классической схеме на основе логического элемента с времязадающей цепочкой.

В цифровом линейном интерполяторе выражение для многоразрядных приращений в i-M такте принимает вид

К/sign Г, V (К+1)л sign Р,-,

- значение переноса из накопительного сумматора 8 на i-м шаге; - значение целой части отношеЛ YЛ V

ния -г; приЛХ Т ЛУ И -- при Лхал

.

Введение в предлагаемьй цифровой линейный интерполятор дополнительного коммутатора, обеспечивающего выдачу одного из двух многоразрядных приращений по ведущей координате, отличающихся на единицу сформированных в цикле подготовки и не изменяющихся в процессе интерполяции, позволяет уменьшить время цикла интерполяции по отношению к известному устройству на время

Т Tj (Tj-- Т),

где Тц - число тактов в полном цикле интерполяции;

Т- - время суммирования в двоичном комбинационном сумматог ре;

Т( - время коммутации многоразрядных приращений коммутатором.

6

Формула изобретения

1. Цифровой линейный интерполятор, содержащий двоичный и накапливающий сумматоры, входной коммутатор, блок сравнения, блок управления, делитель координатных приращений, первый коммутатор, первый и второй регистры координатных приращений, информационные входы которьпс являются соответственно,первым и вторым информационньи входом интерполятора, выходы регистров координатных приращений подключены к информацнонным входам входного коммутатора и входам блока сравнения, выход которого соединен с управляющим входом первого и входного коммутаторов, первый выход входного коммутатора соединен с информационным входом блока управления и с первым входом делителя координатных приращений, а .второй выход входного коммутатора подключен к второму входу делителя коррдинатных- приращений,, отличающийся тем, ЧТО; с целью повышения быстродействия, введен второй коммутатор, первый информационный вход которого подключен к первому выходу делителя координатных приращений и к первому информационному входу двоичного сумматора, второй информационный вход второго коммутатора соединен с выходом двоичного сумматоРа, а управляющий вход - с выходом переноса накапливающего сумматора, информационный вход которого соединен с вторым выходом делителя координатных приращений, первый и второй управляющие входы накапливающе- , го сумматора подключены соответственно к второму и третьему выходам блока управления, вторые информационные входы двоичного сумматора

заземлены, а вход переноса подключен к сигналу логической единицы, выход второго коммутатора соединен с вторым информационным входом первого коммутатора, старшие разряды первого информационного входа которого заземлены, а младший разряд подключен к сигналу логической единицы, первый и третий выходы блока управления являются соответственно стробирующим выходом и выходом Конец интерп оляции интерполятора, первый и второй выходь первого коммутатора являются соответственно первым и вторым информационными выходами интерполятора, выход блока сравнения является управляющим выходом интерполятора, управляюпщй вход интерпо-г лятора подключен к управляющим входам первого и второго регистров координатных приращений, а вход Пуск интерполятора соединен с управляющим входом блока управления.

2. Интерполятор по п. 1, о т л и- чающийся тем, что блок управления содержит формирователь импульса по включению питания, генератор импульсов, первый и второй D-триггер первый, второй и третий элементы И, счетчик, информационные входы которого являются информационными входами блока, а первый управляющий вход соединен с управляющим входом первого D-триггера и является управляющим входом интерполятора, второй управляющий вход соединен с выходом второго элемента И, а выход пе-гки-авьер, , аю3107798

реноса - с первым входом первого элемента И, второй вход которого соединен с выходом формирователя импульса по включению питания и устано5 i вочным R-входом второго D-триггера, а выход - с установочным R-входом первого и-триггера, информационный вход которого подключен к сигналу логической единицы, а выход.- к инJO формационному входу второго D-триггера, управляющий вход котороголсоединен с прямым выходом генератора импульса и первым входом второго элемента И, а выход - с вторым входом второго и-первым входом третьего элементов И, инверсный выход генератора подключен к второму входу третьего элемента И, выход которого является первым выходом блока, выход вто20 рого элемента И и инверсный выход второго и-триггера являются соответственно вторым и третьим выходами блока.

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными .органами регистрации, а также в станках с программным управлением, в которых использованы линейные и матричные исполнительные органы. Целью изобретения является повышение быстродействия цифрового линейного интерполятора. Цифровой линейный интерполятор содержит первый 1 и второй 2 регистры координатных приращений, блок 3 сравнения, входной коммутатор 4, блок 5 управления, делитель 6 координатных приращений, двоичный 7 и накопительный 8 сумматоры, первый 10 и и второй 9 коммутаторы. Введение в цифровой линейный интерполятор второго коммутатора 9 позволяет увеличить его быстродействие за счет сокращения времени формирования многоразрядных приращений по ведущей координате в каждом такте интерполяционного цикла . 1 3.п. ф-лы. 5 ил. (Л с 15 (ригЛ 00 со

789 fO f

Ну 4

12 ГЗ /« /

Фсг&.2

0/п а 4

усм

П

21

1

22

27

и

/4

J7

rf

фиг.З

-V

6

29

1

16

1

77

25

Г6

1/

Т)

3D

0

С R

К 5лому9

cfJae.4

Редактор Е.Копча

Составитель И.Швец Техред .л. Сердюкова

Заказ 1889/43 Тираж 864Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород ул.Проектная, 4

(pf/ff.5

Корректор М.Демчик

| Цифровой линейный интерполятор | 1975 |

|

SU529458A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Хоровиц П., Хилл У | |||

| Искусство схемотехники | |||

| М.: Мир, 1983, т.1, с | |||

| Искроудержатель для паровозов | 1920 |

|

SU588A1 |

| Цифровой линейный интерполятор | 1976 |

|

SU579599A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-15—Подача