дов связан с первым входом первого блока внутрирегистрового сдвига кодов, первый выход которого через второй блок запоминания кодов соединен с первым входом, второго блока внутрирегистрового сдвига кодов, первый выход которого связан с входом третьего блока запоминания кодов, а второй выход первого блока внутрирегистрового сдвига кодов связан через дешифратор ответвляемого кода с блоком запоминания ответвляемого кода, при этом второй выход второго блока внутрирегистрового сдвига кодов соединен с вторым входом первого блока внутрирегистрового сдвига кодов. Причем вход первого блока запоминания кодов является первым вхсщом, а третьи входы первого и второго блоков внутрирегистрового сдвига кодов являются соответственно вторыми и третьими входами асинхронно-синхронного регистра первой регистровой ячейки, первым и вторым выходом которой служат ВЫХОДЫ блока запоминания ответвляемого кода и третьего блока запоминания кодов.

3.Устройство по п. 1, о т л и ч а .ю щ е е с я тем, что асинхронносинхронный регистр первой регистровой ячейки выполнен из трех блоков запоминания кодов, двух блоков внутрирегистрового сдвига кодов,, дешифратора ответвляемого к.ода и единичного шифратора, причем выход дешифратора ответвляемого кода через, первый блок запоминания кодов соединен

с первым входом первого блока внутрирегистрового сдвига кодов, выход которого через единичный шифратор связан с первым ВХОДОМ второго блока запоминания колов, первый выход которого связан с первым входом второго блка внутрирегистрового сдвига кодов, выход которого соединен с третьим блоком запоминания кодов, при этом вход дешифратора ответвляемого кода соединен с вторым входом второго блока запоминания кодов и они являются первым входом асинхронносийхронного регистра первой регистровой ячейки, а вторые входы первого и второго блоков внутрирегистровых сдвигов кодов служат соответственно вторым и третьим входом асинхронно-синхронного регистра первой регистровой ячейки, первым и вторым выходом которой соответственно яв- . ляются второй выход второго блока запоминания кодов ja выход третьего блока запоминания кодов.

4.Устройство по п. 1, о т л и ча ю щ ее с, я тем, что асинхронносинхронный регистр первой регистровой ячейки выполнен из четырех ftnoкс9в запоминания кодов, двух блоков

внутрирегистрового сдвига кодов и блока запоминания ответвляемого крда, причем первый блок запоминания кодов соединен с первым входом первого блока внутрирегистрового сдвига кодов, первый выход которого через третий блок запоминания кодов связан с первым входом второго блока внутриреги.стрового сдвига кодов, первый выход которого соединен с четвертым блоком запоминания кодов, при этом выход второго блока з апоминания кодов связан с вторым входом первого блока внутрирегистрового сдвига кодов, второй выход которого соединен с блоком запоминания ответвляемого кода, а второй выхоп вторбго блока внутрирегистрового сдвига кодов соединен с третьим входом первого блока внутрирегистрового сдвига кодов, причём входы первого и второго блоков запоминания кодов объединены между собой и являются первым входом асинхронно-синхронного регистра первой регистровой ячейки, а вторым и третьим входом .служат четвертый вход первого и второй вход второго блоков внутрирегистрэвых сдвигов кодов, при этом выход блока запоминания ответвляемого кода служит первым выходом, а выход четвертого блока запоминания кодов Является вторым выходом асинхронно-синхронного регистра первой регистровой ячейки.

5. Устройство по п. I, о т л и чающееся тем, что асинхронносинхронный регистр первой регистровой ячейки выполнен из трех блоков запоминания кодов, двух блоков внутрирегистрового сдвига кодов и блока запоминания ответвляемого кеда, причем первый блок запоминания кодов соединен с первым входом первого блрка внутрирегистрового сдвига кодов, выход которого соединен с вторым блоком запоминания кодов, а третий блок запоминания кодов связан с первым входом второго блока внутрирегистрового сдвига ксщов, выход которого соединен с блоком запоминания ответвляемого кода,-при этом входы первого и третьего блоков запсялинания кодов соединены между собой и являются першдм входом асинхронно-синхронного регистра первой регистровой ячейки, а вторым и третьим входом служат вторые входы первого и второго блоков внутрирегистровых сдвигов кодов, при этом выход блока запоминания ответвляеftoro кода служит первым выхоцом, а выход второго блока запоминания кодов является BTopbiM выходом асинхрокнЪ-синхронного pisracrpa первой регисровой ячейки. Изобретение относится к устройствам программного управления и может быть использовано при .сортировке лесоматериалов. Известно устройство управления сортировкой лесоматериаловf содержащее задатчик адресов, соединенный через шифратор с начальным асинхронным регистром, дешифраторы, регистровые .и безрегистровые ячейки по чис лу накопителей, включающие путевой датчик и исполнительный механизм l Недостатком известного устройств является низкое качество сортировки Цель изо етения - повышение качества сортировки. Поставленная цель достигается тем что устройство, содержащее задатчик адресов, соединенный через шифратор с начальным асинхронным регистром, дечифраторы, регистровые и безрегист ровые ячейки по числу накопителей, включающие путевой датчик и исполнительный механизм, содержит блоки сдвигу кодов, блок сдвига кодов с. дешифраторами -и асинхронно-синдсронные регистры, при этом регистровые ячейки., кроме последней, объединены попарно с безрегистровыми ячейками, причем первая регистровая ячейка этой пары, расположенная ближе к начальному асинхронному регистру, вклю чает блок сдвига кодов и асинхронносинхронный регистр, а ее вторая безрегистровая ячейка включает блок сдвига кодов с дешифратором, при это путевой датчик первых регистровых ячеек каждой пары первым выходом свя зан с Первым входом блока сдвига кодов, первый выход которого соединен через дешифратор со своим исполнительным механизмом/ а второй выход связан с первым входом асинхронносинхронного регистра, первый выход которого соединен с первым входом блока сдвига кодов с дешифратором второй безрегистровой ячейки, а первый выход блока сдвига кодо.в с дешиф ратором связан со своим испопнительным механизмом, при этом путевой датчик второй безрегистровой ячейки первым выходом соединен с вторым входом блока сдвига кодов с дешифратором, второй выход которого- соединен с вторым выходом путевого датчика второй безрегистровой ячейки и с вторым входом асинхронно-синхронного регистра первой регистровой ячейки, при этом у путевых датчиков первых регистровых ячеек каждой пары, кроме первой регистровой ячейки первого накопителя, второй выход сое динен с третьим входом асинхронносинхронного регистра первой, регистровой ячейки предыдущего накопителя а второй выход асинхронно-синхронно. го регистра связан с вторым входом блока сдвига кодов первой регистровой ячейки следующего накопителя, третий выхсщ блока сдвига кодов первой регистровой ячейки соединен с третьим входом асинхронно-синхронного регистра первой регистровой ячейки предьщущего накопителя, при этом асинхронно-синхронный регистр наиболее удаленной от начсшьного асинхронного регистра первой регистровой ячейки вторым выходом соединен с вторым входом блока сдвига кодов с дешифратором второй безрегистровой ячейки, а второй выход блока сдвига кодов соединен с третьим входом асинхронно-синхронного регистра первой регистровой ячейки. При этом асинхронно-синхронный регистр первой регистровой ячейки выполнен из трех блоков запоминания кодов, двух блоков, внутрирегистрового сдвига кодов, дешифратора ответвляемого кода и блока запоминания ответвляемого кода, .причем выход первого блока запоминания кодо.в связан с первым входом первого .блока внутрирегистрового сдвига кодов, первый выход которого через второй блок запоминания кодов соединен с первым входом второго блока внутрирегистрового сдвига кодов, первый выход которого связан с входом третьего блока запоминания кодов, а второй выход первого блока внутрирегистрового сдвига кодов связан через дешифратор ответвляемого кода с блоком запоминания ответвляемого кода, при этом второй выход второго блока внутрирегистрового сдвига кодов соединен с вторым входом первого блока внутрирегистрового сдвига кодов, причем вход первого блока запоминания кодов является первым входом, а третьи входы первого и второго блоков внутрирегистрового сдвига кодов являются соответственно вторыьш и третьими входами асинхронносинхронного регистра -первой регистровой ячейки, первым и вторым выходом которой служат выходы блока запоминания ответвляемого кода и третьего блока запоминания кодов. Асинхронно-синхронный регистр первой регистровой ячейки может быть выполнен из трех блоков запоминания кодов, двух блоков внутрирегистрового сдвига кодов, дешифратора ответвляемого кода и единичного шифратора, причем выход дешифратора ответвляемого кода через первый блок запоминания кодов соединен с первым -входом первого блока внутрирегистрово то сдвига кодов, выход которого через единичный шифратор связан С первым входом второго блока запоминания кодов, первый выход которого свя эан с первым входом второго блока внутрирегистроаого сдвига кодов, выход которого соедине.н с третьим блоком запоминания кодов, при этом вход дешифратора ответвляемого кода соединен с вторым входом второго блока запоминания код:ов и они };:вляются первым входом асинхронно-сингфонного регистра первоЛ регистровой ячейкиf а вторые входы первого и вгорого блоков внутрирегистровых сдвигов кодов служат соответственно вторым и третьим входом асинхронносинхронного регистра первой регистровой ячейки, первым и вторым выходом которой соответственно являются второй выход второго блока запоминания кодов и выход третьего блока запоминания кодов.

Асинхронно-синхронный регистр первой регистровой ячейки может быть выполнен из четырех блоков запоминания КОД.ОВ, двух блоков внутрирегистрового сдвига кодов и блока запоминания ответвляемого кода, причем первый блок запоминания кодов соедивен с первым входом первого блока внутрирегистрового сдвига кодов, первый выход которого через третий блок запоминания кодов связан с первым входом второго блока внутрирегистрового сдвига кедов, первый выход которого соединен с четвертым блоком запоминания -кодов, при этом выход второго блока запоминания кодов связан с вторым входом- первого блока внутрирегистрового сдвига кодов, второй выход которого соединен с блоком запоминания ответвляемого Кода, а второй выход второго блока внутрирегистрового сдвига кодов .соединен с третьим входом первого блока внутрирегистрового сдвига кодов, причем входы первого и второго блоков запоминания кодов объединены между собой и являются первым вхсдом асинхронно-синхронного регистра первой регистровой ячейки, а вторым и третьим входом служат четвертый вход первого и второй вход второго блоков внутрирегистровых сдвигов кодов, при этом выход блока запоминания ответвляемого кода служит первым выходом, а выход четвертого блока запоминания кодов является вторым выходом асинхронно-синхронного регистра первой регистровой ячейки.

Кроме того, асинхронно-синхронный регистр первой регистровой ячейки выпопнен из трех блоков запоминания ft оДов, двух блок ов внутрире гистрового сдвига кодов и блока запоминания ответвляемого- кода, причем первый 6jft)K запокинаниЯ кодов соединен с .первым входом первого блока внутрирегистрового сдвига кодов, выход

которого соединен с вторым блоком запоминания кодов, а третий блок запоминания кодов связан с первым входом iBTOporo блока внутрирегистрового .сдвига кодов, выход которого соедиS иен с блокс«4 эапсмшнания ответвляемого кода, этом входы первого и треть:вго блоков запоминания кодов соединены между собой и йвляются первым входом асинхронно-синхронного

10 регистра первой регистровой ячейки, а вторым и третьим входом служат вторые входы первого и второго блоков внутрирегистровых сдвигов кодов, при этом, выход блока запоминания

5 ответвляемого кода служит первым выходом, а выход второго блока запоминания кодов, является вторым выходом асинхронно-синхронного регистра первой регистровой ячейки.

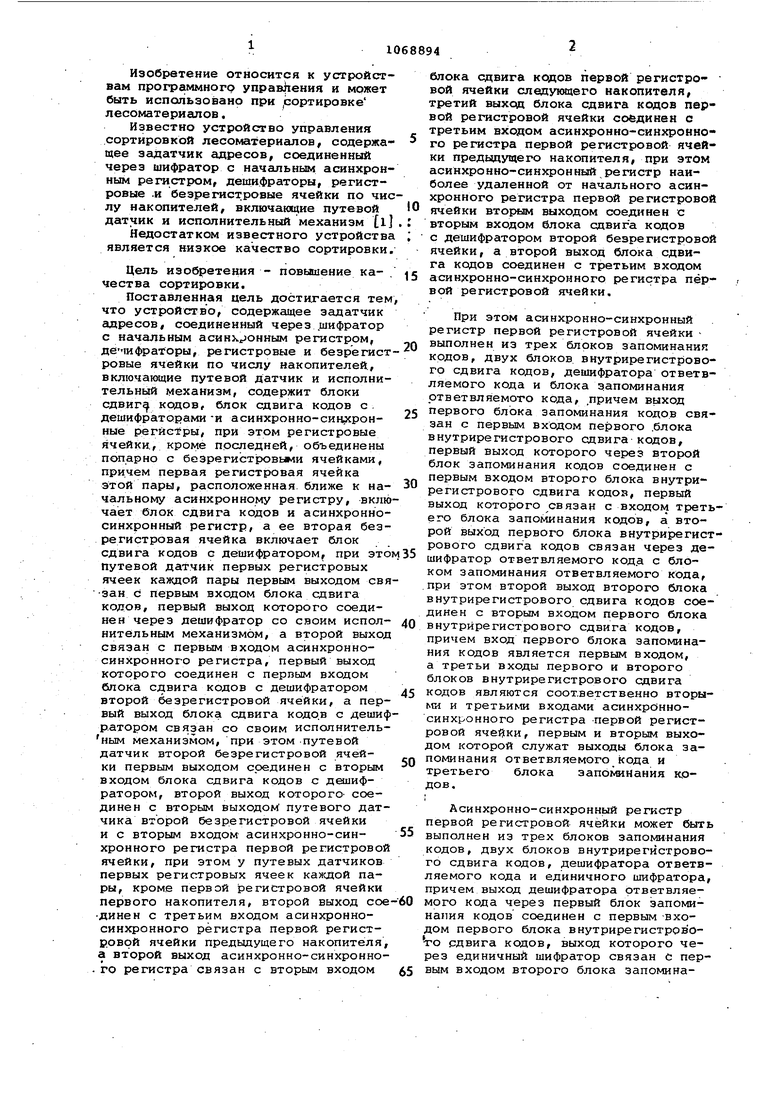

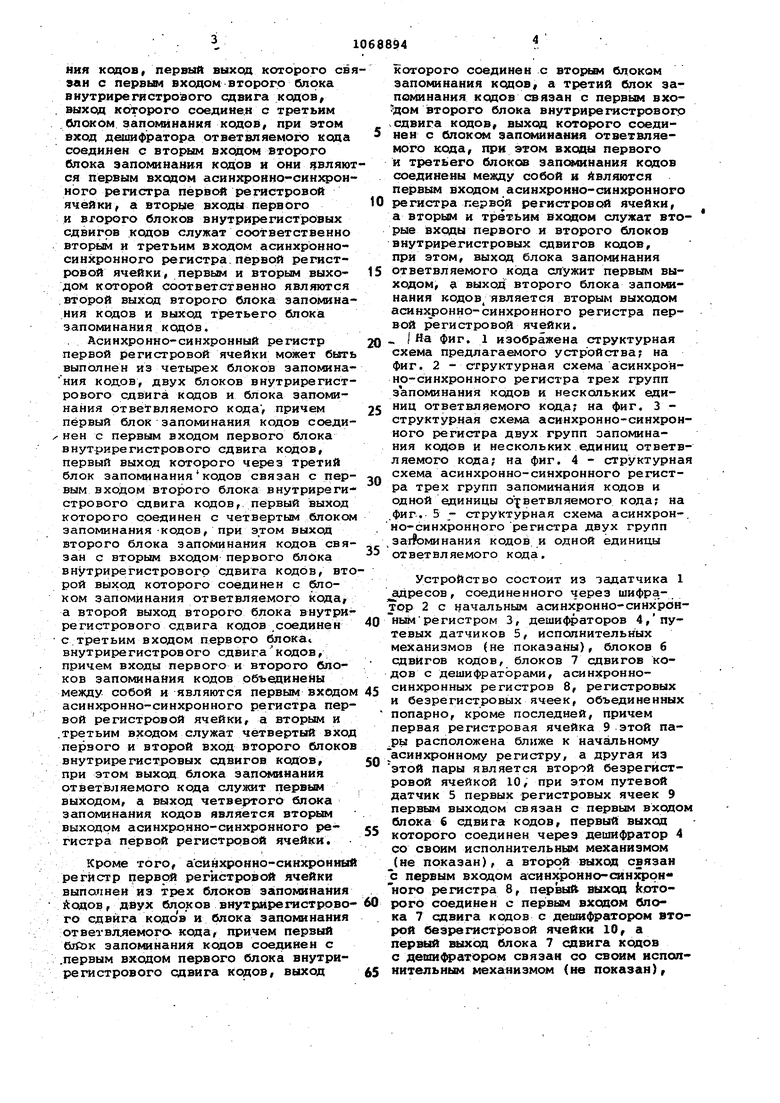

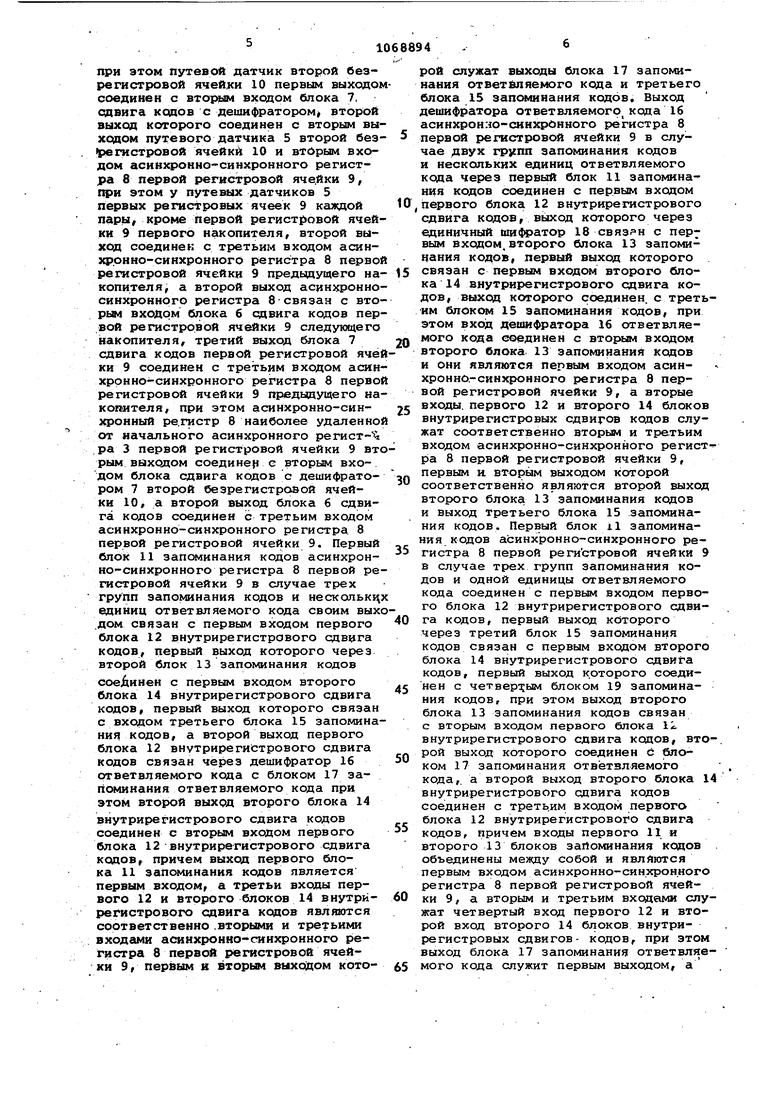

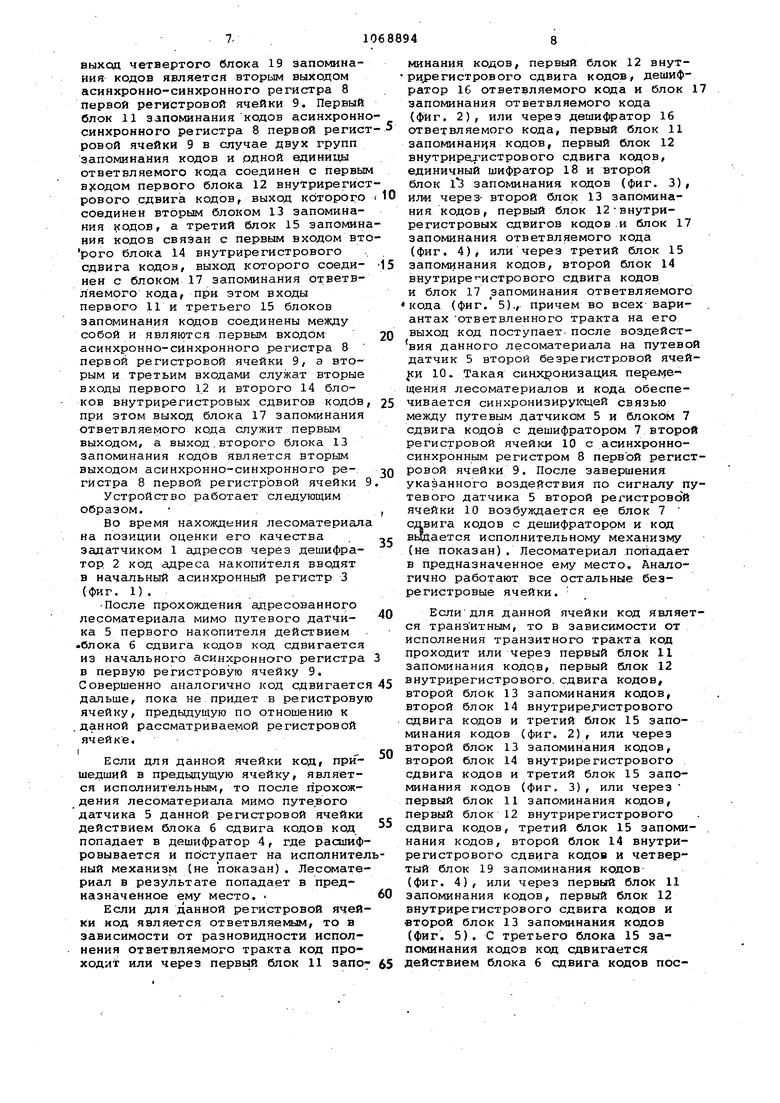

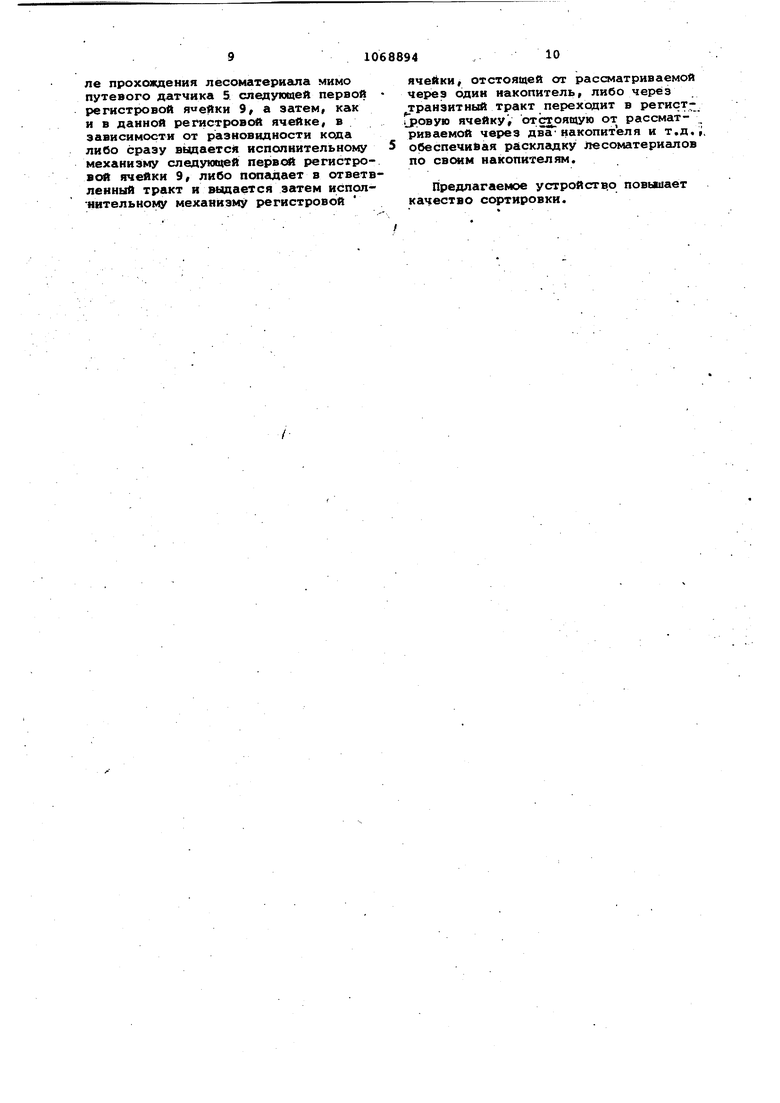

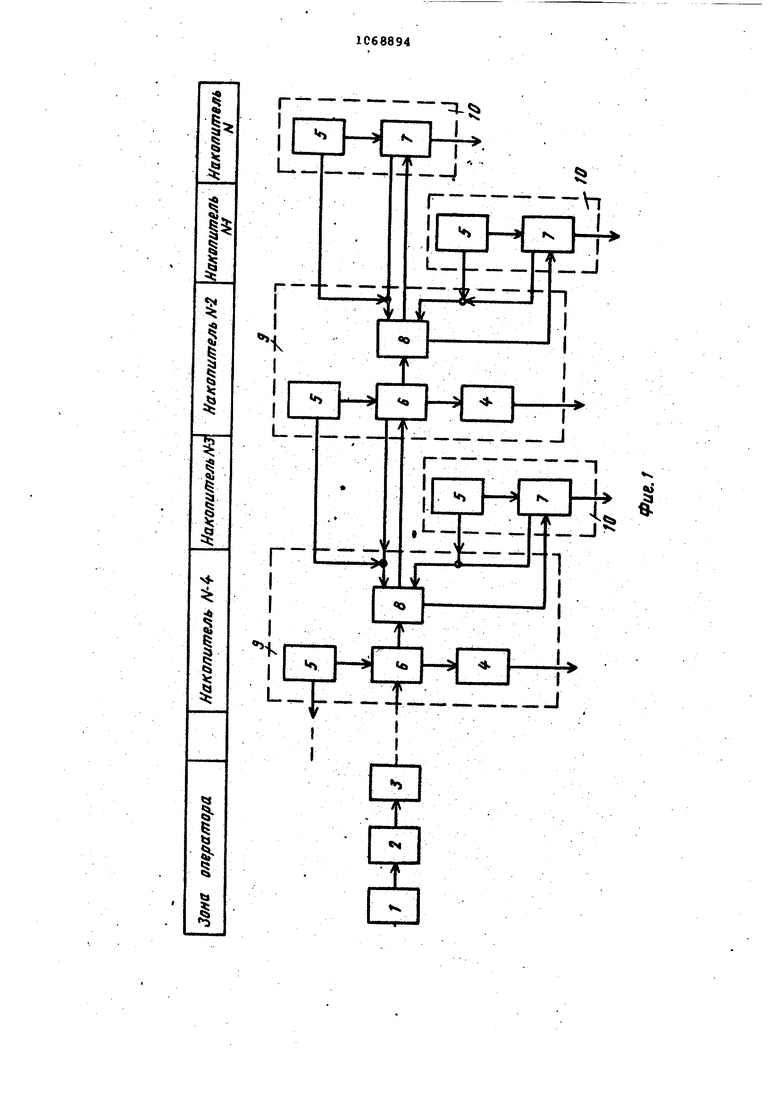

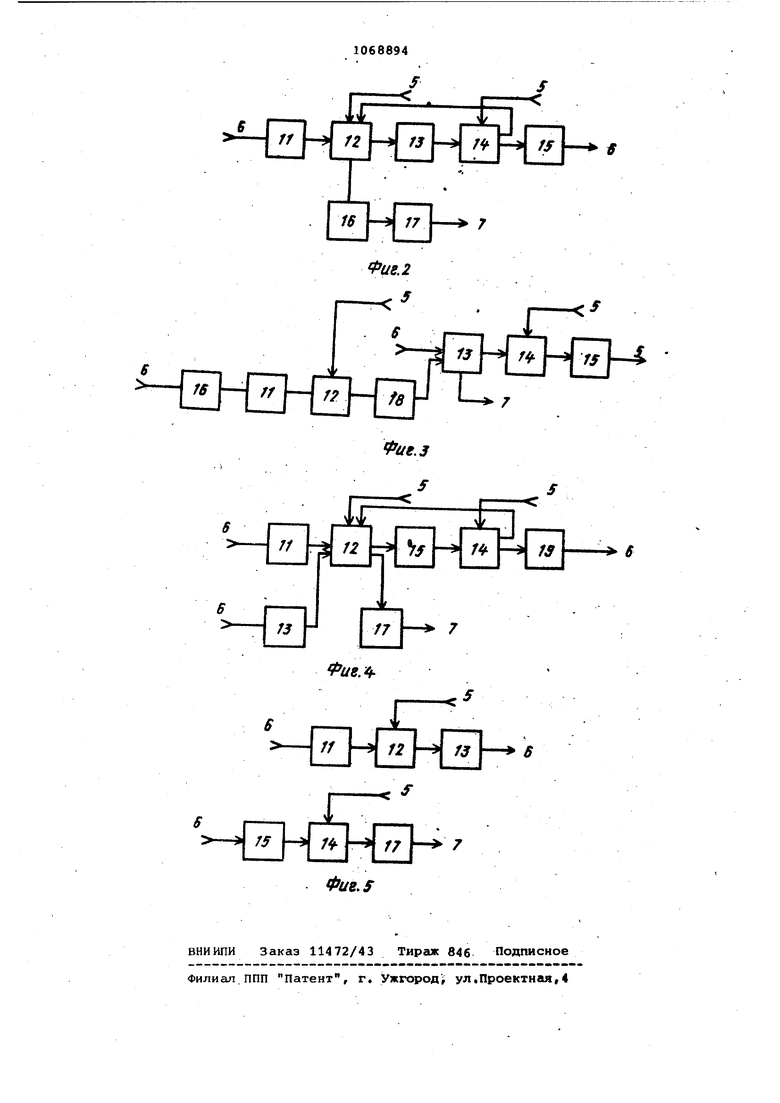

Q « I На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема асинхронно-синхронного регистра трех групп запоминания кедов и несксльких еди5 ниц ответвляемого кода; на фиг. 3 структурная схема асинхронно-синхронного регистра двух групп запоминания кодов и нескольких единиц ответвляемого кода; на фиг. 4 - стру ктурная схема асинхронно-синхронного регистра трех групп запоминания кодов и одной единицы о ветвляемого кода; на .фиг. 5 - структурная схема асинхрон-, но-синхронногорегистра двух групп запоминания кодов и одной единицы

5 ответвляемого кода.

Устройство состоит из эадатчика 1 jCapecoB, соединенного через шифратор 2 с начальным асинхронно-синхрон0 нь1мрегистром 3, дешифраторов 4,путевых датчиков 5, исполнительных механизмов (не показаны), блоков 6 сдвигов кодов, блоков 7 сдвигов кодов с дешифраторами, асинхронно5 синхронных регистров 8, регистровых

и безрегистровых ячеек, объединенных попарно, кроме последней, причем первая регистровая ячейка 9 этой пары расположена ближе к начальному

асинхронному регистру, а другая из этой пары является второй безрегистровой ячейкой 10, при этом путевой датчик 5 первых регистровых ячеек 9 первым выходом связан с первым входом блока 6 сдвига кодов, первый выход

5 которого соединен через дешифратор 4

со своим исполнительным механизмом

(не показан), а второй выход связан

Ъ первым входом асинхронно-синзфон ного регистра 8, первый выход fcoTO0 рого соединен с первым входом блока 7 рдвига кодов с дешифратором второй безрегистровой ячейки 10, а первый выход блока 7 сдвига кодов с дешифратором связан со своим испол5 нительным механизмом (не показан).

при этом путевой датчик второй безрегистровой ячей{ и 10 первым выходомсоединен с зторым входом блока 7, сдвига кодов с дешифратором второй выход которого соединен с вторым выходом путевого датчика 5 второй без(решстровой ячейки 10 и вторым входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9, 1Ч)и этом у путешлх датчиков 5 п:ервых регистровых ячеек 9 каждой пары, кроме первой регист{ овой ячейки 9 первого накопителя, второй выход соединен с третьим входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9 предьиущего накопителя, а второй выход асинхронносинхронного регистра 8-связан с вторым входом блока 6 сдвига кодов первой регистровой ячейки 9 следующего накопителя, третий выход блока 7 сдвига кодов первой регистровой ячейки 9 соединен с третьим входом асинхронно-синхронного peipHCTpa 8 первой регистровой ячейки 9 предыдущего накопителя, при этом асинхронно-синхронный регистр 8 наиболее удаленной от начального асинхронного регист- ра 3 первой регистровой ячейки 9 вторым выходом соединен с вторым входом блока сдвига кодов с дешифратором 7 второй безрегистровой ячейки 10, а второй выход блока 6 сдвига кодов соединен с третьим входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9. Первый блок 11 запоминания кодов асинхронно-синхронного регистра 8 первой регистровой ячейки 9 в случае трех групп запоминания кодов и нескольких единиц ответвляемого кода своим выхо.дом связан с первым входом первого блока 12 внутрирегистрового сдвига кодов, первый выход которого через второй блок 13 запоминания кодов

соединен с первым входом второго блока 14 внутрирегистрового сдвига кодов, первый выход которого связан с входом третьего блока 15 запоминания кодов, а второй выход первого блока 12 внутрирегистрового сдвига кодов связан через дешифратор 16 ответвляемого кода с блоком 17 запоминания ответвляемого кода при этом второй выход второго блока 14 внутрирегистрового сдвига кодов соединен с вторым входом первого блока 12 внутрирегистрового сдвига кодов, причем выход первого блока 11 запоминания кодов является первым входом, а третьи входы первого 12 и второго блоков 14 внутрирегистрового сдвига кодов являются соответственно .вторыми и третьими входами асинхронно-синхронного регистра 8 первой регистровой ячейки 9, первым и вторым выходом которой служат выходы блока 17 запоминания ответвляемого кода и третьего блока 15 запоминания кодов. Выход дешифратора ответвляемого, кода 16 асинхрон:ю-син:фОнного регистра 8 первой регистровой ячейки 9 в случае двух групп запоминания кодов и нескольких единиц ответвляемого кода через первый блок 11 запоминания кодов соединен с первым входом

первого блока 12 внутрирегистрового сдвига кодов, выход которого через единичный ши(атор 18 связан с пер7 вым входом, второго блока 13 запоминания кодов, первый выход которого

связан с первым входом второго блока 14 внутрирегистрового сдвига кодов, выход которого соединен, с третьим блоком 15 запоминания кодов, при этом вход дешифратора 16 ответвляемого кода соединен с вторым входом

второго блока 13 запоминания кодов и они являются первым входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9, а вторые

входал. первого 12 и второго 14 блоков внутрирегистровых сдвигов кодов служат соответственно вторьм и третьим

входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9, первым и вторым выходом которой соответственно являются второй выход второго блока 13 запоминания кодов и выход третьего блока 15 запоминания кодов. Первый блок il запоминания кодов асинхронно-синхронного регистра 8 первой регистровой ячейки 9 в случае трех групп запоминания кодов и одной единицы ответвляемого кода соединен с первым входом первого блока 12 внутрирегистрового сдвига кодов, первый выход которого через третий блок 15 запоминания кодов связан с первым входом второго блока 14 внутрирегистрового сдвиГа кодов, первый выход крторого соединен с четвер1;ым блоком 19 запоминания кодов, при этом выход второго блока 13 запоминания кодов связан с вторым входом первого блока 11 внутрирегистрового сдвига кодов, вто-.

рой выход которого соединен с блоком 17 запоминания отв(атвляемого кода,, а второй выход второго блока 14 внутрирегистрового сдвига кодов соединен с треть.им входом первого блока 12 внутрирегистрового сдвига

кодов, причем входы первого 11 и второго 13 блоков запоминания кодов объединены между собой и являются первым входом асинхронно-синхронного регистра 8 первой регистровой ячейки 9, а вторым и третьим входами служат четвертый вход первого 12 и второй вход второго 14 блоков внутрирегистровых сдвигов- кодов, при этом выход блока 17 запоминания ответвляемого кода служит первым выходом, а

выход четвертого блока 19 запоминания кодов является вторым выходом асинхронно-синхронного регистра 8 первой регистровой ячейки 9. Первый блок 11 запоминаниякодов асинхронносинхронного регистра 8 первой регист-5 ровой ячейки 9 в случае двух групп запоминания кодов и одной единицы ответвляемого кода соединен с первым в}содом первого блока 12 внутрирегистрового сдвига кодов, выход которого 1 10 соединен вторым блоком 13 запоминания кодов, а третий блок 15 запоминания кодов связан с первым входом второго блока 14 внутрирегистрового , . сдвига кодов, выход которого соеди- 15 нен с блоком 17 запоминания ответвляемого кода, при этом входы первого 11 и третьего 15 блоков запоминания кодов соединены между собой и являются первым входом 20 асинхронно-синхронного регистра В первой регистровой ячейки 9, э вторым и третьим входами служат вторые входы первого 1.2 и второго 14 блоков внутрирегистровых сдвигов кодОв, 25 при этом выход блока 17 запоминания ответвляемого кода служит:первым выходом, а выход.второго блока 13 запоминания кодов является вторым выходом асинхронно-синхронного ре- 0 гйстра В первой регистровой ячейки 9.

Устройство работает следующим образом, ,

Во время нахождения лесоматериала на позиции оценки его качества . ,Е задатчиком 1 адресов через дешифратор. 2 код адреса накопителя вводят в начальный асинхронный регистр 3 (фиг. 1).

После прохождения адресованного лесоматериала мимо путевого датчи- 0 ка 5 первого накопителя действием блока 6 сдвига кодов код сдвигается из начального асинхронного регистра 3 в первую регистровую ячейку 9, овершенно аналогично код сдвигается 45 дальше, пока не придет в регистровую ячейку, предыдущую по отношению к данной рассматриваемой регистровой ячейке,

-50

Если для данной ячейки код, приедший в предыдущую ячейку, является исполнительным, то после прохожения лесоматериала мимо путевого атчика 5 данной регистровой ячейки ействием блока б сдвига кодов код попадает в дешифратор 4, где расшифовывается и поступает на исполнительный механизм (не показан). Лессматеиал в результате попадает в предназначенное ему место. 60

Если для данной регистровой ячейки код является ответвляемым, то в зависимости от разновидности исполнения ответвляемого тракта код проходит или через первый блок 11 запо- 65

минания кодов, первый блок 12 внут рире гистров ого сдви га к одов, дешифратор 16 ответвляемого кода и блок запоминания ответвляемого кода (фиг, 2), или через деши йатор 16 ответвляемого кода, первый блок 11 запоминания кодов, первый блок 12 внутриред:истрового сдвига кодов, единичный шифратор 18 и второй блок запоминания кодов (фиг. 3) , ил« череЗ второй блок 13 запоминания кодов, первый блок 12-внутрирегистровых сдвигов кодов .и блок 17 запоминания ответвляемого кода (фиг. 4), или через третий блок 15 запоминания кодов, второй блок 14 внутрирегистрового сдвига кодов и блок 17 запоминания ответвляемого «кода (фиг. 5),, причем во всех вариантах ответвленного тракта на его выход код поступает, после воздействия данного лесоматериала на путево датчик 5 второй безрегистровой ячей| и 10.. Такая синх онизация nepeweщения лесоматериалов и кода обеспечивается синхронизиру1С1цей связью между путевым датчиком 5 и блоком 7 сдвига кодов с дешифратором 7 второ регистровой ячейки 10 с асинхронносинхронным регистром В первой регисровой ячейки 9. После завершения указанного воздействия по сигналу птевого датчика 5 второй регистровой ячейки 10 возбуждается е.е блок 7 сдвига кодов с дешифратором и код ввдается исполнительному механизму (не показан) , Лесоматериал .попадает в предназначенное ему место. Аналогично работают все остальные беэрегистровые ячейки.

Если для данной ячейки код являеся транзитным, то в зависимости от исполнения транзитного тракта код проходит или через первый блок 11 запоминания кодов, первый блок 12 внутрирегистрового. сдвига кодов, второй блок 13 запоминания кодов, второй блок 14 внутрирегистрового сдвига кодов и третий блок 15 запоминания кодов (фиг. 2), или через второй блок 13 запоминания кодов, второй блок 14 внутрирегистрового сдвига кодов и третий блок 15 запоминания кодов (фиг, 3), или через первый блок 11 запоминания кодов, первый блок 12 внутрирегистрового сдвига кодов, третий блок 15 запоминания кодов, второй блок 14 внутрирегистрового сдвига кодов и четвертый блок 19 запоминания кодов(фиг. 4), или через первый блок 11 запоминания кодов, первый блок 12 внутрирегистрового сдвига кодов и второй блок 13 запоминания кодов (фиг. 5). С третьего блока 15 запоминания кодов код сдвигается действием блока 6 сдвига кодов после прохождения лесоматериала мимо путевого датчика 5. следующей первой регистровой ячейки 9, а затем, как и в дайной регистровой ячейке, в зависимости от разновидности кода либо сразу выдается исполнительному механизму следующей перъоЛ регистровой ячейки 9, либо п Х1адает в ответвленный тракт и выдается затем исполнительному механизму регистровой

ячейки, отстоящей от рассматриваемой через один накопитель, либо через транзитный тракт переходит в регист-РРвую ячейку, отстоящую от рассматриваемой через двгГ накопителя и т.д./ 5 обеспечивая раскладку лесоматериалов по своим накопителям.

Предлагаемое устройство повьшает качество сортировки.

м

//

S

t

/f

13

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления сортировкой лесоматериалов | 1984 |

|

SU1247841A2 |

| Устройство управления сортировкой длинномерных материалов | 1990 |

|

SU1817060A1 |

| Устройство управления сортировкой длинномерных материалов | 1985 |

|

SU1305638A1 |

| Устройство управления сортировкой длинномерных материалов | 1991 |

|

SU1824628A1 |

| Устройство управления сортировкой лесоматериалов | 1991 |

|

SU1824626A1 |

| Устройство управления сортировкой лесоматериалов | 1991 |

|

SU1824627A1 |

| Устройство управления сортировкой лесоматериалов | 1990 |

|

SU1729618A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Устройство для управления сортировкой длинномерных материалов | 1990 |

|

SU1782680A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

1. УСТРОЙСТВО УПРАВЛЕНИЯ СОРТИРОВКОЙ ЛЕСОМАТЕРИАЛОВ, содержащее задатчик адресов, соединенный, через шифратор с начальным асинхронным регистром, дешифраторы-, регистровые и беэрегистровые ячейки по числу накопителей, включающие путевой датчик и исполнительный механизм, от л и ч а юще ее я тем, что, с целью повьаиения качества сортировки, оно содержит блоки сдвига кодов, блок сдвига кодов с дешифраторами и асинхронно-синхронные регистры, при этом реги гровые ячейки, кроме последней, объединены попарно с безрегистровьми ячейками, причем первая регистровая ячейка этой пары, расположенная ближе к начальному асинхронному регистру, включает блок сдвига кодов и асинхронно-синхрон-: ный регистр, а ее вторая без гистровая ячейка включает блок сдвига кодов с дешифратором, при этом путевой датчик первых регистровых ячеек каждой пары первым выходом связан с первым входом блока сдвига кацов, первый выход которого соединен через дешифратор со своим исполнительным механизмом, а второй выход связан с первым входом асинхрокно-яинхронного регистра, первый выход котдарого соединен с первым вхсохом блока сдвига кодов с дешифратором второй безрегистровой ячейки а первый fet. ta ,. выход блока сдвига кодов с дешифратором связан со своим испслнительньм механизмом, при этом путевой датчик второй безрегистровой ячейки первым выходом соединен с вторым ВХОДОМблока ццвига кодов с дешифратором, второй выход которого соединен с вторым выходом путевого датчика второй безрегистровой ячейки и вторым входом асинхронно-синхронного регистра первой регистровой ячейки, при этом у путевых датчиков первых регистровых ячеек кахщой пары, кроме первой регистровой ячейки первого накопителя, второй выход соединен с третьим входом асинхронно-синхронного регистра первой регистровой ячейки предьщущего накопи(Л теля, а второй выход асинхронно-синхронного регистра связан с вторым входом блока сцвИга кодов первой регистровой ячейки следующего накопителя, третий выход блока сдвига кодов первой регистровой ячейки соединен с третьим входом асинхронносинхронного регистра первой регистро-. о б вой ячейки предыдущего накопителя, . при этом асинхронно-синхронный регистр наиболее удаленной от началь00 00 ного асинхронного регистра первой регистроВ;СА ячейки вторым выходом соединен с вторым входом блока сдвисо га кодов с дешифратором второй регистровой ячейки, а второй выход блока сдвига кодов соединен с третьим входом асинхронно-синхронного регистра первс регистровой ячейки, 2. Устройство по п. 1, отличающее с я тем, что.асинхронносинхронный регистр первой регистро- :я вой ячейки выполнен из трех блоков Запоминания кодов, двух блоков внутрирегистрового сдвига кедов, дешифратора ответвляемого кода и блока запоминания ответвляемого кода, причем выход первого блока запоминания ко

17

Рие.2

//

f2

leV

Фие.з S

V/

6

ЛУ

/«

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запольский Б.А.и Серов S.B | |||

| Цифровая вычислительная техника для автоматизации лесозаготовительных предприятий | |||

| М., Лесная промлиленность, 1966, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

Авторы

Даты

1984-01-23—Публикация

1982-07-21—Подача