Изобретение относится к автомати ке и вычислительной технике, в част ности к цифровым вычислительным машинам третьего - четвертого поколе1ний, и предназначено для использова ния в устройствах ввода-вывода, модулях обмена с периферийными устрой ствами и в контрольно-проверочной аппаратуре при анализе достоверност передачи информации с последующей ее корректировкой. Известно устройство поразрядного сравнения кодов с выделением сигналов Больше и Меньше или Равно содержащее логические схемы И, ШШ, НЕ и др и 3 -К триггеры ij . . Недос.татком устройства является низкая достоверность функционирования при сравнении кодов, задержанных во времени между собой с невозможностью синхронизации сравниваемых кодов. При наличии -синхронизации на Л-К триггерах - большим коли чеством ложных срабатываний. Наиболее близким к изобретению по технической сущности ярляется устройство для сравнения двоичных чисел, содержащее блок сравнения, включающий О-К триггеры, элементы ИЛИ,НЕ и блок формирования результатов сравнения на элементе ИЛИ-НЕ, причём информационные входы устройства соединены с первыми входами первого и второго J -К триггеров, первый информационный вход устройства через первый элемент НЕ подклю чен к второму входу 3 второго .3-К триггера, второй информационный вход устройства через второй элемен НЕ соединен с вторым входом Д первого 3 -К триггера, прямой выход ко торого подключен к первому входу ne вого элемента ИЛИ, выход которого соединен с входом установки в нулевое состояние второго 3-К триггера, прямрй выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом установки в нулевое состояние первого Л -К триггера, инверсный выход которого подключен к третьему входу 3 второго J -К триггера, инверсный выход Kotoporo соединен с третьим входом D первого 3 7 Триггера, пря мде выходы первого -и второго 3 К триггеров соединены с первым и вторым выходами устройства и с первым и вторым входами элемента ИЛИ-НБ, выход которого подключен к третьей выходной шине устройства, вход синх ронизации устройства соединен с вхо дами D-К триггеров, вход начальной установки устройства подключен ,к вторым входам элементов ИЛИ зЗ . Однако устройство не обеспечивает непрерывную проверку всех битов кодовой информации, так как при первом же неравенстве схема блокируется и требует, для продолжения работы, обнуления. Кроме того, нарушается достоверность информации при сравнении сдвинутых между собой во времени кодов больше, чем на половину импульса битовой единицы, так как узлом сравнения вырабатываются ложные сигналы неравенства. Устройство неработоспособно при асинхронном приеме сравниваемой расфазированной информации rio отношению к импульсам синхронизации. Целью изобретения является повышение достоверности и надежности за счет обеспечения функционирования при сдвиге кодов во времени друг относительно друга и при асинхроннсял приеме их по отногаению к сигналу синхронизации при анализе достоверности передачи информации. Поставленная цель достигается тем, что в устройстве для сравнения двоичных кодов, содержащем блок сравнения, включагаций элемент НЕ, и блок формирования результатов сравнения,, включающий первый элемент ИЛИ-НЕ, причем информационные BxojttJ блока сравнения соединены с шинами первого и второго сравниваемлх кодов, вйЬД синхронизации блока сравнения подключён к шине синхронизации устройства, выхода блока форлшрования результатов сравнения подключены к выходным шинам Больше и Меньше устройства, входы первого элемента ИЛИ-НЕ соединены соот.вет ственно с первым и вторым входами I блока фop мpoвaния результатов сравjнения, а выход - с его первым выхо |дом, в блок сравнения введены эле:мент ИСРШЮЧАЩЕЕ ИЛИ, двоичный счетчик и дешифратор, а в блок формирования результатов сравнения - второй элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с входами элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого через элемент НЕ подключен к входу установки, в ноль двоичного счетчика, счетный вход которого соединен с входом синхронизации блока сравнения, выхоф двоичного счетчика подключены к соответствующим входам дешифратора, выход которого, являющийся вЁлходом блока сравнения, соединен с шиной Равно устройства, с первым входом блока сравнения и с первыми входами первого и второго элементов ИЛИ-НЕ блока формирования результатов сравнения, вторые входы которых подключены соответственно к второму и третьему входам блока формирования результатов ср авнения и к шинам первого и второго сравниваемых кодов, а выходы - соответственно к первому и второму выходам блока формирования результатов сравнения и к шинам Меньше и больше устрой ст ва.

При этом оптимальный период следования импульсов синхронизации оп ределяется длительностью импульса высокого уровня напряжения и и временем задержки сдвига) сравниваемых кодов Ij по соотношению сц

. ..

2

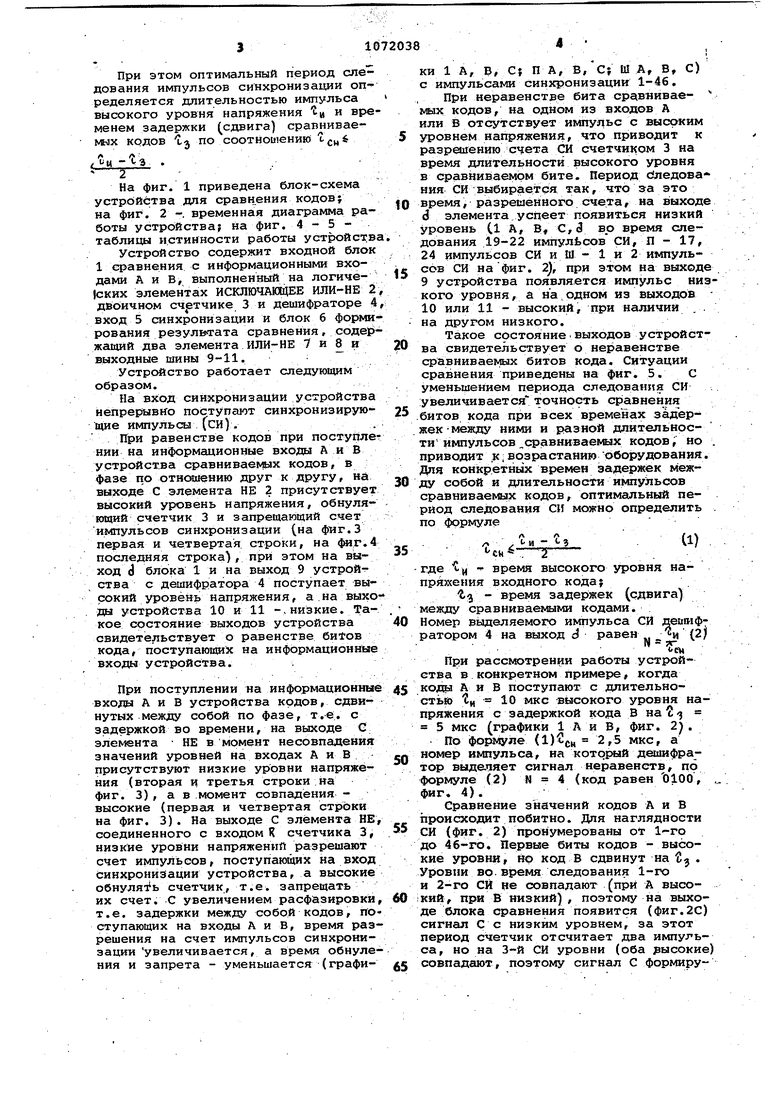

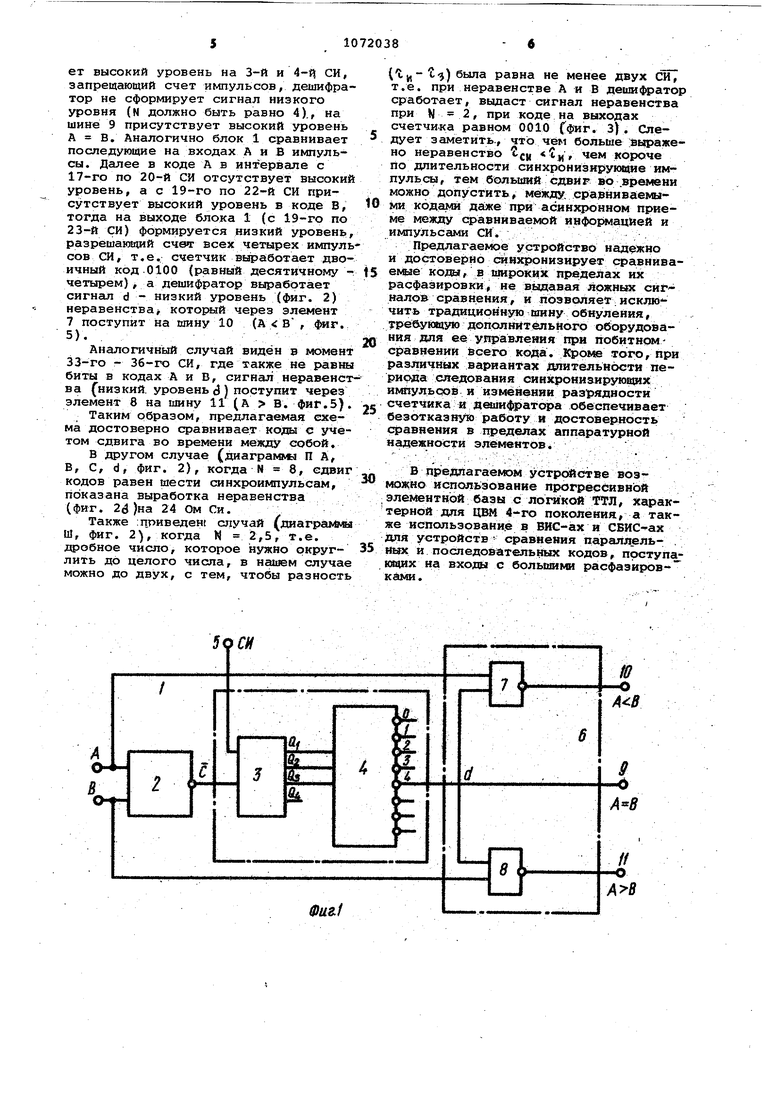

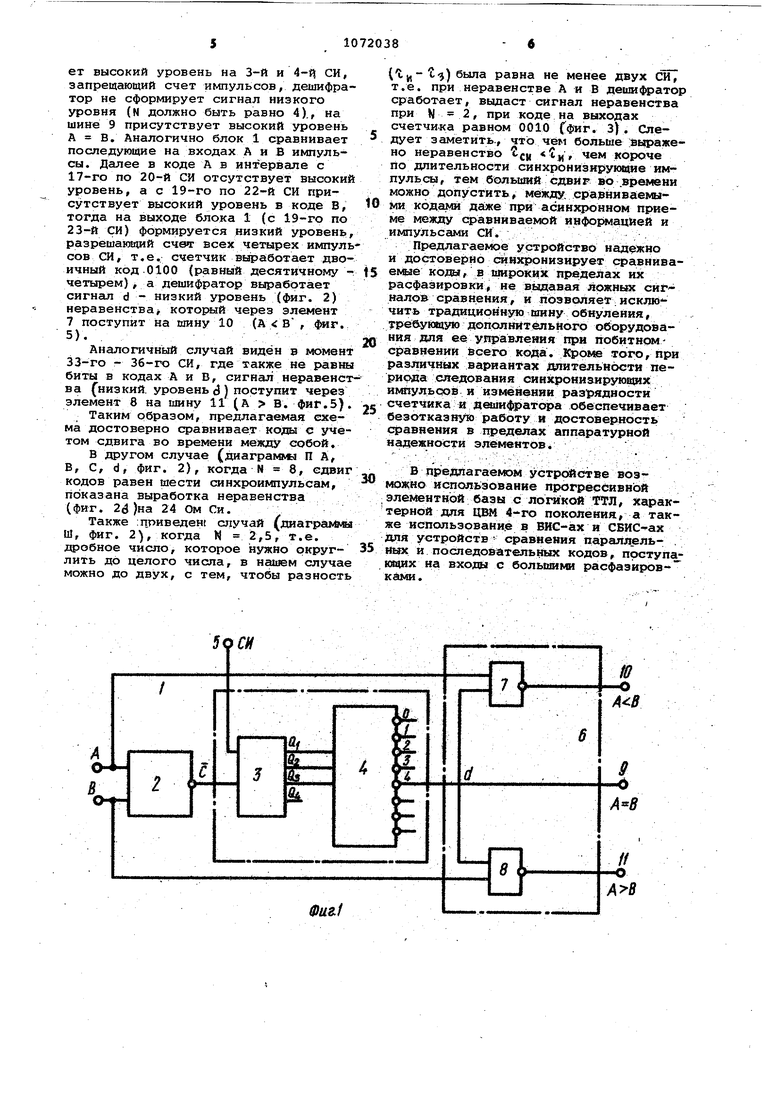

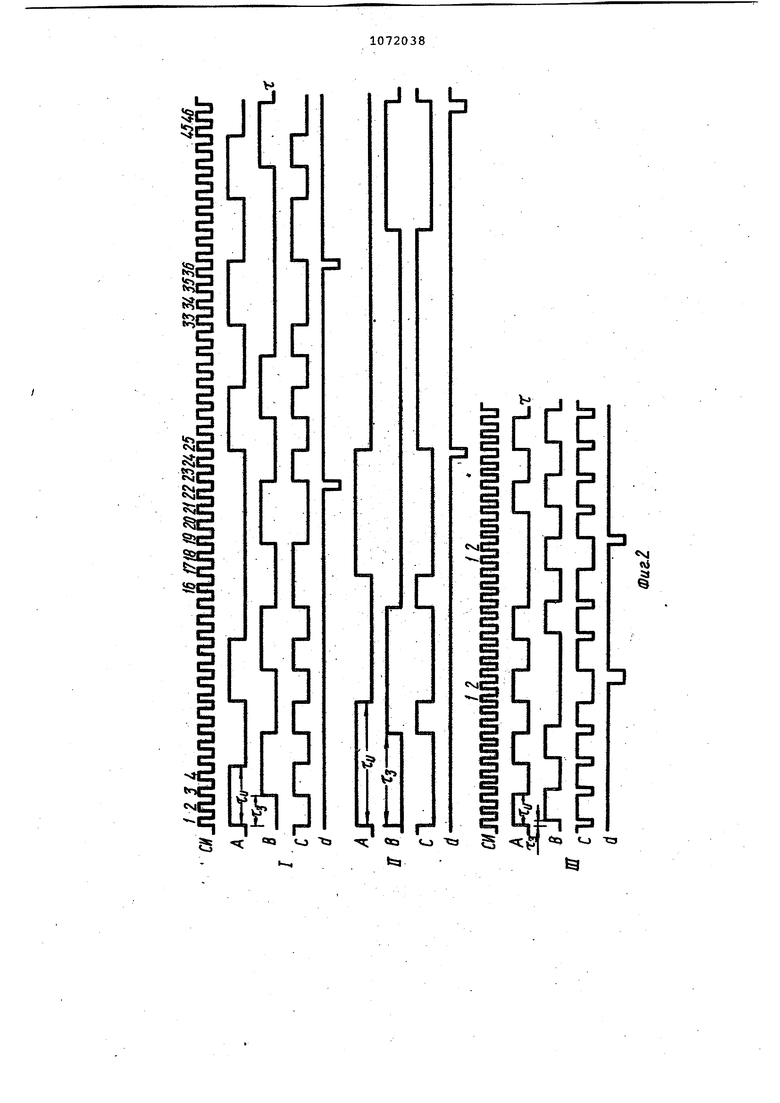

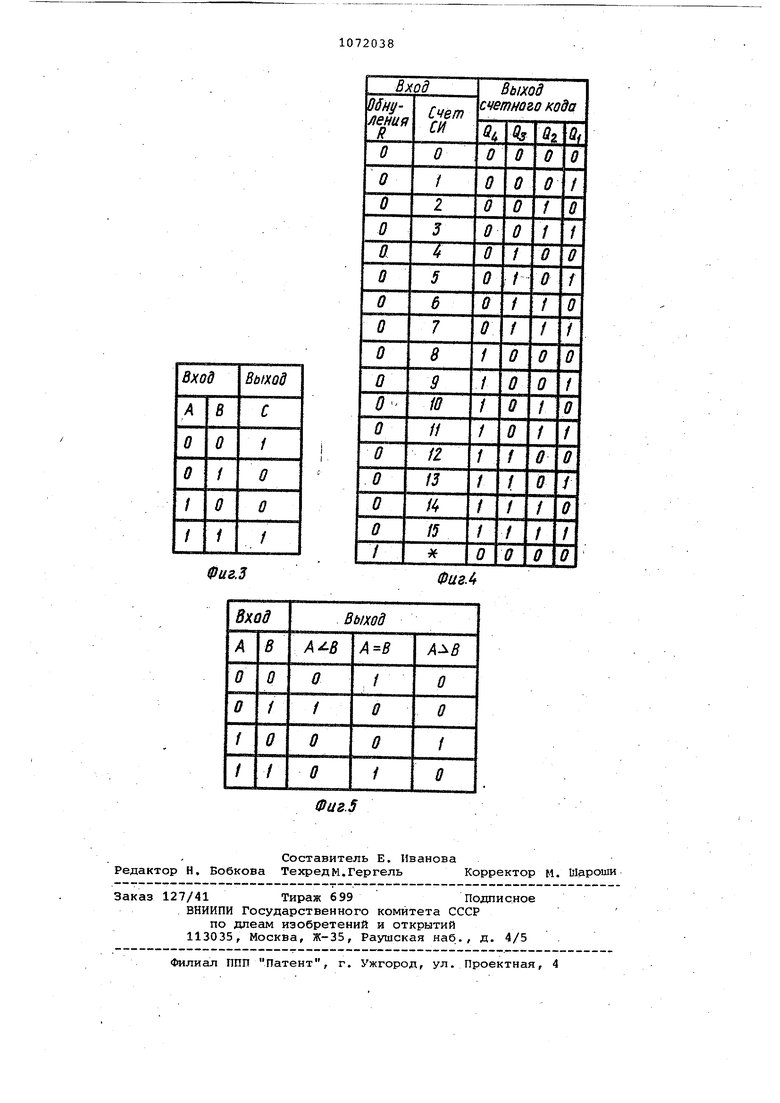

На фиг. 1 приведена блок-схема устройства для сравнения кодовv на фиг. 2 -. временная диаграмма работы устройства; на фиг. 4 - 5 таблицы истинности работы устройств

Устройство содержит входной блок 1 сравнения с информационными входами А и В, выполненный на логичеfcKHX элементах ИСКЛЮЧАЩЕЕ ИЛИ-НЕ 2 двЪичном счртчике 3 и дешифраторе 4 вход 5 синхронизации и блок 6 формирования резулвчгата сравнения, содержащий два элемента ИЛИ-НЕ 7 и 8 и выходные шины 9-11.

Устройство работает следующим образом.

На вход синхронизации устройства непрерывно поступгиот синхронизирующие импульсы (си),.

При равенстве кодов при поступле НИИ на информационные входаз А и В устройства сравниваемых кодов« в фазе по отнснйению друг к другу, на выходе С элемента НЕ 2 присутствует высокий уровень напряжения, обнулягощий счетчик 3 и запрещающий счет импульсов синхронизации (на фиг.З первая и четвертая строки, на г.4 последняя строка), при этом на выход d блока 1 и на выход 9 устрой ства с дешифратора 4 поступает высокий уровень напряжения, а на выходы устройства 10 и 11 -.низкие. Такое состояние выходов устройства свидетельствует о равенстве би1ов кода, поступаюцщх на информационные входщ устройства. .

При поступлении на информационные входы А и В устройства кодов, сдвинутых между собой по фазе, т.е. с задержкой во времени, на выходе G элемента НЕ в момент несовпадения значений уровней на входах А и В присутствуют низкие уровни напряжения (вторая и третья строки.на фиг. 3), а в момент совпадения высокие (первая и четвертая строки на фиг. 3). На выходе С элемента НЕ, соединенного с входом К счетчика 3, низкие уровни напряжений разрешают счет импульсов, поступающих на вход синхронизации устройства, а высокие обнулять счетчик, т.е. запрещать их счет. -С увеличением расфазировкй, т.е. задержки между собой кодов, поступающих на входы А и В, время разрешения на счет импульсов синхронизации увеличивается, а время обнуления и запрета - уменьшается (графики 1 А, В, GJ ПА, В,С; Ш А, Б, С) с импульсами синхронизации 1-46.

При неравенстве бита сравнивавмых кодов, на одном из входов А или в отсутствует импульс с уровнем напряжения, что приводит к разрешению счета СИ счетчиком 3 на время длительности высокого уровня в сравниваемом бите. Период йледова ния СИ выбирается так, что это время, разрешенного счета, на выходе d элемента.успеет появиться низкий уровень (1 А, В, С,5 во время следования 19-22 импулЬсов СИ, Л - 17, 24 импульсов СИ и Ш - 1 и 2 импульсов СИ на фиг. 2), при этом на выходе

9устройства появляется импульс низкого уровня, а на одном из выходов 10или 11 - высокий, при наличии . . на другом низкого.

Такое состояние.выходов устройства свидетельствует о неравенстве сравниваемых битов кода. Ситуации сравнения приведены на фиг. 5. С уменьшением периода следова шя СИ увеличивается точность сравнения .битов кода при всех временах задержек -между ними и р азной длительностиимпульсов сравниваемых кодов, но приводит ,к i возрастанию оборудования. Для конкретных времен задержек между собой и длительности импульсов сравниваемых кодов, оптимальный период следования си можно определить по формуле

л I

(1) t-и - Э

2

чцгде I. и время высокого уровня напряжения входного кода;

з - время задер жек (сдвига) между сравниваемыми кодами. Номер выделяемого импульса СИ дешифратором 4 на выход d равен ц (2)

N 7г ьп

При рассмотрен11и работы устройства в конкретном примере, когда кода А и В поступают с длительностью - iO МКС высокого уровня напряжения с задержкой кода В 5 МКС (графики 1 А и В, фиг. 2J,

По формуле (1)Ссц 2,5 мкс, а номер импульса, на который дешифратор выделяет сигнал неравенств, по формуле (2) N 4 (код равен 0100, фиг. 4).

Сравнение значений кодов А и В происходит побитно. Для наглядности СИ {фиг. 2) пронумерованы от 1-гр до 46-го. Первые биты кодов - высокие уровни, но код В сдвинут на t . Уровни во.время следования 1-го и 2-го СИ не совпадают (при А высо:КиК, при В низкий), поэтому на выходе блока сравнения появится (фиг.2с) сигнал с с низким уровнем, за этот период счетчик отсчитает два импульса, но на 3-й СИ уровни (оба высокие совпадают, поэтому сигнал С формирует высокий уровень на 3-й и 4-4 СИ, запрещающий счет импульсов, дешифратор не сформирует сигнал низкого уровня (N должно быть равно 4)., на шине 9 присутствует высокий уровень А В. Аналогично блок 1 сравнивает последующие на входах А и В импульсы. Далее в коде А в интервале с 17-го по 20-й СИ отсутствует высокий уровень, а с 19-го по 22-й СИ присутствует высокий уровень в коде В, тогда на выходе блока 1 (с 19-го по 23-й СИ) формируется низкий уровень, разрешаювщй счет всех четырех импуль сов СИ, т.е. счетчик вьфаботает двоичный код.0100 (равный десятичному четырем), а дешифратор выработает сигнал d - низкий уровень (г. 2) неравенстваj который через элемент 7 поступит на шину 10 (А В, фиг. 5): ./ , . . ...: ;. Аналогичный случай виден в момент 33-го - 36-го СИ, где также не равны биты в кодах А и В, сигнал неравенст в а низкий, уровень d ) поступит через элемент 8 на шину 11 (А В. фиГ.З). Таким образом, предлагаемая схема достоверно сравнивает коДы с учетом сдвига во времени между собой. В другом случае (диаграмма ПА, В, С, d, фиг. 2), когда N 8, сдвиг кодов равен шести синхроимпульсам, показана выработка неравенства (фит. 2 )на 24 Ом Си. Также :приведен случай (диагра й«д Ш, фиг. 2), когда N 2,5, т.е. дробное число, которое нужно округлить до целого числа, в нашем случае можно до двух, с тем, чтобы разность (tj,-t) была равна не менее двух СИ, т.е. при неравенстве А и В дешифратор сработает, выдаст сигнал неравенства при и 2, при коде на выходах счетчи-ка равном 0010 Сфмг. 3). Следует заметить., что чём больше ;гыражено неравенство tjj, j,, м короче lio длительности синхронизирующие импульсы, тем больший сдвиг во .времени можно допустить, между, сравниваемыми кодами даже при асинхронном приеме между сравниваемой информацией и импульсами СИ. Предлагаемое устройство надежно и достовер|4о синхронизирует сравниваемые кода, в широких пределах их расфазировки, не выдавая ложных сигналов сравнения, и позволяет исключить традициойн5™ шину обнуления, требующую дополнительного оборудования для ее управления при побитнснл сравнении всего кода. Кроме того, при различных вариантах длительности периода следования сиихрониаируюедах импульс5оё и изменении разрядности счетчика и яетаифратора обеспечивает безотказную работу и достоверность сравнения в пределах аппаратурной надежно ;ти элементов. В предлагаемом устройстве возможно использование прогрессивной элемеитной базы с логикой ТТЛ, характерной для ЦВМ поколения, а также использовами.е в ВИС-ах и СВИС-ах для устройств сравнения параллельных и последовательных кодов, прступакяцих на входы с большими расфазиров- ками.

I

S I

-Jhb

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных кодов | 1990 |

|

SU1784965A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| УСТРОЙСТВО СИНХРОННОГО ПРИЕМА ДВОИЧНОЙ ИНФОРМАЦИИ ПО ДУБЛИРУЮЩИМ КАНАЛАМ СВЯЗИ | 2012 |

|

RU2528089C2 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для контроля хода программы | 1983 |

|

SU1236487A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Устройство воспроизведения цифровой магнитной записи | 1990 |

|

SU1777175A1 |

yctPOflCTBO ДЛЯ СРАВНЕНИЯ ДВОИЧНШ КОДОВ, содержащее блок сравнения, включанхций элемент НЕ, и блок/ формирования ре; ультатов фавнения, включаю ф(й первый элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с шингьми первого и второго сравниваемых кодов, взюд синхронизации блока сравнения подключен к 1Ш1не синхронизащш уст- ройства, выходы блока формирования результатов сравнения подключены к выходным ши нам Больше и Меньше устройства, входы первого элемента ИЛИ-НЕ соеда1нены.соответственно с / .первым и вторым входами блока формирования результатов сравнения, а выход - с его первым выходом, отличающееся тем, 1то, с целью повышения надежности устройства за счет обеспечения работоспособности при сравнений расфазированных кодов и их асинхронном приеме по отнсинению к сигналу синхронизации при анализе достоверности передачи информации, в блок сравнения введены элемент ИСК) ИЛИ, двоичный счетчик и дешифратор, а в блок формирования результатов сравнения - . второй элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с входами элемента ИСК7ШЧАЩЕЕ 1ШИ, выход. которого через элемент НЕ подключен к входу установки в ноль двоичного счетчика, счетный вход которого соединен с входом синхронизации блока сравнения, выходы двоичного счетчика подключены к соЬтветствуювим входам дешифратора, § выход которого, являкяцийся выходом блока сравнения, соединен с шиной Равно устройства, .с первым входом блока сравнения, и с первыми входами первогЬ и второго элементов ИЛИ-НЕ блока фор1 гарования результатов срав- g нения, вторые входы которых подключен, ны соответственно к второму и третьему входам блока формирова1}ия результатов сравнения и к чтнам первого и второго сравниваемых кодов, а выходы - соответственно к первому И второму выходам блока формирования результатов сравнения и к шинам Меньше и Больше устройства.

-чс «о ta ocjto -«3 C uQ to -СЭ

Фиг.З

Фиг.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU781807A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU798816A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-07—Публикация

1982-10-15—Подача