Изобретение относится к автоматике и вычислительной технике, может быть использовано в модулях обмена с периферийными устройствами и в контрольно-проверочной аппаратуре при анализе достоверности передачи информации с последующей ее коррекцией.

Известно устройство поразрядного сравнения двоичных чисел, содержащее блок сравнения, включающий IK-тригге- ры, элементы ИЛИ, НЕ и блок формирования результатов сравнения на элементе ИЛИ-НЕ 1.

Недостатком устройства является то, что оно не обеспечивает непрерывную проверку всех битоп кодовой информации, так как при первом же неравенстве схема блокируется и требует для продолжения работы

обнуления, кроме того, нарушается достоверность информации при сравнении сдвинутых между собой во времени кодов больше чем на половину импульса битовой единицы, так как узлом сравнения вырабатываются ложные сигналы неравенства Устройство неработоспособно при асинхронном приеме сравниваемой расфа- зированной информации по отношению к импульсной синхронизации.

Наиболее близким к изобретению по технической сущности является устройство для сравнения двоичных чисел 2, содержащее блок сравнения, включающий элемент НЕ и блок формирования результатов сравнения, включающий первый элемент ИЛИ- НЕ. причем информационные входы блока сравнения соединены с шинами первого и

VJ 00 4 О О СЛ

второго сравниваемых кодов, вход синхронизации блока сравнения подключен к шине синхронизации устройства, выходы блока формирования результатов сравне- ния подключены к выходным шинам Боль- ше и Меньше устройства, входы первого элемента ИЛИ-НЕ соединены соответственно с первым и вторым входами блока формирования результатов сравнения, а - с его первым выходом, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, двоичный счетчик, дешифратор, блок формирования результатов сравнения - второй элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с входами эле- мента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, выход которого подключен ко входу установки в ноль двоичного счетчика, счетный вход ко- торого соединен с входом синхронизации блока сравнения, выходы двоичного счетчи- ка подключены к соответствующим входам дешифратора, выход которого является выходом блока сравнения, соединен с шиной Равно устройства, с первым входом блока сравнения и с первыми входами первого и второго элементов ИЛИ-НЕ блока формирования результатов сравнения, вторые входы которых подключены соответственно ко второму и третьему входам блока формирования результатов сравнения и к шинам первого и второго сравниваемых кодов, а выходы - соответственно к первому и второму выходам блока формирования результатов сравнения и к шинам Меньше и Больше устройства.

Недостатком устройства является то. что оно настроено на одну длительность сравниваемых кодов, а также невозможность перестройки его в процессе работы, что сужает его функциональные возможно- сти.

Целью изобретения является расширение функциональных возможностей за счет автоматической настройки устройства на длительность сравниваемых кодов по сиг- налам с блока сброса.

Поставленная цель достигается тем. что в устройство для сравнения двоичных кодов, содержащее элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый двоичный счетчик, дешифратор, два элемента ИЛИ-НЕ, первые входы которых соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и входами первого и второго сравниваемых чисел устрой- ства, выходы разрядов первого двоичного счетчика соединены с соответствующими входами дешифратора, введены элемент сравнения, элемент задержки,два элемента НЕ, восемь элементов И, два элемента ИЛИ,

второй двоичный счетчик, выходы которого соединены с входами первых групп соответствующих разрядов сумматора и элемента сравнения, входы второй группы которого соединены с соответствующими выходами регистра, входы которого соединены с соответствующими выходами сумматора, входы второй группы которого соединены с входом .логической единицы устройства, вход записи регистра соединен с выходом первого элемента И и входом элемента задержки, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с R-входом второго двоичного счетчика, счетный вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами второго и третьего элементов И, первые входы которых соединены с синхровходом устройства, вторые входы второго, первого и третьего элементов И соединены с первым, вторым и третьим выходами дешифратора соответственно, третий вход второго элемента И, первый вход первого элемента И и счетный вход первого двоичного счетчика соединены с выходом четвертого элемента И, первый вход которого объединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, а второй вход через первый элемент НЕ соединен с третьим входом дешифратора и первыми входами пятого, шестого, седьмого и восьмого элементов И, вторые входы седьмого, шестого и восьмого элементов И соединены соответственно с выходами первого и второго элементов ИЛИ-НЕ и через второй элемент НЕ с выходом элемента сравнения, вторые входы первого и второго элементов ИЛИ-НЕ соединены с выходом второго элемента НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ соединен с вторым входом пятого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с R-входом первого двоичного счетчика и входом сброса устройства, а выходы седьмого, восьмого, шестого элементов И являются выходами устройства.

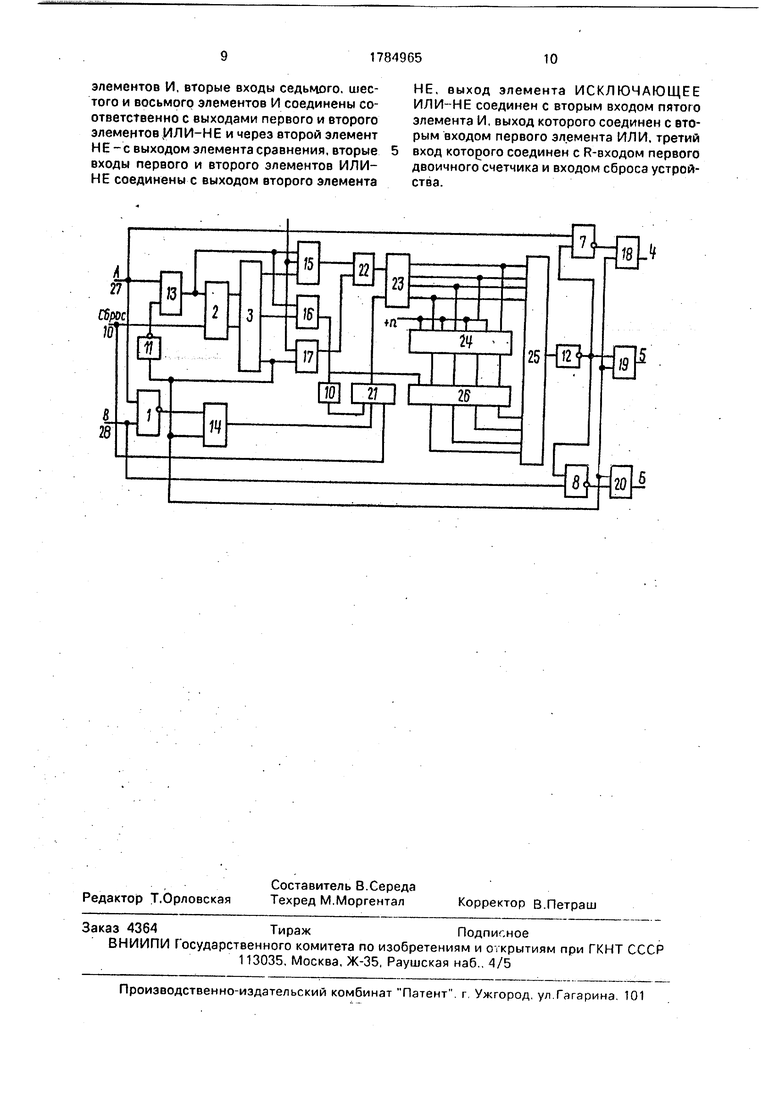

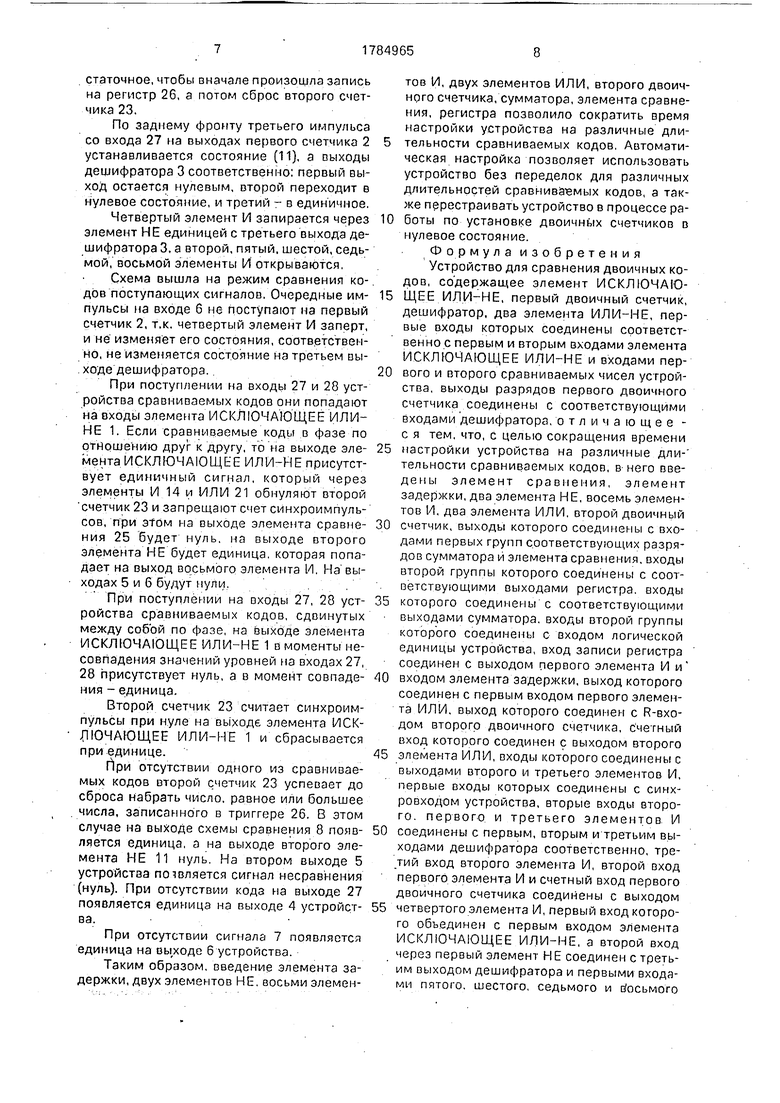

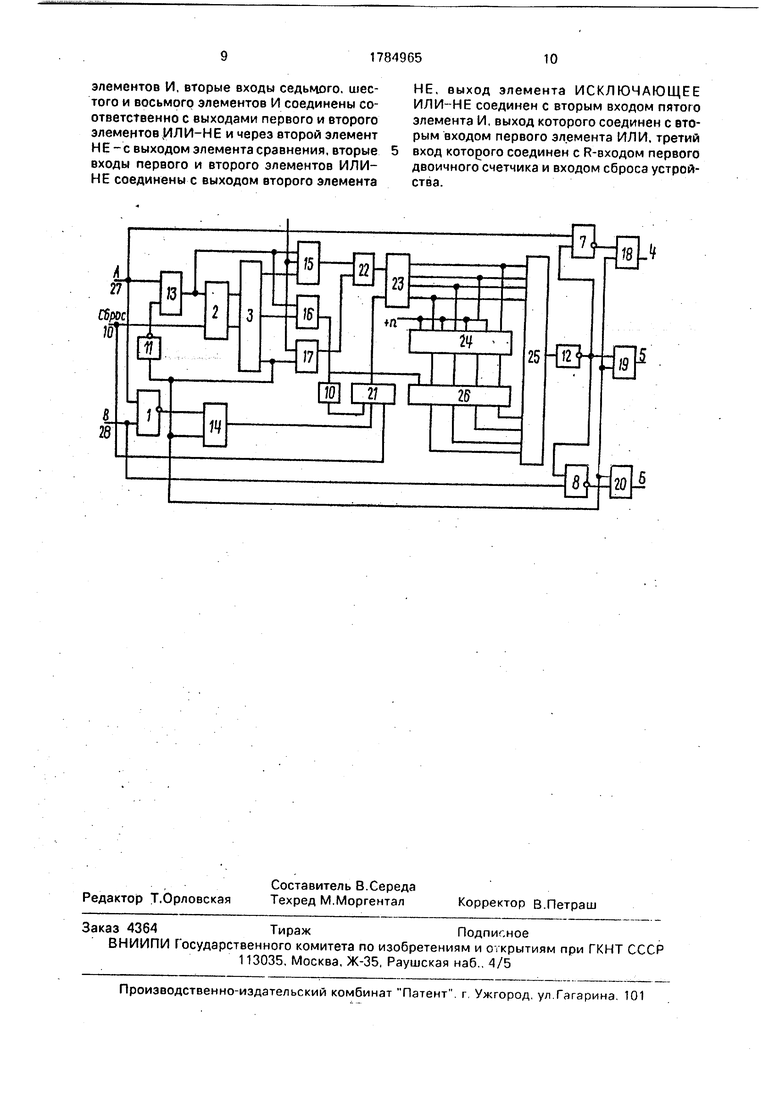

На фиг. 1 изображена электрическая функциональная схема устройства.

Устройство содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 1. первый двоичный счетчик 2, дешифратор 3, два элемента ИЛИ-НЕ 7, 8, элемент задержки 10, два элемента НЕ 10, 11, восемь элементов И 13-20, два элемента ИЛИ 21, 22, второй двоичный счетчик 23, сумматор 24, элемент сравнения 25, регистр 26,

Первые входы первого 7, второго 8 элементов ИЛИ-НЕ соединены соответственно с первым вторым входами элемента 1

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и являющихся первым 27 и вторым 28 входами устройства, выходы двоичного счетчика 2 соединены с соответствующими входами дешифратора 3, выходы второго двоичного счетчика 23 . соединены с первыми входами соответствующих разрядов Ъумматора 24 и с входами первой группы элемента сравнения 25, вторая группа входов которого соединена с соответствующими выходами регистра 26, входы регистра 26 соединены с соответствующими выходами сумматора 24, вторые входы всех разрядов которого соединены с плюсом питания, записывающий вход регистра 26 соединен с выходом первого элемента И 16, и входом элемента задержки 10. выход которого соединен с первым входом первого элемента ИЛИ 21, выход первого элемента ИЛИ 21 соединен с R-входом второго двоичного счетчика 23, счетный вход которого соединен с выходом второго элемента ИЛИ 22, входы которого соединены с выходами второго 15 и третьего 17 элементов И, первые входы которых соединены с синхровходом устройства, вторые же входы второго 15, первого 16 и третьего 17 элементов И соединены с первым, вторым и третьим выходами дешифратора 3 соответственно, входы: третий второго элемента И, первый первого элемента И и счетный вход первого двоичного счетчика соединены с выходом четвертого элемента И, первый вход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ- НЕ 1, а второй вход через первый элемент НЕ соединен с третьим выходом дешифратора 3-й вторым входом третьего и первыми входами пятого, шестого, седьмого, восьмого элементов И, вторые же входы седьмого и шестого элементов И соединены соответственно с выходами второго, первого элементов ИЛИ-НЕ и, через второй элемент НЕ, с выходом элемента сравнения, вторые входы первого, второго элементов ИЛИ-НЕ соединены с выходом второго элемента НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 1 соединен с вторым входом пятого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с R-входом первого двоичного счетчика 2 и входом сброса устройства, а выходы седьмого, восьмого, шестого элементов И являются выходами устройства.

Устройство для сравнения двоичных кодов работает следующим образом.

При включении питания первый 2 и второй 23 счетчики обнуляются. Соответственно на выходах дешифратора 3 тоже 0 . Единичное состояние первого выхода дешифратора 3 соответствует состоянию второго, первого выходов первого счетчика 2 - ( Q1). соответственно единичное состояние второго выхода дешифратора 3 - (10 ) и 5. третьего-(11). Поэтому в начальный момент третий выход дешифратора 3 находится в нулевом состоянии и запирает третий, шестой, седьмой, восьмой элементы И и через элемент НЕ 10 отпирает четвертый элемент

0 И. Со входа 10 поступает первый импульс на счетный вход счетчика 2, через четвертый элемент И, и по заднему фронту этого импульса на первом выходе первого счетчика 2 появляется единица. Первый выход де5 шифратора 3 переходит в единичное состояние, и открывает второй элемент И 15, но синхроимпульсы еще не попадают на счетный вход второго счетчика 23 через схему ИЛИ 21 т.к. второй элемент И 15 заперт

0 нулевым сигналом со входа 27 через четвертый элемент И.

Первый импульс со входа 27 также поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 1, при поступлении сигнала со вхо5 да 28. на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 1 появляется единица, но она не попадает на R-вход второго счетчика 23, через пятый элемент И и ИЛИ 21, т.к. пятый элемент И закрыт нулем, поступающим с

0 третьего выхода дешифратора 3. Когда поступает второй импульс со входа 27 на второй элемент И 15, через четвертый и второй элемент ИЛИ второй счетчик 23 считает син - хроимпульсы до тех пор, пока не приходит

5 задний фронт второго импульса со входа 27, который переводит первый счетчик 2 в состояние (10) и на первом выходе дешифратора 3 появляется нуль, запирающий второй элемент И 15.

0 В этот же момент появляется единица на втором выходе дешифратора 15, которая открывает первый элемент И, и по переднему фронту третьего импульса со входа 27 на выходе первого элемента И появляется еди5 ница. Происходит запись на регистр 26 содержимого второго счетчика 23 минус единица, Единица вычитается сумматором

24. Вычитание единицы производится дяа того,чтобы интервал времени, насчитанный

0 вторым счетчиком 23, был не больше длительности импульса, поступающего со входа 27. Для увеличения точности измерения длительности импульса, поступающего со входа 27, можно увеличить частоту синхро5 импульсов.

Единичный сигнал с выхода первого элемента И также поступает на R-вход второго счетчика 23, через элемент задержки 10 и элемент ИЛИ 21 и обнуляет второй счетчик 23. Время задержки выбирается достаточное, чтобы вначале произошла запись на регистр 26, а потом сброс второго счетчика 23.

По заднему фронту третьего импульса со входа 27 на выходах первого счетчика 2 устанавливается состояние (11), а выходы дешифратора 3 соответственно: первый выход остается нулевым, второй переходит в нулевое состояние, и третий - в единичное.

Четвертый элемент И запирается через элемент НЕ единицей с третьего выхода дешифратора 3, а второй, пятый, шестой, седьмой, восьмой элементы И открываются,

Схема вышла на режим сравнения кодов поступающих сигналов. Очередные импульсы на входе б не поступают на первый счетчик 2, т.к. четвертый элемент И заперт, и не изменяет его состояния, соответственно, не изменяется состояние на третьем выходе дешифратора.

При поступлении на входы 27 и 28 устройства сравниваемых кодов они попадают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ- НЕ 1. Если сравниваемые коды в фазе по отношению друг к другу, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ присутствует единичный сигнал, который через элементы И 14 и ИЛИ 21 обнуляют второй счетчик 23 и запрещают счет синхроимпульсов, при этом на выходе элемента сравнения 25 будет нуль, на выходе второго элемента НЕ будет единица, которая попадает на выход восьмого элемента И, На выходах 5 и 6 будут нули.

При поступлении на входы 27, 28 устройства сравниваемых кодов, сдвинутых между собой по фазе, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 1 в моменты несовпадения значений уровней на входах 27, 28 присутствует нуль, а в момент совпадения - единица.

Второй счетчик 23 считает синхроимпульсы при нуле на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 1 и сбрасывается при единице.

Г1ри отсутствии одного из сравниваемых кодов второй счетчик 23 успевает до сброса набрать число, равное или большее числа, записанного в триггере 26. В этом случае на выходе схемы сравнения 8 появляется единица, э на выходе второго элемента НЕ 11 нуль. На втором выходе 5 устройства пошляется сигнал несравнения (нуль). При отсутствии кода на выходе 27 появляется единица на выходе 4 устройства.

При отсутствии сигнала 7 появляется единица на выходе 6 устройства.

Таким образом, введение элемента задержки, двух элементов НЕ. восьми элементов И, двух элементов ИЛИ, второго двоичного счетчика, сумматора, элемента сравнения, регистра позволило сократить время настройки устройства на различные длительности сравниваемых кодов. Автоматическая настройка позволяет использовать устройство без переделок для различных длительностей сравниваемых кодов, а также перестраивать устройство в процессе ра0 боты по установке двоичных счетчиков в нулевое состояние.

Формула изобретения Устройство для сравнения двоичных кодов, содержащее элемент ИСКЛЮЧАГО5 ЩЕЕ ИЛИ-НЕ, первый двоичный счетчик, дешифратор, два элемента ИЛИ-НЕ, первые входы которых соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и входами пер0 вого и второго сравниваемых чисел устройства, выходы разрядов первого двоичного счетчика соединены с соответствующими входами дешифратора, отличающее - с я тем. что, с целью сокращения времени

5 настройки устройства на различные дли- тельности сравниваемых кодов, в него введены элемент сравнения, элемент задержки, два элемента НЕ, восемь элементов И, два элемента ИЛИ, второй двоичный

0 счетчик, выходы которого соединены с входами первых групп соответствующих разрядов сумматора и элемента сравнения, входы второй группы которого соединены с соответствующими выходами регистра, входы

5 которого соединены с соответствующими выходами сумматора, входы второй группы которого соединены с входом логической единицы устройства, вход записи регистра соединен с выходом первого элемента И и

0 входом элемента задержки, выход которого соединен с первым входом первого элемента ИЛИ. выход которого соединен с R-вхо- дом второго двоичного счетчика, счетный вход которого соединен с выходом второго

5 элемента ИЛИ, входы которого соединены с выходами второго и третьего элементов И, первые входы которых соединены с синх- ровходом устройства, вторые входы второго, первого и третьего элементов И

0 соединены с первым, вторым и третьим выходами дешифратора соответственно, тре- тий вход второго элемента И, второй вход первого элемента И и счетный вход первого двоичного счетчика соединены с выходом

5 четвертого элемента И, первый вход которого объединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, а второй вход через первый элемент НЕ соединен с третьим выходом дешифратора и первыми входами пятого, шестого, седьмого и восьмого

элементов И, вторые входы седьмого, шестого и восьмого элементов И соединены соответственно с выходами первого и второго элементов ,ИЛ И-НЕ и через второй элемент НЕ -с выходом элемента сравнения, вторые входы первого и второго элементов ИЛИ- НЕ соединены с выходом второго элемента

НЕ. выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ соединен с вторым входом пятого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с R-входом первого двоичного счетчика и входом сброса устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования языков | 1983 |

|

SU1111176A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011228C1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1160404A1 |

| Устройство для поиска минимального значения интенсивности размещения в полносвязных матричных системах при двунаправленной передаче информации | 2016 |

|

RU2634198C1 |

| Устройство автоматической дискретной регулировки чувствительности радиоприемника | 1989 |

|

SU1748226A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано в модулях обмена с периферийными устройствами и в контрольно-проверочной аппаратуре при анализе достоверности передачи информации с последующей ее коррекцией. Цель изобретения - сокращение времени настройки устройства на различные длительности сравниваемых кодов Устройство для сравнения двоичных кодов содержит элемент исключающее ИЛИ-НЕ, два двоичных счетчика, дешифратор, два элемента ИЛИ-НЕ, элемент задержки, восемь элементов И, два элемента ИЛИ, сумматор, элемент сравнения, регистр Устройство позволяет без дополнительного монтажа схемы настроить его на длительность сравнйвае ых кодов, а также производить перенастройку схемы во время работы устройства по сигналам сброса 1 ил. сл

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU781807A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения двоичных кодов | 1982 |

|

SU1072038A1 |

| к/ | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1992-12-30—Публикация

1990-10-16—Подача