со

О) СП

о

00

00

11

Изобретений относится к вычисли- тельиоГ технике и может быть использовано при проектировании многопроцессорных нычислительных комплексов .

Цель изобретения - повышение надежности устройства за счет оптимизации контроля.

На фиг. 1 представлена структурная схема устройства;на фиг. 2 - схема блоков контроля;на фиг. 3 - схема блока микропрограммного управления .

Устройство содержит (фиг. 1) с первого по четвертый блоки элементов И 1 - А, регистр 5 обмена с группой 6 информационных и rpynnovi 7 контрольных разрядов, группу 8 блоков контроля по модулю, регистр 9 исправности,блок 10 микропрограммного управления, группу 11 элементов И,кроме этого, изображены информационные шины второй 12 и первой 13 магистралей, шина 14 состояния,шины 15,16 и 17,18 сопровождения данных и опроса второй и первой магистралей вход 19 задания режима устройства, выход 20 готовности устройства.

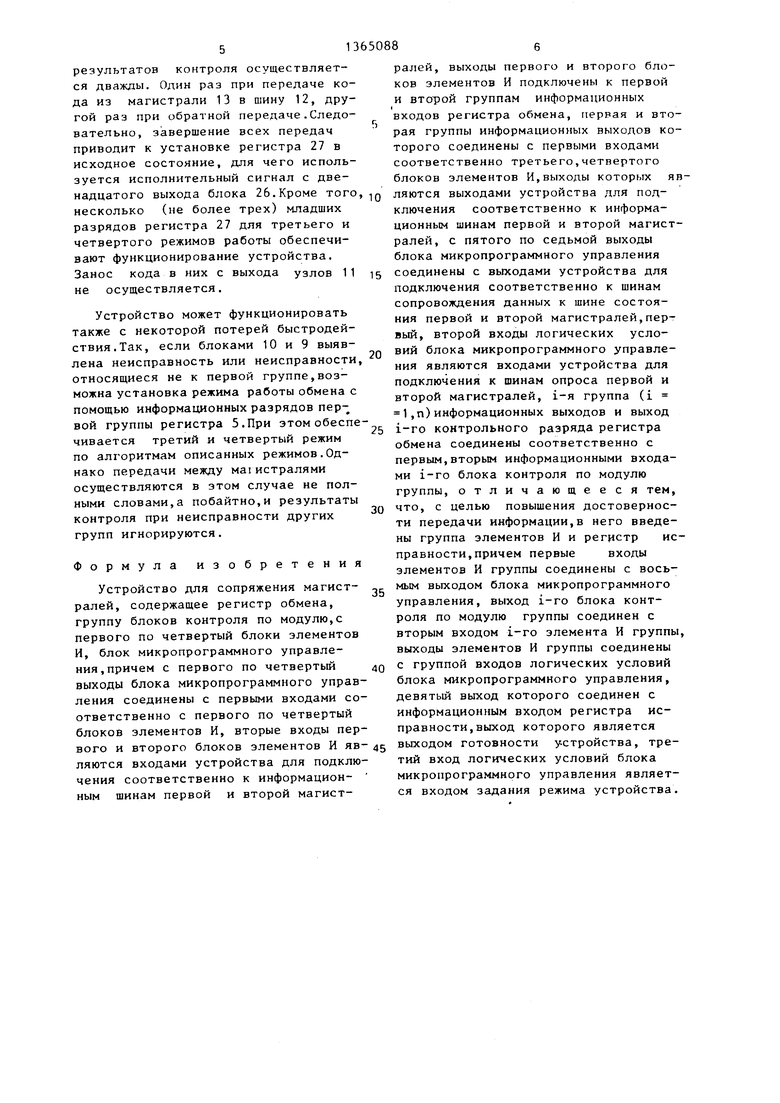

Блок 8 контроля по модулю содержит (фиг. 2) сумматор 21 по модулю два, элемент 22 сравнения.

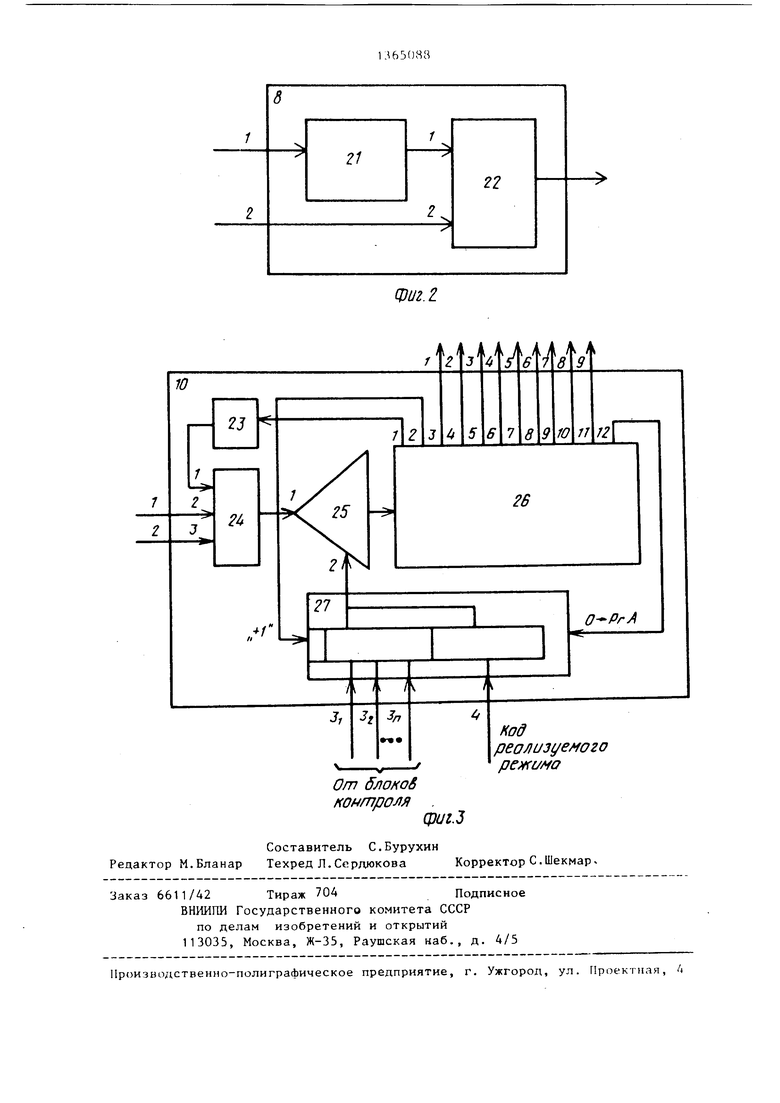

Блок 10 микропрограммного управления содержит (фиг. 3) элемент 23 задержки, элемент ИЛИ 24, дешифратор 25, блок 26 постоянной памяти, регистр 27 адреса.

Устройство работает следующим образом.

5

0

5

0

5

жимого из регис1ра 5 обмена черен блок 3 в эту же магистраль; ньщача информации из второй информационной магистрали 12 через блок 2 в регистр 5 и возврат содержимого из рег истра 5 обмена через блок 4 в магистраль 12; передача адресно-числовой информации из магистрали 13 через регистр 5 обмена в магистраль 12 с контролем групп (побайтно) передаваемой информации в блоках контроля 8 и анализ исправности устройства в блоке 10; передача адресной информации из магистрали 13 через регистр 5 обмена в магистраль 12 и возврат числовой информации из магистрали 12 через регистр 5 обмена в магистраль 13 с контролем групп (побайтно) всех передач в блоках 8 и анализ исправности устройства в блоке 10; передача управляющего слова из магистрали 13 через одну из групп регистра 5 обмена в магистраль 12 и обмен адресно- числовой информацией между магистралями, осуществляемый по этой группе.

Первые два режима являются проверочными. С их помощью осуществляется проверка исправности оборудования магистралей, передач и регистра обмена .

Третий и четвертый режимы являются рабочими.

Последний режим является резервным и служит для осуществления байтовой передачи (или обмена последовательным кодом) между магистралями по первой группе информационных разрядов регистра обмена, в случае фик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании многопроцессорных вычислительных комплексов. Целью изобретения является повышение надежности устройства за счет оптимизации контроля. Устройство содержит с первого по четвертый блоки элементов И 1,2,3,4, регистр 5 обмена, группу 8 блоков контроля по модулю, регистр 9 исправности, блок 10 микропрограммного управления, группу 11 элементов И.Устройство осуществляет приемопередачу информации между двумя магистралями, осуществляя ее полный контроль. 3 ил.

Код, задающий режим работы устрой- 40 сации средствами контроля неисправства,поступает на четвертый вход блока 10 и запоминается в старших разрядах регистра 27 этого блока, предполагается, что каждая из информационных магистралей задействована на свой процессор, причем один из процессоров,например, связанный с перпой информационной магистралью, является ведущим, другой - ведомым, а установка кода режима в блоке 10 осуществляется ведущим процессором

В зависимости от кода, зафиксированного в старших разрядах регистра 27 адреса, возможна реализация одного из следующих режимов обмена между рс1Ч1стром 5 и магистралями 13 и 12: ныдача информации из первой нифирмаци1тми1)й магистрали 13 через iiiioK 1 и ptM HC i p 3 и возврат еодерности в одной или нескольких группах передач, кроме первой. В этом режиме обмен начинается передачей управляющего слова по шине 13 через g регистр обмена в шину 12,при этом в передаваемом управляющем слове указывается и направление обмена.

После установки соответствующего режима на первьш или второй вход блока 10 поступает сигнал, снимаемый с шины 18 или 16, который запускает блок 10 микропрограммного управления. Этот сигнал, пройдя схему 24 и дешифратор 25, поступает на вход блока 26 и вызывает считывание информации из ячейки накопителя по адресу установленного режима. В результате на выходах блока 26 считываются те или иные исполнительные сигналы.

0

5

При реализации первого режима работы исполнительные сигналы появляются на первом, втором и третьем выходах блока 26. Сигнал, выработан- ный на третьем выходе 26 (первый выход блока 10), поступает на второй вход блока 1 и осуществляет передачу кода с шины 13 в регистр 5.Сигнал, считанный с второго выхода блока 26, поступает на вход +1 регистра 27 и увеличивает на единицу содержимое этого регистра. Сигнал,снимаемый с первого выхода блока 26 и задержанный элементом 23 на время окон чания переходных процессов в регистре 27 и блока 26, поступает на первый вход схемы 2А и производит новый опрос блока 26 по следующему адресу, в результате чего исполнительные сигналы появляются на пятом, седьмом и двенадцатом выходах блока 26.Сигнал, выработанный на пятом выходе блока 26 (третий выход блока 10), поступает на второй вход блока 3 и осуществляет передачу кода из регистра 5 на шину 13. Сигнал,считанный с седьмого выхода блока 26 (пятый В11ХОД блока 10) поступает на шину 17 и сопровождает информацию, выданную на шину 13. Сигнал, снимаемый с двенадцатого выхода блока 26 осуществляет установку регистра 27 в исходное состояние. После этого устройство вновь готово к реализа- ции любого режима работы.

Работа устройства при реализации второго режима аналогична работе устройства для рассмотренного случая Опрос блока 10 осуществляется сигиа- лом, снимаемым с шины 16. Исполнительные сигналы появляются сначала на втором, а затем на четвертом и шестом выходах блока 10. Их функции и назначение аналогичны функциям и назначению исполнительных сигналов, снимаемых с первого,третьего и пятого выходов блока 10, с той разницей что они отнесены к шинам 12 и 15.

Если на четвертом входе блока 10 установлен код, соответствующий третьему режиму работы, то сигнал опроса, поступивший на первый вход блока 10 с шины 18, вызывает считывание исполнительных сигналов с первого, второго и третьего выходов блока 26. С помощью этих сигналов производится передача кода из магистрали 13 в регистр 5, увеличивается содержимое

регистра 27 и 1роизводится опрос блока 26 по новому адресу. (Указанная последовательность действий подробно описана при рассмотрении первого режима работы).После заноса кода в регистр 5 для каждой группы разрядов регистра 5 с помощью узла 21 блока 8 контроля осуществляется свертка по модулю два содержимого информационных разрядов этих групп и сравнение в узле 22 результатов свертки со значением контрольного разряда соответствующей группы.Резултаты сравнения (для каждой группы) с выходов блоков 8 поступают на вторые входы соответствующих узлов 11,а опрос блока 26, произведенный по новому адресу, вызывает появление исполнительных сигналов на первом и десятом выходах блока 26.Последний исполнительный сигнал (сигнал с восьмого выхода блока 10) поступает на первые входы узлов 11 и переписывает состояние результатов контроля в младшие разряды регистра 27 блока 10. Исполнительный сигнал,снимаемый С первого выхода блока 26 и задержанный элементом 27, производит новый повторный опрос блока 26.

Если в результате контроля не обнаружено неисправностей ни в одной из анализируемых групп, то в младшие разряды регистра 27 занесен нулевой код или код соответствующей исправности. Повторный опрос блока 26 приводит к выработке исполнительных сигналов, обеспечивающих управление блоком 4 для передачи кода из регистра 5 в шину 12 и установку регистра 27 в исходное состояние. Обнаружение схемами 8 контроля несоответствия в результатах сравнения свернутой информации по какой-либо группе с контрольным разрядом этой группы для одной или нескольких групп приводит к тому,что в регистре 27 с узлов 11 занесен код, отличный от состояния исправности. Повторный опрос блока 26 приводит к выработке исполнительных сигналов, производящих установку регистра 9 в состояние, индицирующее номер неисправной группы или групп, и осуществляющих передачу сигнала неисправности по шине 14.

Четвертый режим работы аналогичен рассмотренному и отличается от него только тем,что в этом режиме опрос

результатов контроля осуществляется дважды. Один раз при передаче кода из магистрали 13 в шину 12, другой раз при обратной передаче.Следовательно, завершение всех передач приводит к установке регистра 27 в исходное состояние, для чего используется исполнительный сигнал с двенадцатого выхода блока 26.Кроме того несколько (не более трех) младших разрядов регистра 27 для третьего и четвертого режимов работы обеспечивают функционирование устройства. Занос кода в них с выхода узлов 11 не осуществляется.

Устройство может функционировать также с некоторой потерей быстродействия.Так, если блоками 10 и 9 выявлена неисправность или неисправности относящиеся не к первой группе,возможна установка режима работы обмена с помощью информационных разрядов пер- вой группы регистра 5.При этом обеспечивается третий и четвертый режим по алгоритмам описанных режимов.Однако передачи между Maiистралями осуществляются в этом случае не полными словами,а побайтно,и результаты контроля при неисправности других групп игнорируются.

Формула изобретения

Устройство для сопряжения магистралей, содержащее регистр обмена, группу блоков контроля по модулю,с первого по четвертый блоки элементов И, блок микропрограммного управления, причем с первого по четвертый выходы блока микропрограммного управления соединены с первыми входами соответственно с первого по четвертый блоков элементов И, вторые входы первого и второго блоков элементов И яв ляются входами устройства для подключения соответственно к информационным шинам первой и второй магист

0

5

0

5

5

0

5

0

ралей, выходы первого и второго блоков элементов И подключены к первой

и второй группам информационных I

входов регистра обмена, первая и вторая группы информационных выходов которого соединены с первыми входами соответственно третьего,четвертого блоков элементов И,выходы которых являются выходами устройства для подключения соответственно к информационным шинам первой и второй магистралей, с пятого по седьмой выходы блока микропрограммного управления соединены с выходами устройства для подключения соответственно к шинам сопровождения данных к шине состояния первой и второй магистралей,первый, второй входы логических условий блока микропрограммного управления являются входами устройства для подключения к шинам опроса первой и второй магистралей, i-я группа (i 1,п)информационных выходов и выход i-ro контрольного разряда регистра обмена соединены соответственно с первым,вторым информационными входами i-ro блока контроля по модулю группы, отличающееся тем, что, с целью повышения достоверности передачи информации,в него введены группа элементов И и регистр исправности, причем первые входы элементов И группы соединены с восьмым выходом блока микропрограммного управления, выход i-ro блока контроля по модулю группы соединен с вторым входом i-ro элемента И группы, выходы элементов И группы соединены с группой входов логических условий блока микропрограммного управления, девятый выход которого соединен с информационным входом регистра исправности, выход которого является выходом готовности устройства, третий вход логических условий блока микропрограммного управления является входом задания режима устройства.

От контроля .

фиг.З

Составитель С.Бурухин

Редактор М.Бланар Техред Л.Ссрлюкова

Заказ 6611/42 Тираж 704Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг.

Код

реализуемого режи/ о

Корректор С. Шекмар.

| Устройство для согласования интер-фЕйСОВ | 1979 |

|

SU822166A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Селлерс Ф | |||

| Автоматический поиск неисправностей в СЦВН | |||

| - М.: Мир, 1972, с | |||

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

Авторы

Даты

1988-01-07—Публикация

1986-05-26—Подача