Изобретение относится к цифровой вычислительной технике и может быть использовано в составе специализирОЕ анных цифровых вычислительных машин (СЦВМ) иили систем обработки и передачи цифровых данных.

Цель изобретения - повышение надежности устройства.

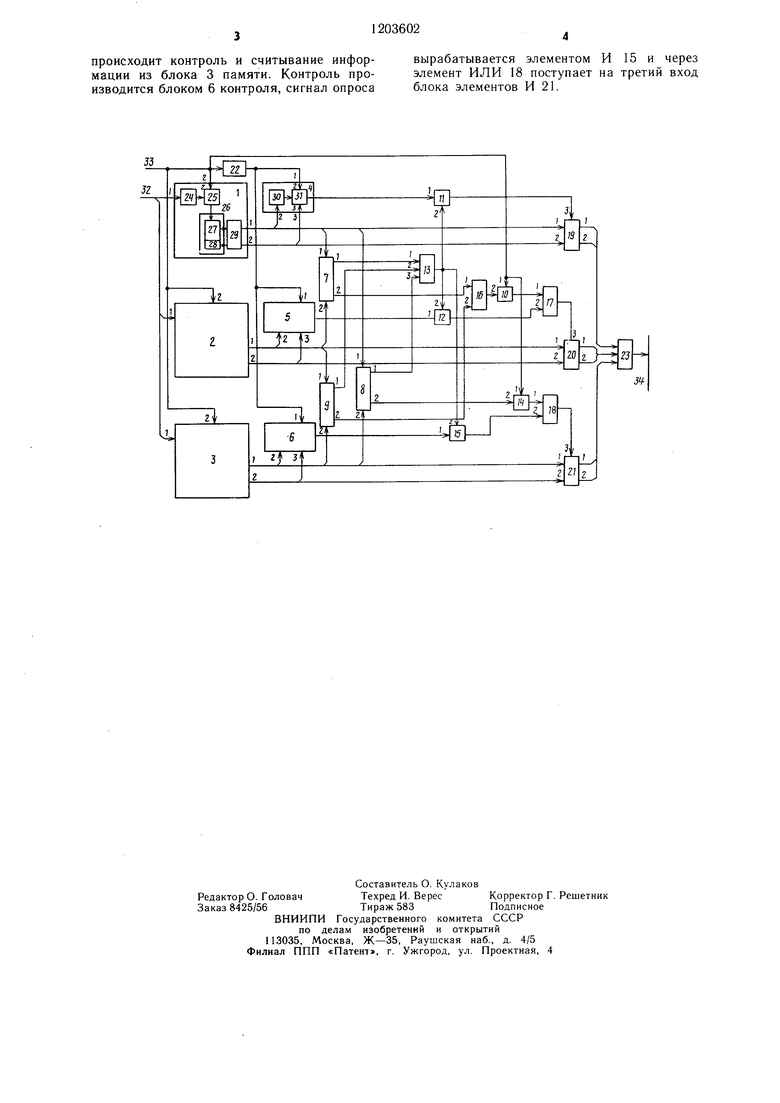

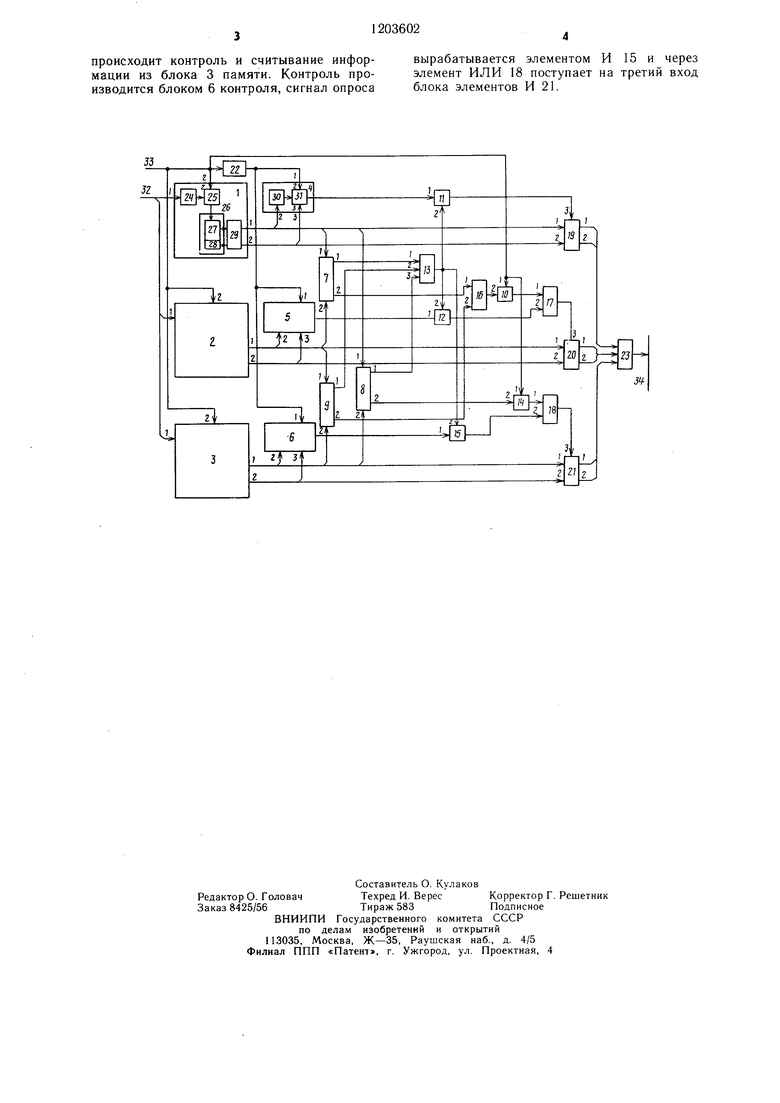

На чертеже представлена блок-схема устройства.

Устройство содержит первый 1, второй 2 и третий 3 блоки памяти, первый 4, второй 5 и третий 6 .блоки контроля, первый 7, второй 8 и третий 9 блоки сравнения, первый 10, второй 1, третий 12, четвертый 3, пятый 14 и шестой 15 элементы И, первый 16, второй 17 и третий 18 элементы ИЛИ, первый 19, второй 20 и третий 21 блоки элементов И, элемент 22 задержки, блок 23 элементов ИЛИ, регистр 24 адреса, дешифратор 25 кода адреса, накопитель 26, информационное поле 27 накопителя, поле 28 контрольных разрядов накопителя, выходной регистр 29, блок 30 свертки по модулю 2, блок 31 сравнения, адресный вход 32, вход 33 опроса и выходную шину 34.

Запоминаюшее устройство работает сле- дуюш,им образом.

На вход 32 устройства подается код адреса, а на вход 33 - сигнал опроса. В каждом блоке 1-3 памяти код адреса подается на вход регистра 24, и сигнал опроса - на второй вход дешифратора 25, управляю- шего регистром 24. При наличии сигнала опроса на входе дешифратора 25 на одном из его выходов появляется сигнал, при помощи которого выбирается информация из соответствуюш,ей ячейки накопителя 26. С выхода информационного поля 27 и поля 28 контрольных разрядов накопителя 26 считанная информация поступает на вход регистра 29. С выхода регистра 29 информация поступает на выходы блоков 1-3 памяти. Информационная ее часть с первого выхода блока 1 памяти подается на первые входы блоков 7 и 8 сравнения, с первого блока 2 памяти подается на второй вход блока 7 и на первый вход блока 9, с первого выхода блока 3 памяти подается на вторые входы блоков 8 и 9. В блоках 7-9 сравнения происходит поразрядное сравнение информации, считанной из блоков памяти. В случае равенства информации, считанной из блоков 1 и 2 памяти, на втором выходе блока 7 формируется сигнал «Равно, который через элемент ИЛИ 16 поступает на второй вход элемента И 10. При наличии на nepeorvi входе элемента И 10 сигнала опроса, он формирует сигнал, поступающий через элемент ИЛИ 17 на третий вход блока элементов И 20, тем самым разрешающий считывание информации и ее контрольных признаков из блока 2 памяти через блок 23 на выходную шину 34. Аналогично происходит сравнение блоком 9 информации, считываемой из блоков 2 и 3 памяти и, в случае равенства, передача информации и ее контрольных признаков на выходную шину 34. Также выполняется блоком 8 сравнение информации, считываемой из блоков 1 и 3 памяти. При ее равенстве на втором выходе блока 8 формируется сигнал «Равно, который подается на второй вход элемента И 14. При наличии на первом входе элемента

И 14 сигнала опроса, он формирует сигнал разрешения считывания информации, который через элемент ИЛИ 18 поступает на третий вход блока 21 и, тем самым, разрешает считывание информации и ее контрольных признаков из блока 3 через блок 23 на выходную шину 34. В случае неравенства информации, считываемой из блоков 1 и 2, 1 и 3, 2 и 3 памяти, на первом выходе каждого из блоков 7, 8 и 9 сравнения формируется сигнал «не равно, который поступает на первый, третий и второй входы элемента И 13 соответственно. При наличии на всех входах одновременно элемента И 13 сигналов «Не равно элемент И 13 выработает разрешающий сигнал для элементов И 11, 12 и 15. Информация с выходов блоков 1-3 памяти поступает соответственно на входы блоков 4-6 контроля, где ее информационная часть свертывается при помощи блока 30 по заложенным контрольным признакам. Результаты свертки

сравниваются в каждом блоке 4, 5 и 6 с контрольными признаками блоков 31 сравнения. Сигнал опроса подается на первые входы блоков 4-6 контроля с выхода элемента 22 задержки (для синхронизации работы устройства). В случае равенства результата

свертки информационной части и контрольного признака (признаков) в блоке 4, а также наличия сигнала опроса на входе этого блока, блок 31 блока 4 формирует сигнал, который поступает на первый вход элемента И 11. При наличии на втором входе элемента И 11

сигнала разрешения на его выходе появляется сигнал, поступающий на третий вход блока элементов И 19 и, тем самым, раз- решаюпхий передачу информации и ее контрольных признаков, поступающих на вход

блока элементов И 19 дальще - через блок элементов ИЛИ 23 на выходную шину 34 устройства. В случае неравенства результатов свертки информационной части и контрольного признака (признаков) в блоке 4, этот блок не вырабатывает сигнал опроса.

В работу включатся цепи, обеспечивающие считывание информации из блока 2 памяти через блок элементов И 20 и блок элементов ИЛИ 23 на выходную шину 34 устройства. Контроль информации в этом случае осуществляется блоком 5 контроля, работа которого аналогична работе блока 4 контроля. Сигнал опроса формируется элементом И 12 и через элемент ИЛИ 17 поступает на третий вход блока элементов И 20. Аналогично

происходит контроль и считывание информации из блока 3 памяти. Контроль производится блоком 6 контроля, сигнал опроса

вырабатывается элементом И 15 и через элемент ИЛИ 18 поступает на третий вход блока элементов И 21.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1984 |

|

SU1236560A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1072102A1 |

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1439685A1 |

| Оперативное запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1089628A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для вычисления нормированных статистических моментов случайных процессов | 1986 |

|

SU1385131A2 |

| Устройство для сопряжения магистралей | 1986 |

|

SU1365088A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Устройство для ввода информации | 1987 |

|

SU1539761A1 |

33

| Запоминающее устройство | 1982 |

|

SU1049982A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-01-07—Публикация

1984-07-26—Подача