00

со

а

00

ел

10

15

25

Изобретение относится-к вычислительной технике и может быть использовало в системах обработки и передачи цифровых данных повышенной надежности.

Цель изобретения - расширение области применения устройства за счет возможности его реализации на элементах импульсно-потенциальной и потенциальной логики с различным быстродействием.

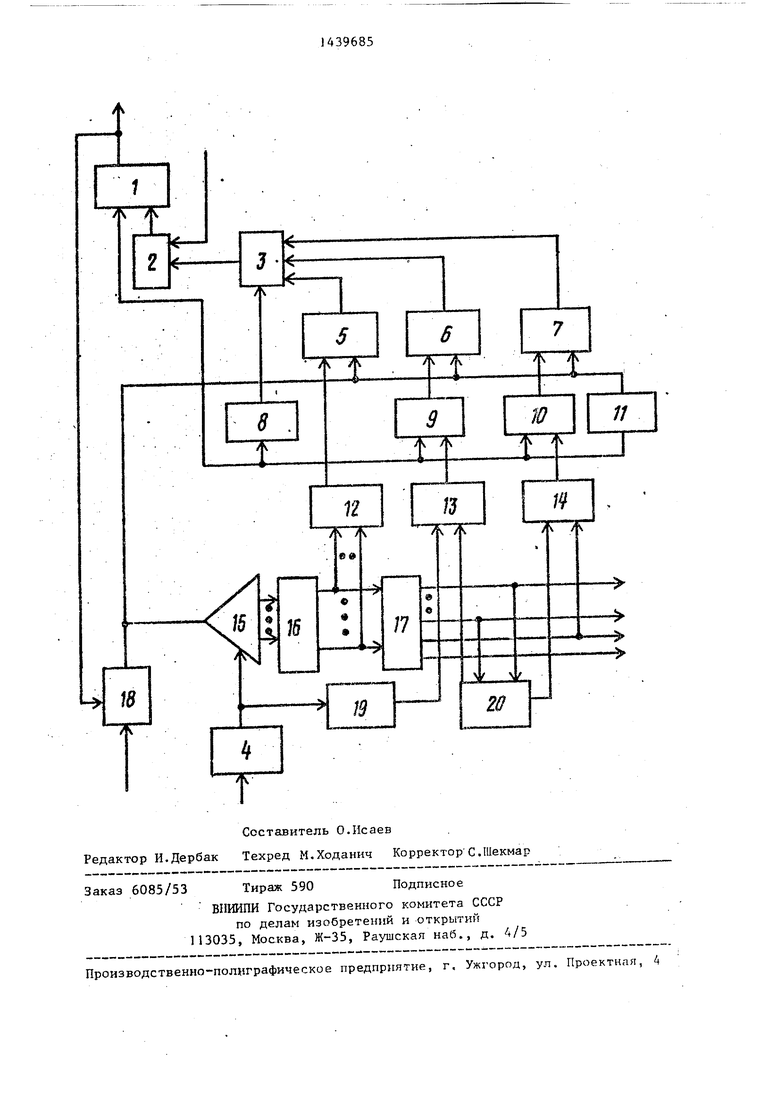

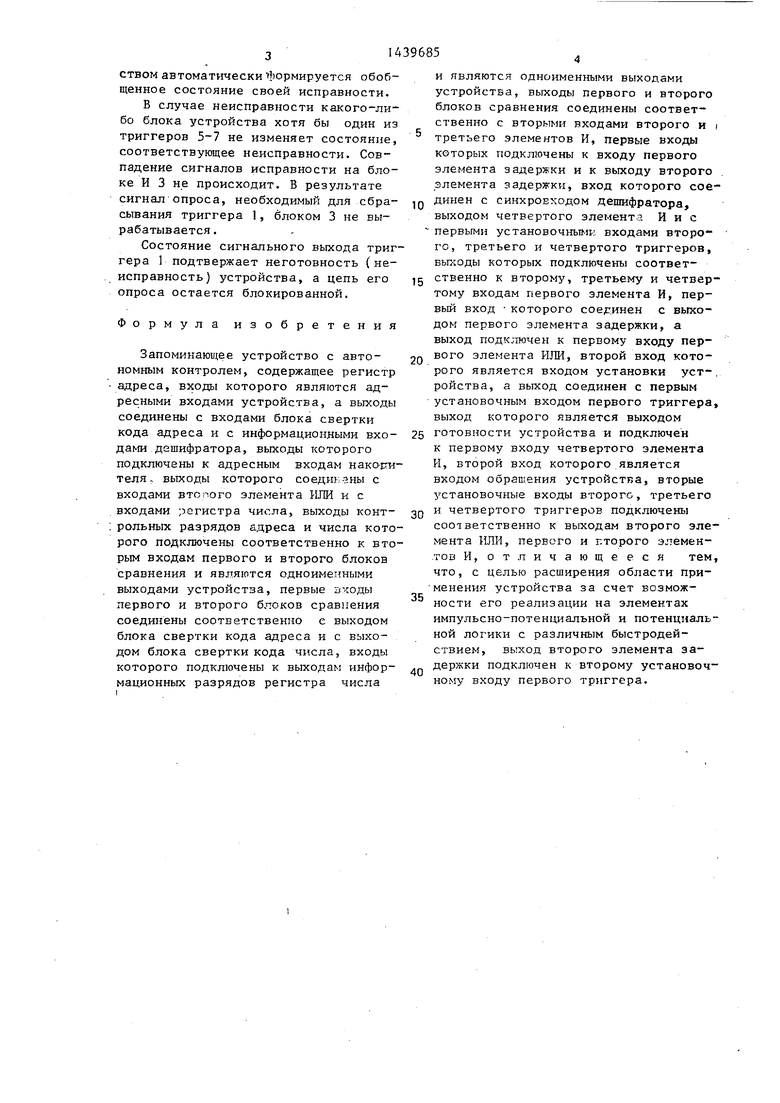

На чертеже представлена схема запоминающего устройства с автономным контролем.

Устройство содерлсит первый триггер 1, первый элемент ИЛИ 2, первый элемент И 3, регистр 4 адреса, второй 5, третий б и четверый 7 триггеры, первый элемент 8 задержки, вто-2п -рой 9 и третий JO элементы PI, второй элемент 11 задержки, второй элемент ИЛИ 12, первый 13 и второй 14 блоки сравнения, дешифратор 15, накоиитель 16, регистр 17 числа, четверый элемент И 18, блок 19 свертки кода адреса и блок 20 свертки кода числа,

Запоминакяцее устройство работает следующим образом.

На второй вход элемента ИЛИ 2 подается сигнал, который, пройдя элемент ИЛИ 2, устанавливает триггер 1 в исходное состояние (или состояние исправности устройства). Затем на вход элемента И 18 подается сигнал опроса, а на входы регистра 4 адреса - код адреса, который свертывается при помощи блока 19 св ертки кода адреса.,Результаты свертки подаются на первьш вход блока 13 сравнения. Сигнал опроса, пройдя через элемент И 18, производит установку триггеров 5-7 в единичное состояние (соо,тве1 ствующее неисправности), и поступает на вход дешифратора 15 и на вход элемента 11 задержки. Этот сигнал, задержанный элементом 11 задержки на время, необходимое для устойчивого считывания информации из накопителя 16 при выполггении накопителя 16. дешифратора 15 и регистра 4 адреса на любой сутдествующей элементной базе, производит установку триггера 1 в инверсное сбстояние (или состояние неисправности устройства).

30

35

10

45

50

При наличии на втором входе деши ратора 15 сигнала опроса, длительность которого определена при помощи блока 11, на одном из выходов дешифратора 15 появляется сигнал, производящий выборку информации из соответствующей ячейки памят. накоп теля 16. С выходов накопителя 16 сч танная информация поступает на вход регистра 17 числа и-на входы элемента ИЛИ 12. Числовой код, зафикси рованный в регистре 17, свертываетс при помощи блока 20 свертки кода числа и поступает на первый вход блока 14 сравнения. На второй вход этого блока подается значение контрольного признака четности числовой информации, который также считывает из накогителя 16 и запоминается в регистре 17. Значение второго (адре ного) контрольного признака подаетс на второй вход блока 13 сравнения. Информация, считанная из выбранной ячейки памяти накопителя 16, пройд элемент ИЛИ 12, поступает на второ вход трр ггера 5, в результате чего последний меняет свое состояние. Эт новое состояние триггера 5 соответствует состоянию исправности (при этом, предполагается, что из выбран ной ячейки памяти накопителя 16 будет считана хотя бы одна единица). Этот случай соответствует исправности цепей опроса дешифратора и нако пителя. Результаты контроля правил ности считанной информации и выбра ного адреса с выходов блоков 13 и 1 сравнения поступают соответственно на вторые входы элементов И 9 и 10. На первые входы этих элементов пост .пает сигнал с выхода элемента 11 за держки. В слз чае правильности прове рок четности элементами 9 и 10 выдается сигнал, поступающий на второй вход триггеров 6 и 7 соответственно .

В результате триггеры 6 и 7 изме няют свое состоя ше. Измененное сос тояние триггеров 5-7 фиксируется на втором, третьем и четвертом вход первого элемента И 3. Опрос элемент И 3 производится сигналом, выбранны элементом 1 и задержанным на элеме

При этом цепь опроса устройства (эле- те 8 задержки. С выхода элемента И

мент И 18, управляемый единичным выходом триггера 1) для приема следующего сигнала блокирована.

0

5

5

п

0

5

0

5

0

При наличии на втором входе дешифратора 15 сигнала опроса, длительность которого определена при помощи блока 11, на одном из выходов дешифратора 15 появляется сигнал, производящий выборку информации из соответствующей ячейки памят. накопителя 16. С выходов накопителя 16 считанная информация поступает на входы регистра 17 числа и-на входы элемента ИЛИ 12. Числовой код, зафиксированный в регистре 17, свертывается при помощи блока 20 свертки кода числа и поступает на первый вход блока 14 сравнения. На второй вход этого блока подается значение контрольного признака четности числовой информации, который также считывается из накогителя 16 и запоминается в регистре 17. Значение второго (адресного) контрольного признака подается на второй вход блока 13 сравнения. Информация, считанная из выбранной ячейки памяти накопителя 16, пройдя элемент ИЛИ 12, поступает на второй вход трр ггера 5, в результате чего последний меняет свое состояние. Это новое состояние триггера 5 соответствует состоянию исправности (при этом, предполагается, что из выбранной ячейки памяти накопителя 16 будет считана хотя бы одна единица). Этот случай соответствует исправности цепей опроса дешифратора и накопителя. Результаты контроля правильности считанной информации и выбранного адреса с выходов блоков 13 и 14 сравнения поступают соответственно на вторые входы элементов И 9 и 10. На первые входы этих элементов посту- .пает сигнал с выхода элемента 11 задержки. В слз чае правильности проверок четности элементами 9 и 10 выдается сигнал, поступающий на второй вход триггеров 6 и 7 соответственно .

В результате триггеры 6 и 7 изменяют свое состоя ше. Измененное состояние триггеров 5-7 фиксируется на втором, третьем и четвертом входах первого элемента И 3. Опрос элемента И 3 производится сигналом, выбранным элементом 1 и задержанным на элемен3 считывается сигнал, который, пройдя элемент ЙШ1 2, изменяет состояние триггера 1, в результате чего устройством aBTOMarvnecKH Нормируется обобщенное состояние своей исправности.

В случае неисправности какого-либо блока устройства хотя бы один из триггеров 5-7 не изменяет состояние, соответствующее неисправности. Совпадение сигналов исправности на блоке И 3 не происходит. В результате сигнал опроса, необходимый для сбра- сывания триггера 1, блоком 3 не вырабатывается .

Состояние сигнального выхода гера 1 подтвержает неготовность (неисправность) устройства, а цепь его опроса остается блокированной.

Формула изобретения

Запоминающее устройство с автономным контролем, содержащее регистр адреса, входы которого являются адресными входами устройства, а выходы соединены с входами блока свертки кода адреса и с информационными входами дешифратора, выходы которого подключены к адресным входам нако-рги теля, выходы которого соединены с входами BTOi.oro элемента ИЛИ и с входами регистра числа, выходы конт- рольных разрядов адреса и числа которого подключены соответственно к вторым входам первого и второго блоков сравнения и являются одноименными выходами устройства, первые входы первого и второго блоков сравнения соединены соответственно с выходом блока свертки кода адреса и с выходом блока свертки кода числа, входы которого подключены к выходам инфор- мационных разрядов регистра числа

Q

5

о Q

0

5

5

и являются одноименными выходами устройства, выходы первого и второго блоков сравнения соединены соответственно с вторыми входами второго и i третьего элементов И, первые входы которых подключены к входу первого элемента задержки и к выходу второго . элемента задержки, вход которого соединен с синхроЕходом дешифратора, выходом четвертого элемента И и с первыми установочньив входами второ- го, третьего и четвертого триггеров, выходы которых подключены соответственно к второму, третьему и четвертому входам первого элемента И, первый вход которого соединен с выходом первого элемента задержки, а выход подключен к первому входу первого элемента ИЛИ, второй вход которого является входом установки уст-, ройства, а выход соединен с первым установочным входом первого триггера, выход которого является выходом готовности устройства и подключен к первому входу четвертого элемента И, второй вход которого является входом обращения устройства, вторые установочные входы второго, третьего и четвертого триггеров подключены соответственно к выходам второго элемента ИЛИ, первого и г.торого элемен- ,тов И, отличающееся тем, что, с целью расширения области при- менения устройства за счет возможности его реализации на элементах импульсно-потенциальной и потенциаль ной логики с различным быстродействием, выход второго элемента задержки подключен к второму установочному входу первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1072102A1 |

| Устройство для контроля дешифратора | 1987 |

|

SU1495801A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Устройство для сопряжения магистралей | 1986 |

|

SU1365088A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки и передачи цифровых данных повышенной надеясности. Целью изобретенрш является расширение области применения устройства за счет возможности его реализации на элементах импульсно- потенциальной и потенциальной логики с различным быстродействием. Устройство содержит накопитель, регистр адреса, регистр числа, блоки свертки кода адреса и кода числа, первый и второй блоки сравнения, триггеры с первого по четвертый, элементы И с первого ПС четвертый, первый и второй элементы ИЛИ, первый и второй элементы задержки. В устройстве осуществляется aвтoнo шый контроль правильности хранения данных г накопителе, правильности функционирования адресных цепей и цепей выборки путем хранения в накопителе кодов сверток числа и адреса, а также путем проверки считанного из накопителя числа на наличие хотя бы одной единицы. Цель изобретения достигается за счет введения в устройство управгяемой обратной связи, осуществляющей формирование сигнала опроса с длительностью, обеспечиватацей устойчивую работу устройства при реализации его на любой известной элементной базе. 1 ил.

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1072102A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1988-11-23—Публикация

1987-03-17—Подача