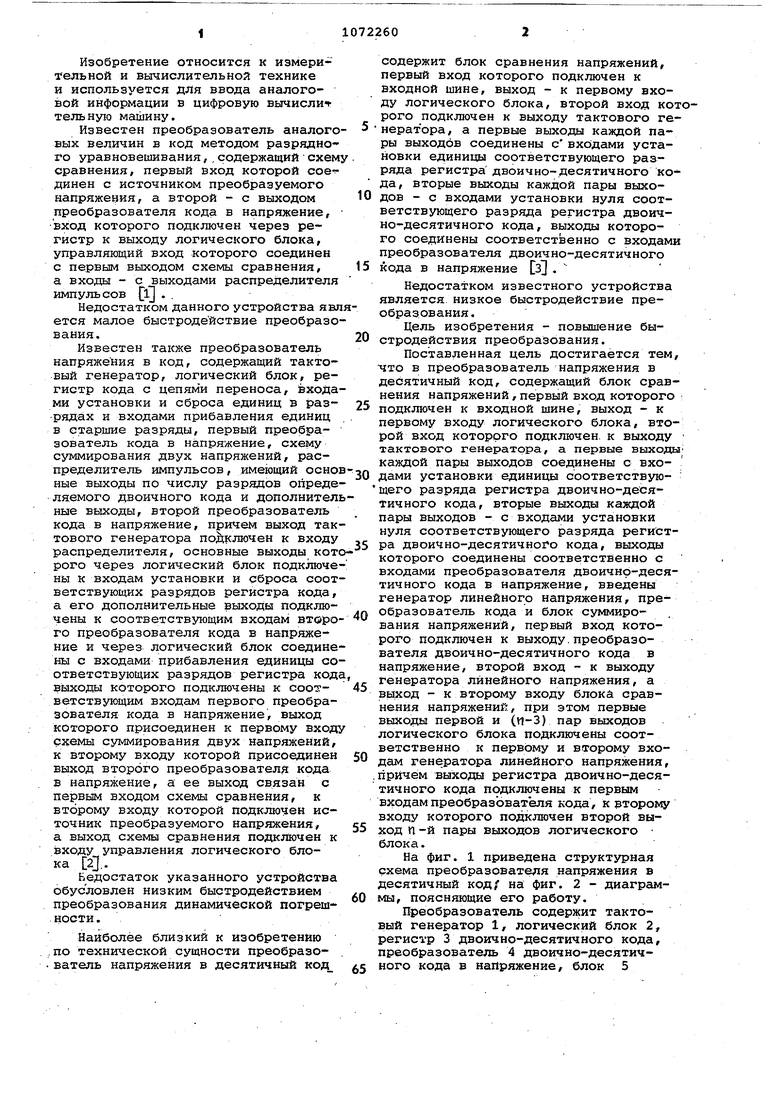

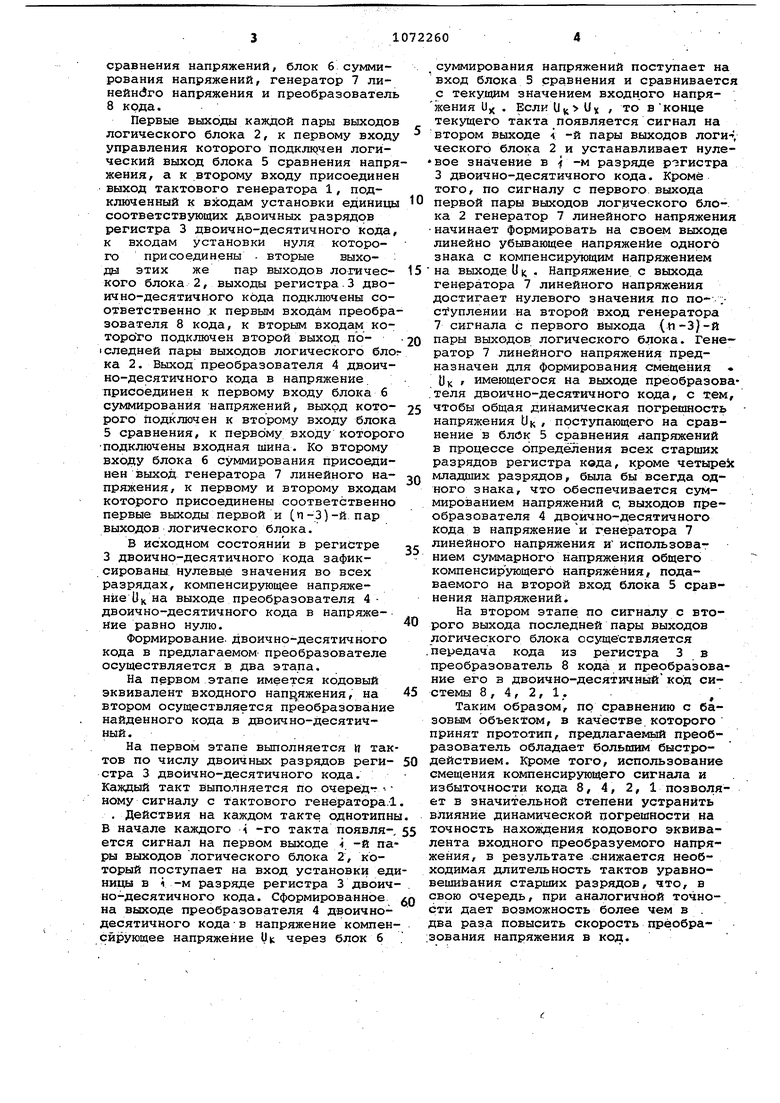

Изобретение относится к измерительной и вычислительной технике и используется для ввода аналого1зой информации в цифровую вычисличтельную машину. Известен преобразователь аналого вых величин в код методом разрядного уравновешивания,,содержащий схем сравнения, первый вход которой соединен с источником преобразуемого напряжения, а второй - с выходом преобразователя кода в напряжение, вход которого подключен через регистр к выходу логического блока, управляющий вход которого соединен с первым выходом схемы сравнения, а входы - с выходами распределителя импульсов jYj .. Недостатком данного устройства явл ется малое быстродействие преобразо вания. Известен также преобразователь напряжения в код, содержащий тактовый генератор, логический блок, регистр кода с цепями переноса, входа ми установки и сброса единиц в разрядах и входами прибавления единиц в старшие разряды, первый преобразователь кода в напряжение, схему суммирования двух напряжений, распределитель импульсов, имеющий осно ные выходы по числу разрядов опреде ляемого двоичного кода и дополнител ные выходы, второй преобразователь кода в напряжение, причем выход так тового генератора подключен к входу распределителя, основные выходы кот рого через логический блок подключе ны к входам установки и сброса соот ветствующих разрядов регистра кода, а его дополнительные выходы подключены к соответствующим входам второ го преобразователя кода в напряжение и через логический блок соедине ны с входами прибавления единицы со ответствующих разрядов регистра код выходы которого подключены к coos- ветствующим входам первого преобразователя кода в напряжение, выход которого присоединен к первому вход схемы суммирования двух напряжений, к второму входу которой присоединен выход второго преобразователя кода в напряжение, а ее выход связан с первым входом схемы сравнения, к второму входу которой подключен источник преобразуемого напряжения, а выход схемы сравнения подключен к входу управления логического блока 2.. Недостаток указанного устройства обусловлен низким быстродействием преобразования динамической погрешности. Наиболее близкий к изобретению ,по технической сущности преобразо ватель напряжения в десятичный код содержит блок сравнения напряжений, первый вход которого подключен к входной шине, выход - к первому входу логического блока, второй вход которого подключен к выходу тактового генератора, а первые выходы каждой пары выходов соединены с входами установки единицы соответствующего разряда регистра двоично-десятичного кода, вторые выходы каждой пары выходов - с входами установки нуля соответствующего разряда регистра двоично-десятичного кода, выходы которого соединены соответственно с входами преобразователя двоично-десятичного кода в напряжение з . Недостатком известного устройства является, низкое быстродействие преобразования. Цель изобретения - повышение быстродействия преобразования. Поставленная цель достигается тем, ЧТО в преобразователь напряжения в десзятичный код, содержащий блок сравнения напряжений, первый вход которого подключен к входной шине, выход - к первому входу логического блока, второй вход которого подключен, к выходу тактового генератора, а первые выходы каждой пары выходов соединены с входами установки единицы соответствую- щего разряда регистра двоично-десятичного кода, вторые выходы каждой пары выходов - с входами установки нуля соответствующего разряда регистра двоично-десятичного кода, выходы которого соединены соответственно с входами преобразователя двоично-десятичного кода в напряжение, введены генератор линейного напряжения, преобразователь кода и блок суммирования напряжений, первый вход которого подключен к выходу.преобразователя двоично-десятичного кода в напряжение, второй вход - к выходу генератора линейного напряжения, а выход - к второму входу блока сравнения напряжений, при этом первые выходы первой и (ц-3) пар выходов логического блока подключены соответственно к первому и второму входам генератора линейного напряжения, причем выходы регистра двоично-десятичного кода подключены к первым входам преобразователя кода, к второму входу которого подключен второй выход П-и пары выходов логического блока. На фиг, 1 приведена структурная схема преобразователя напряжения в десятичный код/ на фиг, 2 - диаграммы, поясняющие его работу. Преобразователь содержит тактовый генератор 1, логический блок 2, регистр 3 двоично-десятичного кода, преобразователь 4 двоично-десятичного кода в напряжение, блок 5 сравнения напряжений, блок 6 суммирования напряжений, генератор 7 линейндго напряжения и преобразователь 8 кода. Первые выходы каждой пары выходов логического блока 2, к первому входу управления которого подклк чен логический выход блока 5 сравнения напря жения, а к второму входу присоединен выход тактового генератора 1, подключенный к входам установки единицы соответствующих двоичных разрядов регистра 3 двоично-десятичного кода, к входам установки нуля которого присоединены - вторые выходы этих же пар выходов логического блока 2, выходы регистра.3 двоично-десятичного кода подключены соответственно к первым входам преобра зователя 8 кода, к вторым входам которого подключен второй выход по1следней пары выходов логического блo ка 2. Выход преобразователя 4 ддоично-десятичного кода в напряжение присоединен к первому входу блока 6 суммирования напряжений, выход которого подключен к второму входу блока 5 сравнения, к первому входу которог подключены входная шина. Ко второму входу блока б суммирования присоединен выход генератора 7 линейного напряжения, к первому и второму входам которого присоединены соответственно первые выходы первой и (rt -3) -и пар выходов логического блока. В исходном состоянии в регистре 3 двоично-десятичного кода зафиксированы нулевые значения во всех разрядах, компенсирующее напряжение Цц на выходе преобразователя 4двоично-десятичного кода в напряжение равно нулю. Формирование, двоично-десятичного кода в предлагаемом преобразователе осуществляется в два этапа. На первом этапе имеется кодовый эквивалент входного напряжения, на втором осуществляется преобразование найденного кода в двоично-десятичный. На первом этапе выполняется It так тов по числу двоичных разрядов регистра 3 двоично-десятичного кода. Каждый такт выполняется по очеред-г - ному сигналу с тактового генератора.1 , Действия на каждом такте однотипн В начале каждого i -го такта появляется сигнал на первом выходе i -и па ры выходов логического блока 2, который поступает на вход установки ед ницы в i -м разряде регистра 3 двоич но-десятичного кода. Сформированное на выходе преобразователя 4 двоичнодесятичного кода в напряжение компен сирующее напряжение УК через блок б суммирования напряжений поступает на вход блока 5 сравнения и сравнивается с текущим значением входного напряжения и . Еслиик и)с / то вконце текущего такта появляется сигнал на втором выходе -i; -и пары выходов логил ческого блока 2 и устанавливает нулевое значение в -м разряде регистра 3 двоично-десятичного кода. Кроме того, по сигналу с первого выхода первой пары вькодов логического блока 2 генератор 7 линейного напряжения начинает формировать на своем выходе линейно убывающее напряжение одного знака с компенсирующим напряжением на выходе U к . Напряжение, с выхода генератора 7 линейного напряжения достигает нулевого значения по по- . ступлении на второй вход генератора 7 сигнала с первого выхода {п-3)-й пары выходов логического блока. Генератор 7 линейного напряжения предназначен для формирования смещения « {JK имеющегося на выходе преобразова.теля двоично-десятичного кода, с т.ем, чтобы общая динамическая погрешность напряжения UK, поступгиощего на сравнение в блек 5 сравнения напряжений в процессе определения всех старших разрядов регистра кода, кроме чeтыpek младших разрядов, была бы всегда одного знака, что обеспечивается суммированием напряжений с, выходов преобразователя 4 двоично-десятичного кода в напряжениеи генератора 7 линейного напряжения и использованием суммарного напряжения общего компенсирующего напряжения, подаваемого на второй вход блока 5 сравнения напряжений. На втором этапе, по сигналу с второго выхода последней пары выходов логического блока осуществляется передача кода из регистра 3 в преобразователь 8 кода и преобразование его в двоично-десятичный код системы 8,4,2,1., Таким образом, по сравнению с базовым объектом, в качестве которого принят прототип, предлагаемый преобразователь обладает большим быстродействием. Кроме того, использование смещения компенсирующего сигнала и избыточности кода 8, 4, 2, 1 позволяет в значительной степени устранить влияние динамической погрешности на точность нахождения кодового эквивалента входного преобразуемого напряжения, в результате -снижается необходимая длительность тактов уравновешивания старших разрядов, что, в свою очередь, при аналогичной точнос5ти дает возможность более чем в . два раза повысить скорость преобразования напряжения в код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU881730A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1977 |

|

SU732853A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

УГЛ

Uf

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых / вычислительных устройств | |||

| М., Энергия, 1975, с | |||

| Переставная шейка для вала | 1921 |

|

SU309A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шляндин В.М | |||

| Цифровые измерительные преобразователи и приборы | |||

| Высшая школа, 1973, с | |||

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

Авторы

Даты

1984-02-07—Публикация

1982-04-07—Подача