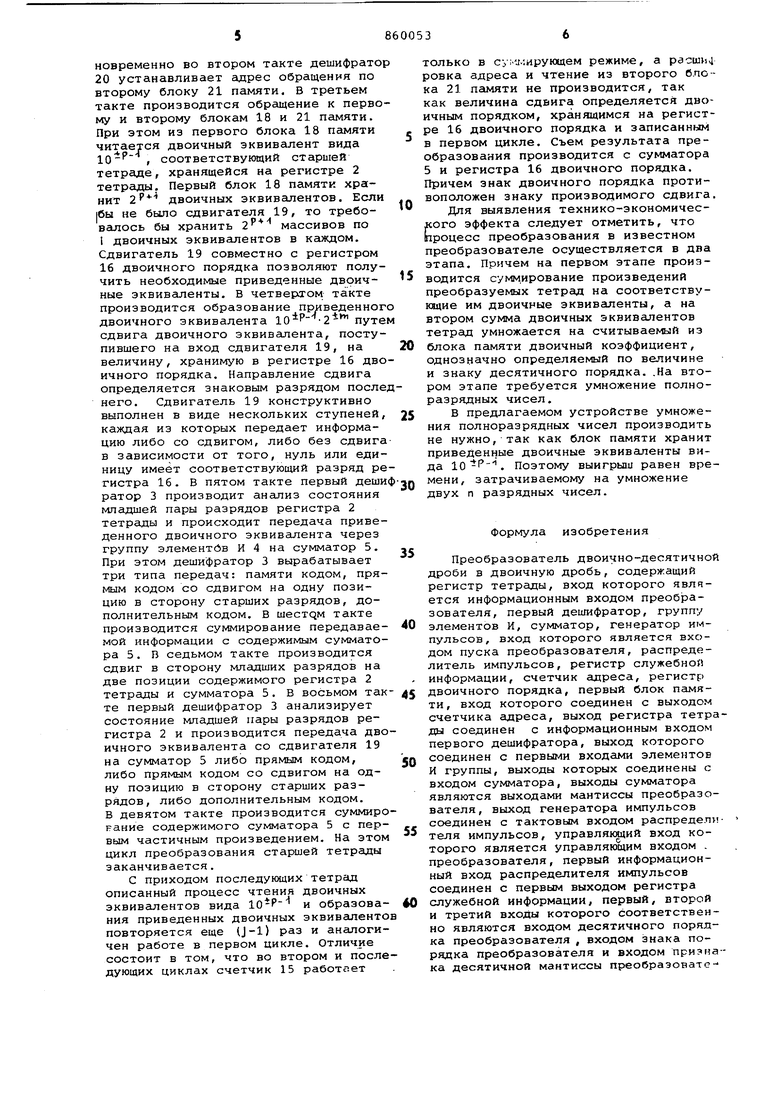

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей. Известен преобразователь двоичнодесятичной дроби в двоичную дробь, содержащий регистр тетрады, регистр старших разрядов, дешифратор, группу элементов И, сумматор, генератор, формирователь, регистр служебной информации, счетчик адреса, регистр двоичного порядка, блок памяти. Преобразование в данном устройстве основано на суммировании двоичных коэффициентов тетрад с последующим у;множени ем на двоичный коэффициент, оДнозначно определяемый по десятичному порядку 1. Недостаток этого преобразователя состоит в относительно низком быстродействииНаиболее близким к предлагаемому по технической сущности является пре образователь двоично-десятичной дроби в двоичную дробь, содержащий регистр тетрады, вход которого является инфор мационньлм входом преобразователя, пер вый дешифратор, группу элементов И, сумматор, генератор импульсов, вход которого является входом пуска преобразователя, распределитель импульсов, регистр служебной информации, счетчик адреса, регистр двоичного порядка, первый блок памяти, вход, которого соединен с выходом счетчика адреса, выход регистра тетрады соединен с информационным входом первого дешифратора, выход которого соединен с первыми входами элементов И группы, выходы которых соединены с входом сумматора, выходы сумматора являются выходами мантиссы преобразователя, выход генератора импульсов соединен с тактовым входом распределителя импульсов, управляющий вход которого является управляющим входом преобразователя, первый информационный вход распределителя импульсов соединен с первым выходом регистра служебной информации, первый, второй и третий входы которого соответственно являются входом десятичного порядка преобразователя, входом знака порядка преобразователя и входом признака десятичной мантиссы преобразователя, второй выход регистра служебной информации соединен со вторым информащионным входом распределителя импульсов и первым входом счетчика адреса, второй вход которого соединен с третьим выходом ре1-истра служебной информации и третьим информационным входом распределителя импульсов, первый, второй, третий и четвертый выходы которого соединены соответственно с тактовыми входами регистра тетрещы, первого дешифратора, cviviMaTopa и счётчика адреса, первый выход регистра двоичного порядка является выходом порядка преобразователя 2, Недостаток известного преобразователя.также состоит в относительно низком быстродействии, -связанном с необходимостью умножения полноразряд ных чисел. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем что 3 преобразователь двоично-десятичной дроби в двоичную дробь дополнительно введены сдвигатель, второй дешифратор, второй блок памяти, вход которого соединен с выходом второго дешифратора, а выход соединен с входом регистра двоичног о порядка, второй выход которого соединен с управляющими входами сдвигателя, информационный вход которого соединен с выходом, первого блока памяти, выход сдвигателя соединен со вторыми входа ми элементов И группы, а первый, второй и третий входы второго дешифратора соединены соответственно с пя тым выходом распределителя импульсов вторым и третьим выходами регистра служебной информации. Кроме того, в преобразователе счетчик адреса выполнен реверсивным. На чертеже представлена блок-схема предлагаемого преобразователя. Схема включает информационный вход 1, регистр 2 тетрады, первый де шифратор 3, группу элементов И 4, су матор 5, выходы 6 мантиссы преобразо вателя, вход 7 пуска преобразователя генератор 8 импульсов, распределитель 9 импульсов, управляющий вход 10 преобразователя, вход 11 десятичного порядка преобразователя, вход 12 знака порядка преобразователя, вход 13 признака десятичной мантиссы преобразователя, регистр 14 служебной информации, реверсивный счетчик 15 сщреса, регистр 16 двоичного порядка, выход 17 порядка преобразователя, первый блок 18 памяти, сдвигатель 19, второй дешифратор 20, второй блок 21 памяти. Управляющий вход 10 служит для по дачи управляющего сигнала с устройства ввода (не показан). Первый выход распределителя 9 импульсов соеди нен с выходом регистра 2 тетрады для сдвига его содержимого на две позиций в сторону младших разрядов. Второй и третий выходы распределителя 9 импульсов соответственно соединены с вторым входом перврго дешифратора и входом сумматора 5 для подачи сигн ла анализа и сдвига содержимого сумматора 5 на две позиции в сторону младших разрядов. Выход первого блока 18 памяти соединен с первым входом сдвигателя 19 для подачи двоичного эквивалента вида 10 . Выход второго дешифратора 20 соединен с входом второго блока 21 памяти, хранящего двоичные порядки. Выход сдвигателя |19 соединен с вторым входом элементов И 4 группы для передачи призеден.ного двоичного эквивалента вида 2 Преобразование осуществляется в соответствии со следуюи-им соотношениемА --ST,),, С) i--i где А - двоичная мантисса; m - двоичный порядок; i - номер десятичного разряда) Т - тетрада десятичного числа; Р - десятичный порядок , (0 ) 2 приведенный двоичный экви валент. Преобразование двоично-десятичного числа основано на суммировании произведений десятичных тетрад на приведенный двоичный эквивалент и присвоении результату необходимого двоичного порядка. Причем приведенный двоичный эквивалент (10-1,-2 получается из двоичного эквивалента , хранимого в первом блоке 18 памяти, путем сдвига на 2. Соотношение (1) реализуется в следующей последовательности. По входу 7 поступает сигнал Пуск на генератор В импульсов, который вырабатывает серию импульсов. Эта серия поступает на распределитель 9 импульсов. Затем на регистр 14 служебной информации поочередно поступают знак десятичного порядка, десятичный порядок и признак десятичной мантиссы по входам 11-13. После этого по входу 1 на регистр 2 тетрады поступает старшая тетрада преобразуемого двоично-десятичного числа. Одновременно по входу 10 поступает управляющий сигнал, который запускает распределитель 9, обеспечивающий нормальное функционирование всего преобразователя в целом. В первом такте счетчик 15 устанавливает некоторый адрес, который определяется величиной и знаком десятичного порядка. Во втором такте он изменяет свое состояние на единицу (отрицательную при , положительную при ), устанавливая тем самым истинный адрес обращения к блоку 18 памяти. Счетчик 15 гщреса выполнен реверсивным, т.е. работает в двух режимах: режиме вычитания и суммирования импульсов. При этом во втором такте первого цикла он работает в режиме вычитания импульсов, во Всех последующих циклах в режиме суммирования импульсов. Одновременно во втором такте дешифрато 20 устанавливает адрес обращения по второму блоку 21 памяти. В третьем такте производится обраидение к первому и второму блокам 18 и 21 памяти. При этом из первого блока 18 памяти читается двоичный эквивалент вида , соответствующий старшей тетраде, хранящейся на регистре 2 тетрады. Первый блок 18 памяти хранит двоичных эквивалентов. Если |бы не было сдвигателя 19, то требовалось бы хранить массивов по 1 двоичных эквивсшентов в каждом. Сдвигатель 19 совместно с регистром 16 двоичного порядка позволяют получить необходимые приведенные двоичные эквиваленты. В четвертом такте производится образование приведенног двоичного эквивалента 10 2 путе сдвига двоичного эквивалента, поступившего на вход сдвигателя 19, на величину, хранимую в регистре 16 двоичного порядка. Направление сдвига определяется знаковым разрядом после него. Сдвигатель 19 конструктивно выполнен в виде нескольких ступеней, каждая из которых передает информацию либо со сдвигом, либо без сдвигав зависимости от того, нуль или единицу имеет соответствующий разряд регистра 16. В пятом такте первый деши ратор 3 производит анализ состояния млсщшей пары разрядов регистра 2 тетрады и происходит передача приведенного двоичного эквивсшента через группу элементс5в И 4 на сумматор 5. При этом дешифратор 3 вырабатывает три типа передач: памяти кодом, прямым кодом со сдвигом на одну позицию в сторону старших разрядов, дополнительным кодом. В mecTQM такте производится суммирование передаваемой информации с содержимым сумматора 5 . В седьмом такте производится сдвиг в сторону младших разрядов на две позиции содержимого регистра 2 тетрады и сумматора 5. Б восьмом такте первый дешифратор 3 анализирует состояние младшей пары разрядов регистра 2 и производится передача двоичного эквивалента со сдвигателя 19 на сумматор 5 либо прямым кодом, либо прямым кодом со сдвигом на одну позицию в сторону старших разрядов, либо дополнительным кодом. В девятом такте производится суммироЕание содержимого сумматора 5 с первым частичным произведением. На этом цикл преобразования старшей тетрады заканчивается.

С приходом последующих тетрад описанный процесс чтения двоичных эквивалентов вида и образования приведенных двоичных эквиваленто повторяется еще IJ-1) раз и аналогичен работе в первом цикле. Отличие состоит в том, что во втором и последующих циклах счетчик 15 работает

только в сум1.:ирующем режиме, а расш1)4 ровка адреса и чтение из второго блока 21 Пс1мяти не производится, так как величина сдвига определяется двоичным порядком, хранящимся на регистре 16 двоичного порядка и записанным в первом цикле. Съем результата преобразования производится с сумматора 5 и регистра 16 двоичного порядка. Причем знак двоичного порядка противоположен знаку производимого сдвига.

0

Для выявления технико-экономического эффекта следует отметить, что процесс преобразования в известном преобразователе осуществляется в два этапа. Причем на первом этапе произ5водится суммирование произведений преобразуемых тетрад на соответствующие им двоичные эквиваленты, а на втором сумма двоичных эквивалентов тетрад умножается на считываемый из

0 блока памяти двоичный коэффициент, однозначно определяемый по величине и знаку десятичного порядка. .На втором этапе требуется умножение полноразрядных чисел.

В предлагаемом устройстве умноже5ния полноразрядных чисел производить не нужно, так как блок памяти хранит приведенные двоичные эквиваленты вида . Поэтому выигрыш равен времени, затрачиваемому на умножение

0 двух п разрядных чисел.

Формула изобретения

5

Преобразователь двоично-десятичной дроби в двоичную дробь, содержащий регистр тетрады, вход которого является информационным входом преобразователя, первый дешифратор, группу

0 элементов И, сумматор, генератор импульсов, вход которого является входом пуска преобразователя, распределитель импульсов, регистр служебной информации, счетчик адреса, регистр двоичного порядка, первый блок памя5ти , вход которого соединен с выходом счетчика адреса, выход регистра тетрады соединен с информационным входом первого дешифратора, выход которого соединен с первыми входами элементов

0 И группы, выходы которых соединены с входом сумматора, выходы сумматора являются выходами мантиссы преобразователя, выход генератора импульсов соединен с тактовым входом распредели5теля импульсов, управляющий вход которого является управлякщим входом . преобразователя, первый информационный вход распределителя импульсов соединен с первым выходом регистра служебной информации, первый, второй

О и третий входы которого соответственно являются входом десятичного порядка преобразователя , входом знака порядка преобразователя и входом признака десятичной мантиссы преобразоватс-ЛЯ , второй выход регистра служебной информации соединен со вторым информационным входом распределителя импульсов и первым входом счетчика адреса, второй вход которого соединен с третьим выходом регистра служебной информации и третьим информационным входом распределителя импульсов, первый , второй , третий и четвертый выходы которого соединены соответственно с тактовыми входами регистра тетрады, первого дешифратора, сумматора (и счетчика адреса, первый выход регистра двоичного порядка является выходом порядка преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введены сдвигатель , второй дешифратор , второй блок памяти, вход которого соединен с выходом второго дешифратора , а выход соединен с входом регистра двоичного порядка, второй выход которого соединен с управляющими входами сдвигателя, информационный вход которого соединен с выxo oм блока памяти, выход сдвигателя соединен со вторыми входами элементов И группы, а первый, второй-и третий 5 входы второго дешифратора соединены соответственно с пятым выходом распределителя импульсов, вторым и третьим выходами регистра служебной информации.

0 2. Преобразователь по п. 1, отличающийся тем, что в нем счетчик адреса выполнен реверсивным.

Источники информации , принятые во внимание при экспертизе

5 Авторское свидетельство СССР по заявке 2649587/24, кл. G06 F 5/02, 1975.

2. Авторское свидетельство СССР по за-чвке № 2818807/24, кл. G06 F 5/02, 20.08.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

t1

П

It

л

Z1

19

Авторы

Даты

1981-08-30—Публикация

1979-09-07—Подача