1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении преобразователей в системах сбора обработки и передачи информации с переменной разрядностью двоичного слова.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий блок хранения эквивалентов, формирователь веса поразрядных цифр десятичного эквивалента, генератор тактовых импульсов, распределитель, поразрядные дешифраторы и счетчики 1.

Недостаток известного преобразователя состоит в относительно низком быстродействии и в зависимости его схемы от числа разрядов входного кода.

Наиболее близким решением данной задачи по технической сушности и схемному построению является преобразователь двоичного кода в двоично-десятичный, содержащий первый, второй и третий сумматоры, первый и второй блоки коррекции 2.

Недостаток данного преобразователя состонт в большом количестве аппаратуры.

Цель изобретения - упрощение преобразователя.

Поставленная цель достнгается тем, что преобразователь двоичного кода в двоично-десятичный, содержащий первый, второй и третий сумматоры, первый и второй блоки коррекции, входы которых соединены с выходами старипос разрядов первого и второго сумматоров соответственно, выход переноса первого сз матора соединен с входом переноса

10 первого блока коррекции, содержит блок хранения эквивалентов, регистр результата и генератор тактов, выходы которого соединены с тактовыми входами регистра результата и блока хранения эквивалентов, входы кото15рого являются входами преобразователя, а выходы блока хранения эквивалентов соединены с первой группой входов первого сумматора, вторая группа входов которого соединена с первой группой выходов регистра результата,

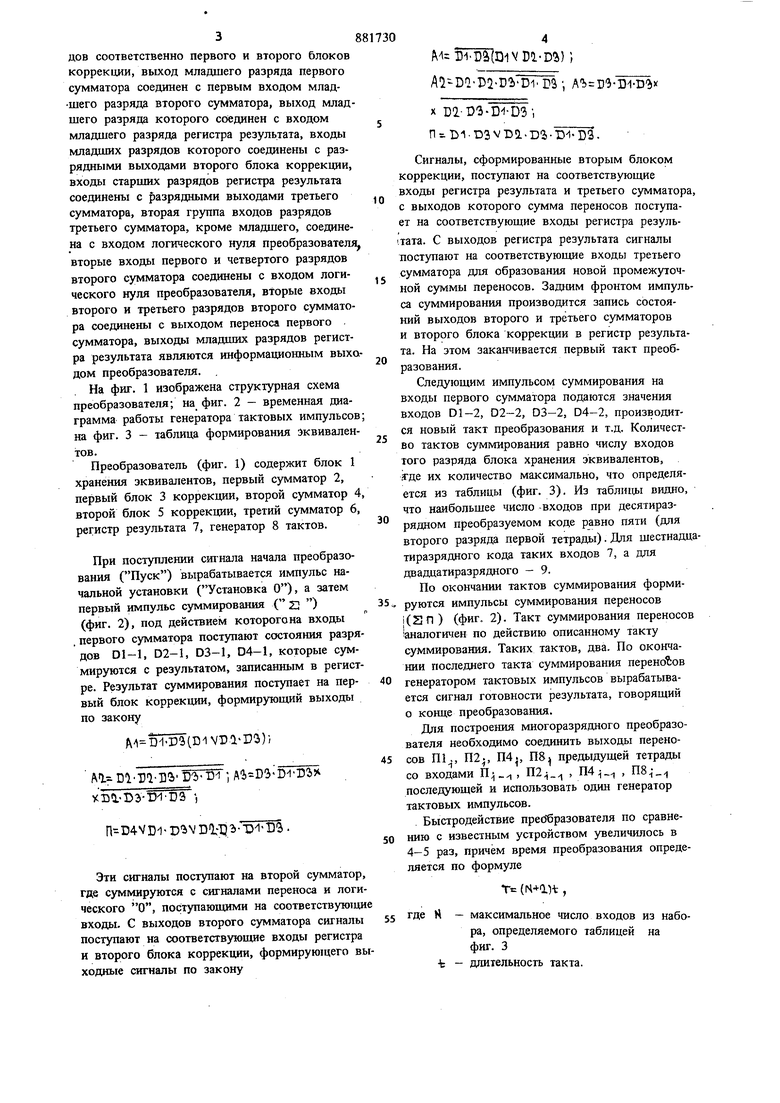

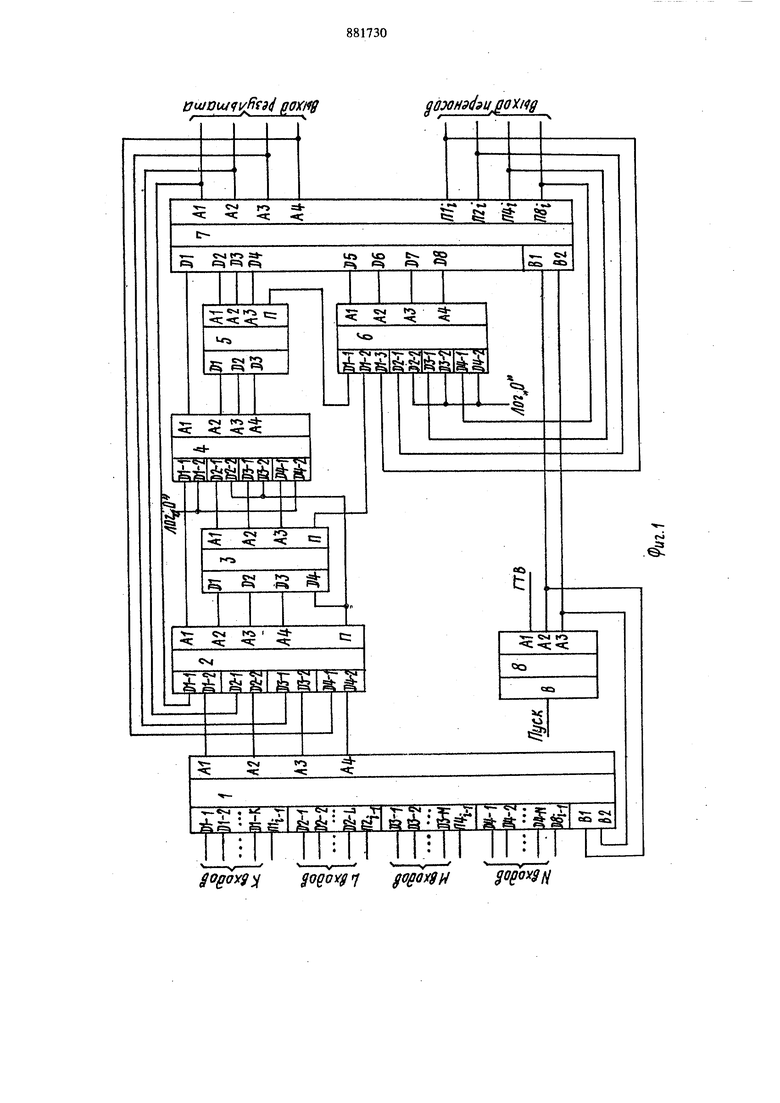

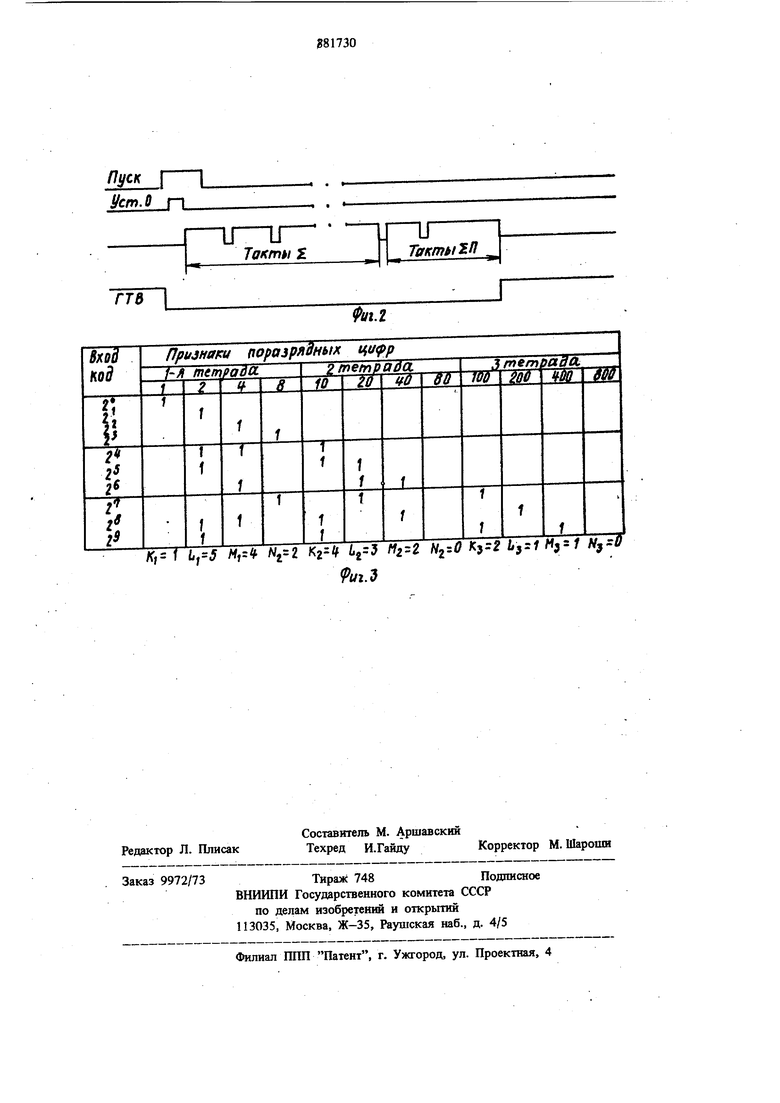

20 вторая группа выходов которого соединена с первой группой входов третьего сумматора,первый и второй входы младшего разряда которого соединены с выходами старших разря3дов соответственно первого и второго блоков коррекции, выход младшего разряда первого сумматора соединен с первым входом младшего разряда второго сумматора, выход младшего разряда которого соединен с входом младшего разряда регистра результата, входы младших разрядов которого соединены с разрядными выходами второго блока коррекции, входы старших разрядов регистра результата соединены с разрядными выходами третьего сумматора, вторая rpjmna входов разрядов третьего сумматора, кроме младшего, соединена с входом логического нуля преобразователя вторые входы первого и четвертого разрядов второго сумматора соединены с входом логического нуля преобразователя, вторые входы второго и третьего разрядов второго сумматора соединены с выходом переноса первого сумматора, выходы младших разрядов регистра результата являются информационным выхо дом преобразователя. На фиг. 1 изображена структурная схема преобразователя; на фиг. 2 - временная диаграмма работы генератора тактовых импульсов на фиг. 3 - таблица формирования Эквивалентов. Преобразователь (фиг. 1) содержит блок 1 хранения эквивалентов, первый сумматор 2, первый блок 3 коррекции, второй сумматор 4 второй блок 5 коррекции, третий сумматор 6, регистр результата 7, генератор 8 тактов. При поступлении сшнала начала преобразования (Пуск) вырабатывается импульс начальной установки (Установка О), а затем первый импульс суммирования ( д ) (фиг. 2), под действием которого на входы первого сумматора поступают состояния разря дов D1-1, D2-1, D3-1, 04-1, которые суммируются с результатом, записанным в регистре. Результат суммирования поступает на первый блок коррекции, формирующий выходы по закону А 31Г)3(С1У111БЗ)-; IVI Dl-pl-UU l)l-t 3-D1D3 n D4VD1-I)bVDl-I31 -D1D Эти сигналы поступают на второй сумматор, где суммируются с сигналами переноса и логи ческого О, поступающими на соответствую1ци входы. С выходов второго сумматора сигналы поступают на соответствующие входы регистра и второго блока коррекции, формирующего вы ходные сигналы по закону M 5 DalDlVDl-Di) ; AlD1D2I), АЪгПЗ- ФВ х X са-оз-оч-оз; П . В1 D3 V DO.. Сигналы, сформированные вторым блоком коррекции, поступают на соответствующие входы регистра результата и третьего сумматора, с выходов которого сумма переносов поступает на соответствующие входы регистра результата. С выходов регистра результата сигналы поступают на соответствующие входы третьего сумматора для образования новой промежуточной суммы переносов. Задним фронтом импульса суммирования производится запись состояний выходов второго и третьего сумматоров и второго блока коррекции в регистр результата. На этом заканчивается первый такт преобразования. Следующим импульсом суммирования на входы первого сумматора подаются значения входов D1-2, 02-2, D3-2, 04-2, производится новый такт преобразования и т.д. Количество тактов суммирования равно числу входов того разряда блока хранения эквивалентов, где их количество максимально, что определяется из таблицы (фиг. 3). Из таблицы видно, что наибольшее число -входов при десятиразрядном преобразуемом коде равно пяти (для второго разряда первой тетрады). Для шестнадцатиразрядного кода таких входов 7, а для двадцатиразрядного - 9. По окончании тактов суммирования формируются импульсы суммирования переносов i(Sn) (фиг. 2). Такт суммирования переносов аналогичен по действию описанному такту суммирования. Таких тактов, два. По окончании последнего такта суммирования переносов генератором тактовых импульсов вырабатывается сигнал готовности результата, говорящий о конце преобразования. Для построения многоразрядного преобразователя необходимо соединить выходы переносов П1., П2, П4., П8;| предыдущей тетрады со входами П jj ., , П2 , П4 , П8 - ,, последующей и использовать один генератор тактовых импульсов. . Быстродействие преббразователя по сравнению с известным устройством увеличилось в 4-5 раз, причём время преобразования определяется по формуле т (, где Ц - максимальное число входов из набора, определяемого таблицей на фиг. 3 fc - длительность такта. 588 Формула изобретения Преобразователь двоичного кода в двоичнодесятичный, содержащий первый, второй и третий сумматоры, первый и второй блоки коррекции, входы которых соединены с выходами старших разрядов первого и второго сумматоров соответственно, выход переноса первого сумматора соединен с входом переноса первого блока коррекции, отличающийся тем, что, с целью упрощения преобразователя, он содержит блок хранения эквивалентов, регистр результата и генератор тактов, выходы которого соединены с тактовыми входами регистра результата и блока .хранения эквивалентов, входы которого являются входамн преобр зователя, а выходы блока хранения эквивалентов соединены с первой группой входов первого сумматора, вторая группа входов кото рого соединена с первой группой выходов регистра результата, вторая группа выходов которого соединена с первой группой входов третьего сумматора, первый и второй входы младшего разряда которого соединены с выходами старших разрядов соответственно первого и второго блоков коррекции, выход младщего разряда первого сумматора соединен с первым входом младшего разряда второго сумматора, выход младшего разряда которого соеяинен с входом младшего разряда регистра результата, входы младших разрядов которого соединены с разрядными выходами второго блока коррекции, входы старших разрядов регистра результата соединены с разрядными выходами третьего сумматора, вторая группа входов разрядов третьего сумматора, кроме младшего, соединена с входом логического нуля преобразователя, вторые входы первого и четвертого разрядов второго ; сумматора соединены с входом логического нуля преобразователя, вторые входы второго и третьего разрядов второго сумматора соединены с выходом переноса первого сумматора, выходы младших разрядов регистра результата являются информационным выходом преобразователя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N- 513492, кл. Н 03 К 13/24, 1974. 2.Патент США № 3614403, кл. 235-155, опублик. 1971 (прототип). Uu/oufqi fsd po)fi

§ogoyg jogoygi gogojfgn oxHsdsu o iig

Пуск Уст, в п

Такти S.

ГТд L

JJ,

Тактики

Фаг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283978A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

К, f L,5 W, «г.З

Авторы

Даты

1981-11-15—Публикация

1980-01-15—Подача