Изобретение относится к вычислительной технике, предназначено для .умножения двоично-десятичных цифр, представленных кодом , и прибавления десятичного переноса и может быть применено в быстродействующих вычислителях.

Известно устройство умножения,сдержащее регистр множимого, регис-д множителя, блок последовательного накопления чисел, кратных множимому, блок суммирования частичных призведений, блок определения очередности цифр ij .

Однако данное устройство отличается низким быстродействием.

Наиболее близким к предлагаемому по технической сущности являетс устройство умножения двоично-десятичных цифр, содержащее блок кодопреобразователей, сумматор, матриц элементов И размерности л m (п т 4 - количество строк и столбцов), причем первый и второй входы 4,j -го элемента И (i 1,4) марицы соединены соответственно с i разрядом множимого и с j -м разрядом множителя устройства, выходы элементов И р -и диагонали матрицы (р 1,3) подключены к входам р-го разряда сумматора, выходы разрядов которого соединены с младшими разрядными входами соответствующих весов блока кодопреобразователей, разрядныевходы переносов сумматор соединены с соответствующими входами переносов устройства, разрядные выходы блока кодопреобразователей являются выходами устройства pQ .

Недостатком известного устройства является сложность блока сумматоров .

Целью изобретения является снижение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство умножения двоично-десятичных цифр, содержащее блок кодопреобразователей, сумматор, матрицу элементов И размерности n-m (п т 4 - количество строк и столбцов), причем первый и второй входы i I -го элемента И (м . 1,4) матрицы соединены соответственно g i -м разрядом множимого и с j -м разрядом множителя устройства, выходы элементов И диагонали матрицы ( р Г,3) подключены к входам р-го разряда сумматора, выходы разрядов которого соединены с млада1ими разрядными входами ссГответствующих весов блока кодопреобразователей, разрядные входы переносов сумматоров соединены с соответствующими входами переносов устройства, раз,рядные выходы блока кодопреобразователей являются выходами устройства, введены элемент ИЛИ и блок элементов ИЛИ, содержащий первый, второй, третий и четвертый элементы ИЛИ, причем выход элемента И седьмой диагонали матрицы соединен с первым входом элемента ИЛИ,второй вход которого соединен с выходом переноса сумматора, выход элемента ИЛИ соединен со старшим разрядным входом блока кодопреобразователей, выходы элементов И четвертой диагонали матрицы подключены соответственно к входам первого и второго элементов ИЛИ блока, йыходы элементов И пятой к шестой диагонали матрицы подключи чн соответственно к входам третьего и четвертого элементов ИЛИ блока, выходы первого и второго элементов ИЛ блока подключены к входам четвертого разряда сумматора, выходы третьего и четвертого элементов HJiH блока подключены соответственно к входа.- ..Hforo и ujecToro разрядов сумма йра,

CHHKei-iiG- аппаратурных затрат в данном устройстве достигается посредством учета избыточности двоичного представления десятичных цифр

При использовании кода 8-4-2-1 запрещенными (избЕлточньлми) комбинациями npL-i представлении десятичных цифр являются значения 1010-1111, удовлетворяющие словиям

8 4

(1 g. Х 1, значение бита с весом 2

где Xg двоично--десятичной цифры сомножителя.

Это обстоятельство позволяет сократить количество одноразрядных сумматоров, составляющих сумматор,с двенадцати до семи. Вместо одноразрядных сумматоров могут быть использованы обычные элементы ИЛИ,что вызывает упрощение сумматора.

На фиг.1 представлена структурна схема устройства; на фиг.2 - матриц элементов Н на фиг.З - схема блока элементов ИЛИ; на фиг.4 - схема сумматора; на фиг.З - схема блока ко допреобразователей.

Устройство содержит матрицу 1 элементов И, сумматор 2, блок 3 кодопреобразователей, блок 4 элементов ИЛИ, входы 5 множимого устройства, входы б множителя устройства, входы 7 переносов устройства, выходы 8 устройства.

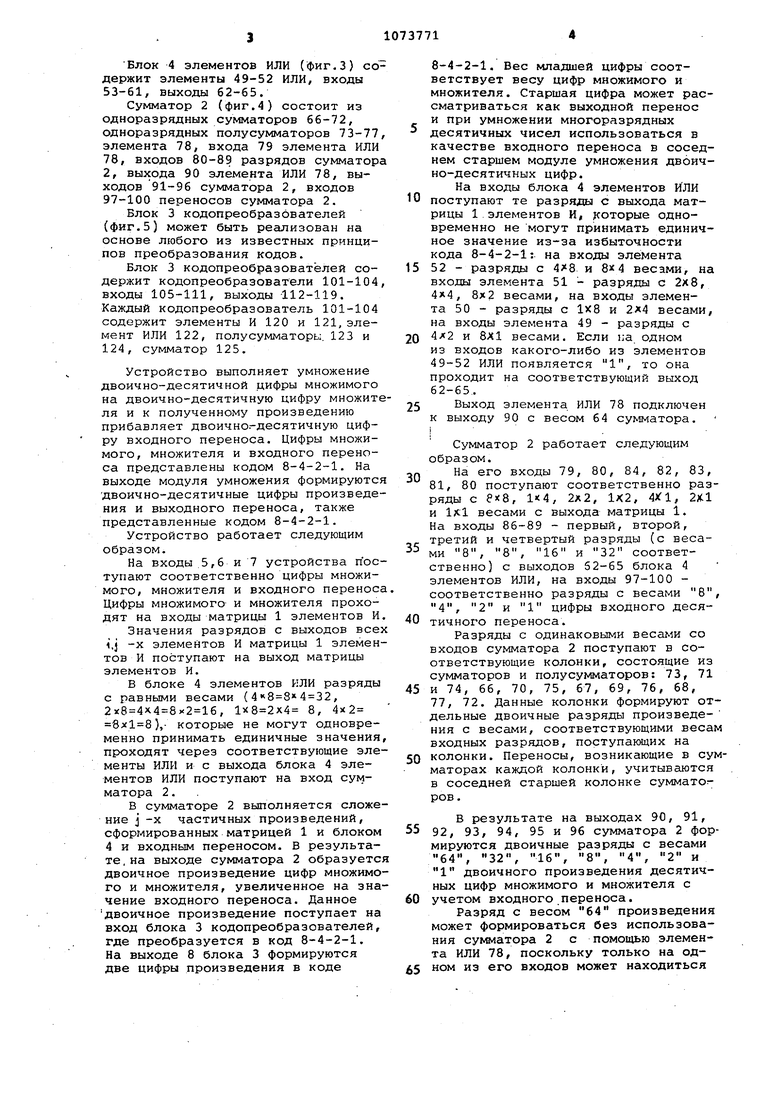

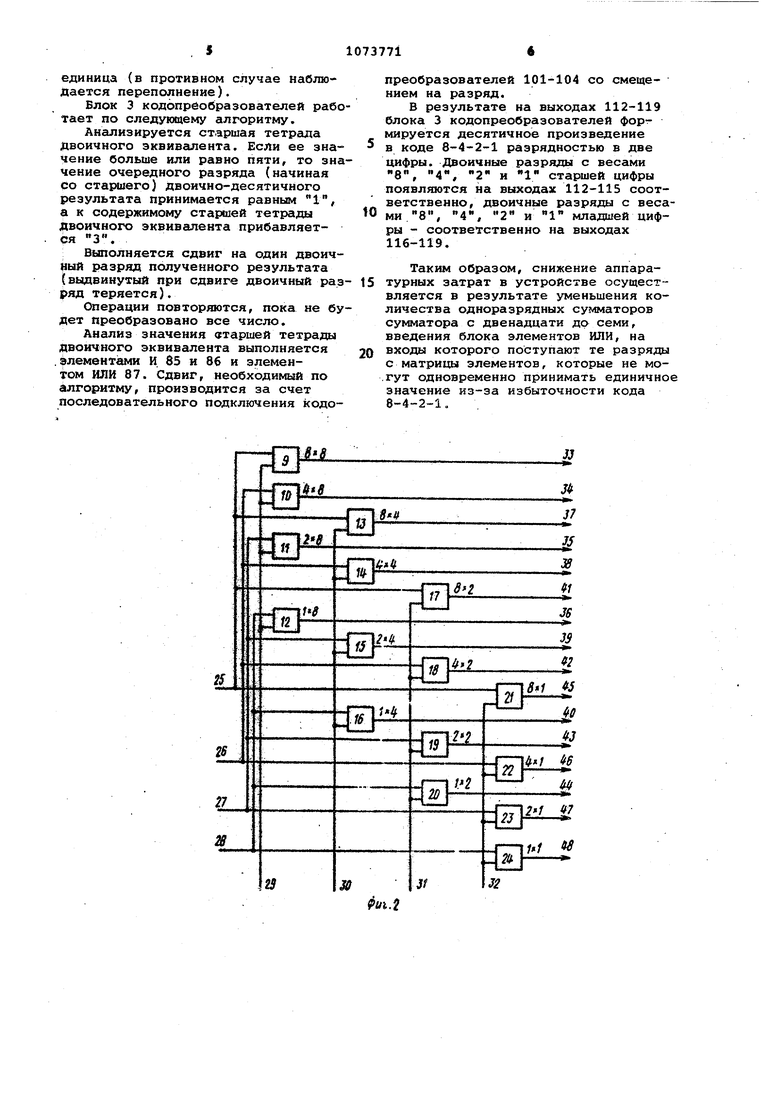

Матрица 1 элементов И (фиг.2) со держит элементы 9-24 И с соответствующими весами, входы 25-28 разрядов множимого устройства, входы 29-32 множителя устройства, выходы 33-48 1 элементов И.

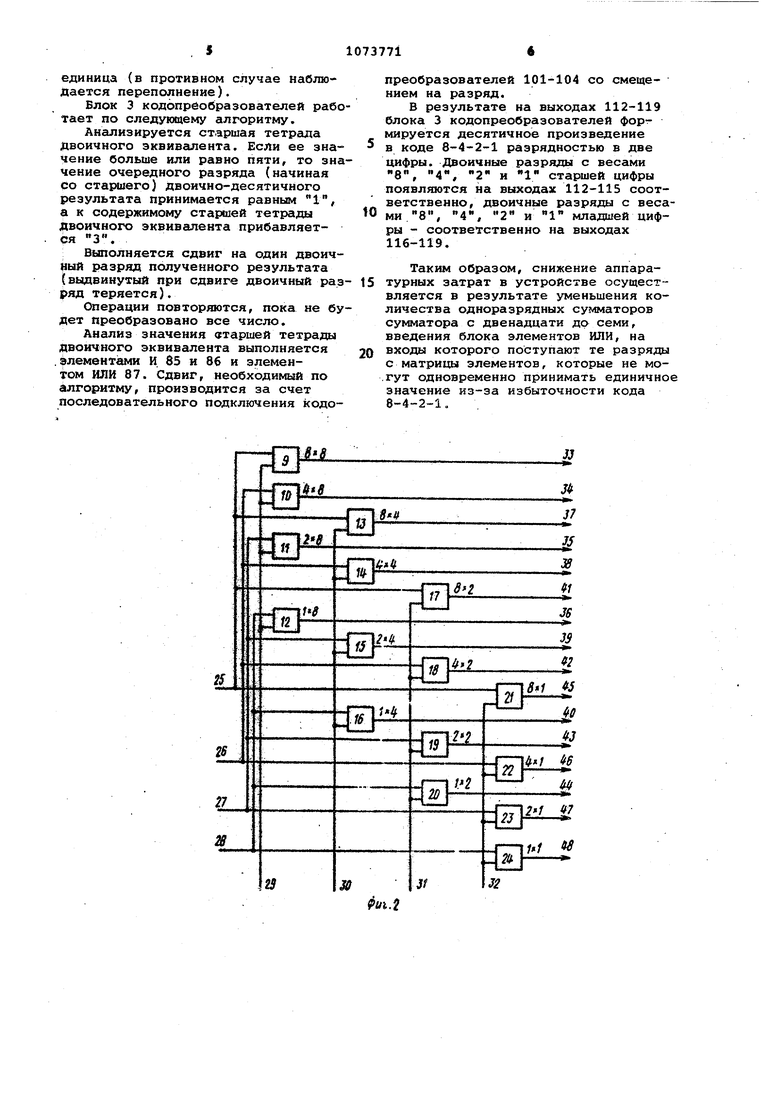

Блок 4 элементов ИЛИ (фиг.З) содержит элементы 49-52 ИЛИ, входы 53-61, выходы 62-65.

Сумматор 2 (фиг.4} состоит иэ одноразрядных сумматоров 66-72, одноразрядных полусумматоров 73-77, элемента 78, входа 79 элемента ИЛИ 78, входов 80-89 разрядов сумматора 2, выхода 90 элемента ИЛИ 78, выходов 91-96 сумматора 2, входов 97-100 переносов сумматора 2.

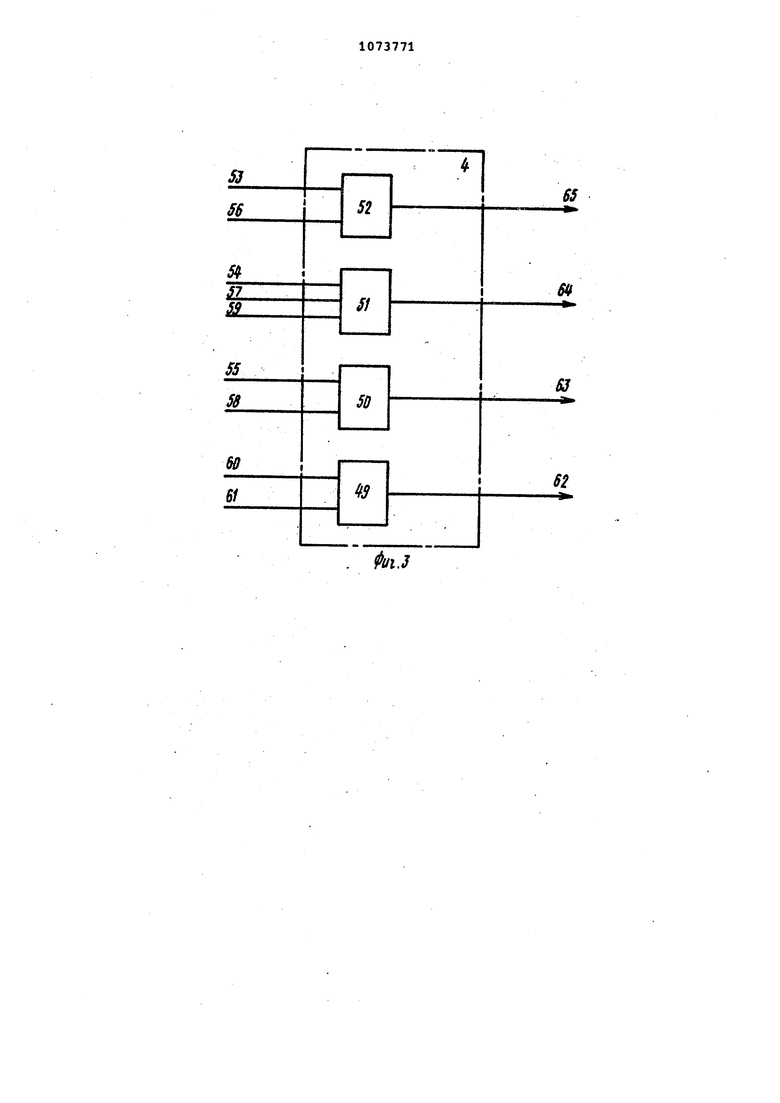

Блок 3 кодопреобразователей (фиг.5) может быть реализован на основе любого из известных принципов преобразования кодов.

Блок 3 кодопреобразователей содержит кодопреобразователи 101-104, входы 105-111, выходы 112-119. Каждый кодопреобразователь 101-104 содержит элементы И 120 и 121,элемент ИЛИ 122, полусумматоры. 123 и 124, сумматор 125.

Устройство выполняет умножение двоично-десятичной цифры множимого на двоично-десятичную цифру множителя и к полученному произведению прибавляет двоично-десятичную цифру входного переноса. Цифры множимого, множителя и входного переноса представлены кодом 8-4-2-1. На выходе модуля умножения формируются двоично-десятичные цифры произведения и выходного переноса, также представленные кодом 8-4-2-1.

Устройство работает следующим образом.

На входы 5,6 и 7 устройства поступают соответственно цифры множимого, множителя и входного переноса Цифры множимого и множителя проходят на входы матрицы 1 элементов И.

Значения разрядов с выходов всех i.j -X элементов И матрицы 1 элементов И поступают на выход матрицы элементов И.

В блоке 4 элементов ИЛИ разряды с равными весами (, , 8, 4x2 ),- которые не могут одновременно принимать единичные значения, проходят через соответствующие элементы ИЛИ и с выхода блока 4 элементов ИЛИ поступают на вход сумматора 2.

В сумматоре 2 выполняется сложение j -X частичных произведений, сформированных матрицей 1 и блоком 4 и входным переносом. В результате, на выходе сумматора 2 образуется двоичное произведение цифр множимого и множителя, увеличенное на значение входного переноса. Данное двоичное произведение поступает на вход блока 3 кодопреобразователей, где преобразуется в код 8-4-2-1. На выходе 8 блока 3 формируются две цифры произведения в коде

8-4-2-1. Вес младшей цифры соответствует весу цифр множимого и множителя. Старшая цифра может рассматриваться как выходной перенос и при умножении многоразрядных десятичных чисел использоваться в качестве входного переноса в соседнем старшем модуле умножения двоично-десятичных цифр.

На входы блока 4 элементов ИЛИ

0 поступают те разряда с выхода матрицы 1 элементов И, которые одновременно не могут принимать единичное значение из-за избыточности кода 8-4-2-1: на входы элемента

5 52 - разряды с 4X8 и 8 4 весами, на входы элемента 51 - разряды с 2x8, 4x4, 8x2 весами, на входы элемента 50 - разряды с 1X8 и 2X4 весами, на входы элемента 49 - разряды с 4x2 и 8x1 весами. Если i;a одном

0 из входов какого-либо из элементов 49-52 ИЛИ появляется 1, то она проходит на соответствующий выход 62-65.

Выход элемента ИЛИ 78 подключен

5 к выходу 90 с весом 64 сумматора. I

Сумматор 2 работает следующим образом.

На его входы 79, 80, 84, 82, 83,

0 81, 80 поступают соответственно разряды с ек8, К 4, 2X2, 1X2, 4J 1, 2Ц.1 и 1x1 весами с выхода матрицы 1. На входы 86-89 - первый, второй, третий и четвертый разряды (с веса5ми 8, 8, 16 и 32 соответственно) с выходов 52-65 блока 4 элементов ИЛИ, на входы 97-100 соответственно разряды с весами 8, 4, 2 и 1 цифры входного деся0тичного переноса.

Разряды с одинаковыми весами со входов сумматора 2 поступают в соответствующие колонки, состоящие из сумматоров и полусумматоров: 73, 71 и 74, 66, 70, 75, 67, 69, 76, 68,

5 77, 72. Данные колонки формируют отдельные двоичные разряды произведения с весами, соответствующими весам входных разрядов, поступающих на колонки. Переносы, возникающие в сум0маторах каждой колонки, учитываются в соседней старшей колонке сумматоров .

В результате на выходах 90, 91,

5 92, 93, 94, 95 и 96 сумматора 2 формируются двоичные разряды с весами 64, 32, 16, 8, 4, 2 и 1 двоичного произведения десятичных цифр множимого и множителя с

0 учетом входного переноса.

Разряд с весом 64 произведения может формироваться без использования сумматора 2 с помощью элемента ИЛИ 78, поскольку только на одном иэ его входов может находиться

5

единица (в противном случае наблюдается переполнение).

Блок 3 кодопреобразователей работает по следующему алгоритму.

Анализируется старшая тетрада двоичного эквивалента. Если ее значение больше или равно пяти, то значение очередного разряда (начиная Со старшего) двоично-десятичного результата принимается равным 1, а к содержимому старшей тетрады двоичного эквивалента прибавляется 3.

Выполняется сдвиг на один двоич| ый разряд полученного результата (выдвинутый при сдвиге двоичный разряд теряется).

Операции повторяются, пока не будет преобразовано все число.

Анализ значения Фтаршей тетрады двоичного эквивалента выполняется .элементами И S5 и 86 и элементом ИЛИ 87. сдвиг, необходимый по алгоритму, производится за счет последовательного подклкгчения кодопреобразователей 101-104 со смещением на разряд.

В результате на выходах 112-119 блока 3 кодопреобразователей форт мируется десятичное произведение в коде 8-4-2-1 разрядностью в две цифры. Двоичные разряды с весами

2 и 1 старшей цифры

появляются на выходах 112-115 соответственно, двоичные разряды с весами 8, 4, 2 и 1 младшей цифры - соответственно на выходах 116-119.

Таким образом, снижение аппаратурных затрат в устройстве осуществляется в результате уменьшения количества одноразрядных сумматоров сумматора с двенадцати до семи, введения блока элементов ИЛИ, на входы которого поступают те разряды с матрицы элементов, которые не мо.гут одновременно принимать единичное значение из-за избыточности кода 8-4-2-1,

. Фи1.3

111

119

фиг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

| Устройство для умножения | 1985 |

|

SU1262484A1 |

| Устройство для умножения | 1985 |

|

SU1262481A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЦИФР, содержащее блок кодопреобразователей, сумматор,матрицу элементов И размерности (П 1 4 - количество строк и столбцов), причем первый и второй входы j -го элемента И ( 1,4) матрицы соединены соответственно C.I-M разрядом множимого и -м разрядом множителя устройства, выходы элементов И р -и диагонали матрицы (р 1,3) подключены к входам р -го разряда сумматора, выходда разрядов которого соединены с младшими разрядными входами соответствующих весов блока кодопреобразователей, разрядные входы переносов сумматора соединены с соответствующими входами переносов устройства, разрядные выходы блока кодопреобразователей являются выходами устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в не го введены элемент ИЛИ и елок элементов ИЛИ, содержащий первый, второй, третий и четвертый элементы lUIH причем выход элемента И седьмой диагонали матрицы соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом переноса сумматора, выход элемента ИЛИ соединен со старшим разрядным входом блока кодопреобразователей, выходы элементов И четвертой диагонали матрицы подключены соответственно к вхо(Л дам первого и второго элементов ИЛИ блока, выходы элементов И пятой и шестой диагонали матрицы подключены соответственно к входам третьего и четвертого элементов ИЛИ блока, выходы первого и второго элементов ИЛИ блока подключены к входам четвертого разряда сумматора, выходы третьего, и четвертого элементов ИЛИ блока Ч подключены соответственно к входам пятого и шестого разрядов сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство умножения двоичнодесятичных чисел | 1974 |

|

SU510714A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3890496, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-15—Публикация

1982-11-05—Подача