производится в регистры 3, 4 памяти,| $1ричем каждое следующее повторение выталкивает предьщущее из регистра 3 в регистр 4.С помощью сумматоров 12 - 14, вычитателей 15 - 16 и пороговых элементов 19, 20 производится декодирование сообщения с учетом пре- дьщущих повторений и передача его на выход устройства с помощью комИзобретение относится к вычислительной технике и технике связи и может использоваться в системах передачи информации с трехкратным дублированием сообщений.

Цель изобретения - повыщение быстродействия .

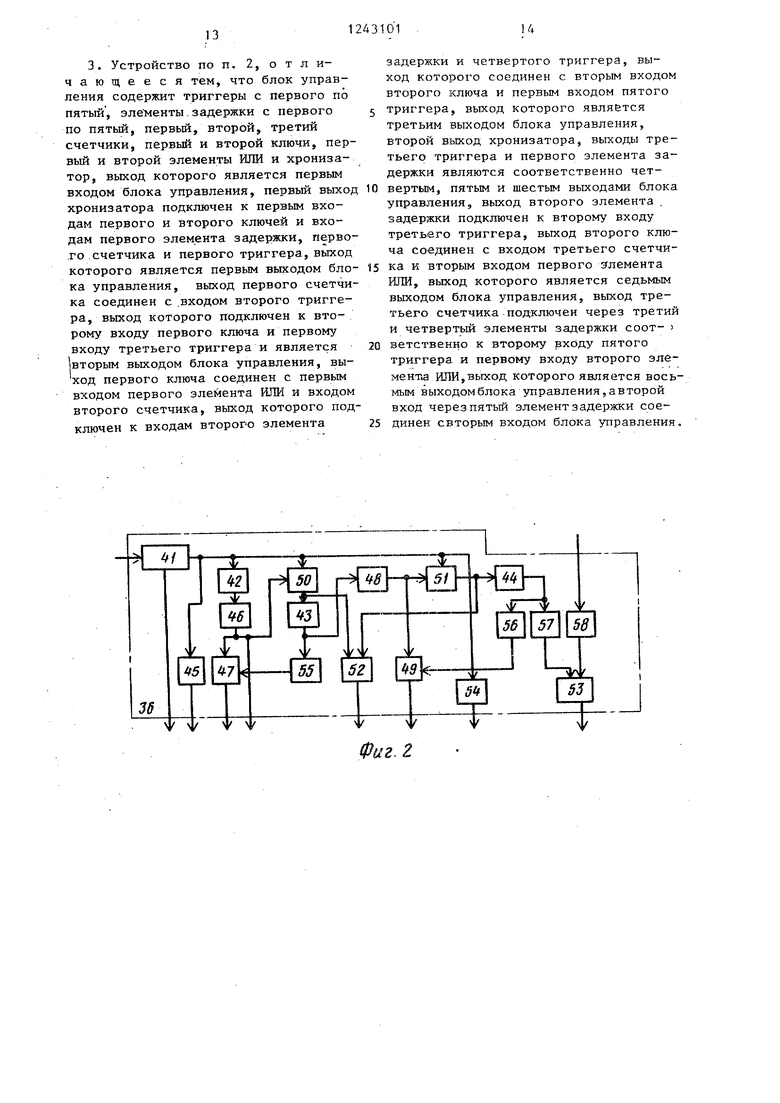

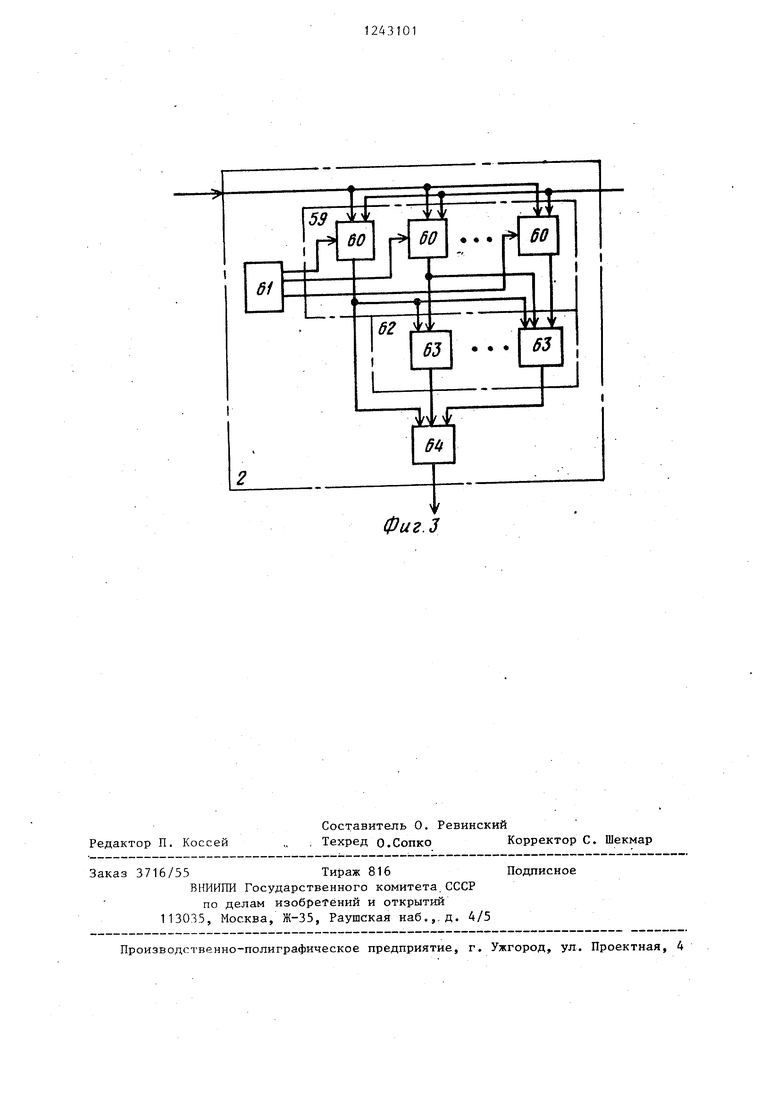

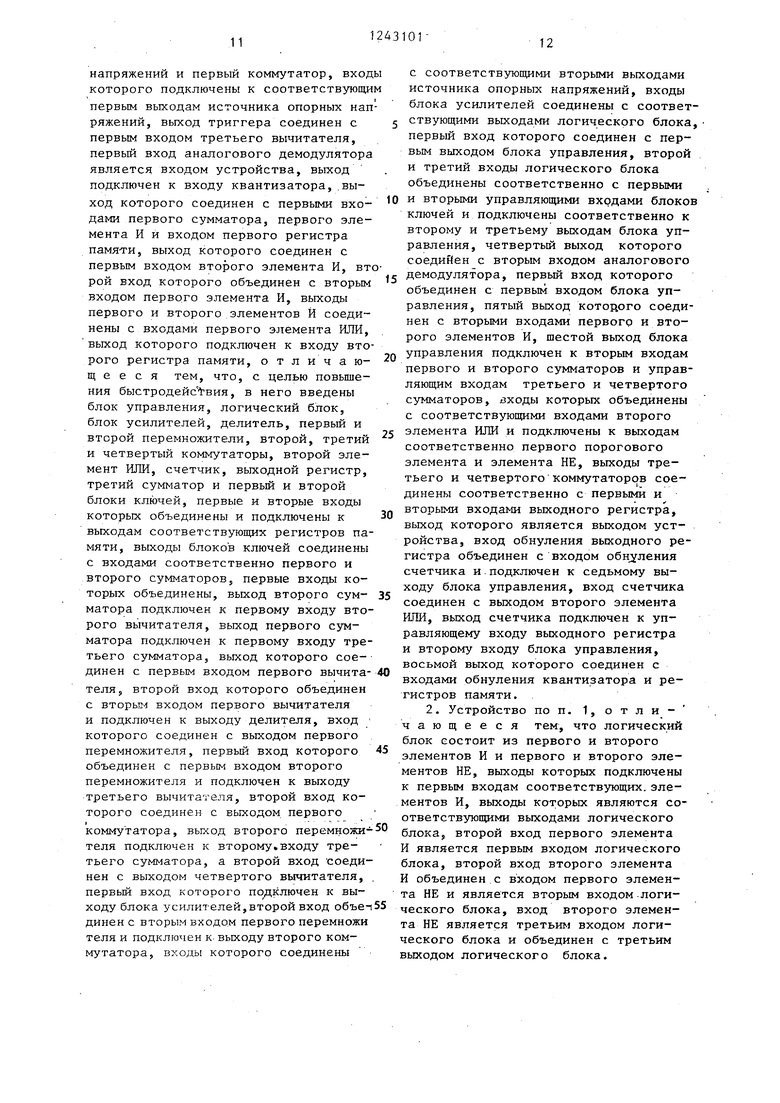

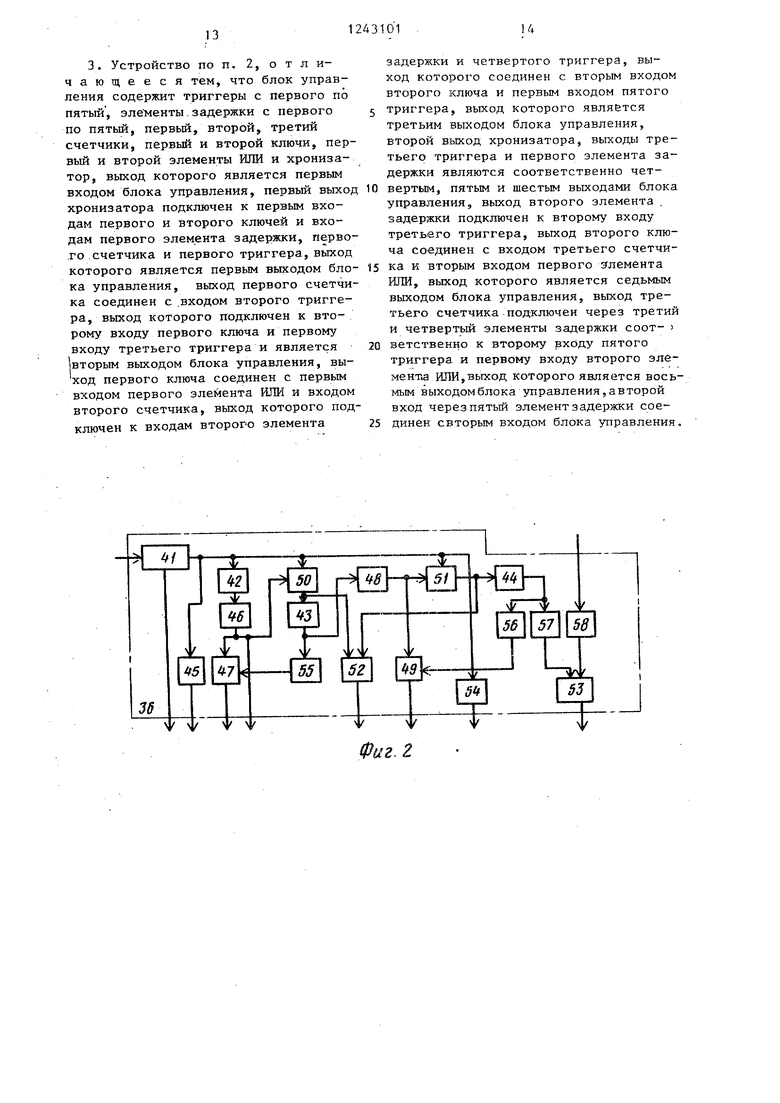

На фит;. 1 приведена функциональная схема устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема квантизатора.

Устройство для мажоритарного декодирования в целом содержит аналоговый демодулятор 1, квантизатор 2, первый и второй регистры 3 и 4 памяти, первый и второй элементы 5 и 6 И, первый 7 и второй 8 элементы ИЛИ, первый и второй блоки 9 и 10 ключей 11, первый, второй, третий сумматоры 12-14, первый, второй, третий, чет- вертый вычитатели 15-18, первый и второй пороговые элементы 19 и 20, элемент НЕ 21, счетчик 22, логический блок 23, блок 24 усилителей 25, делитель 26, источник 27 опорных напряже- НИИ, первый, второй, третий и четвертый коммутаторы 2§-31, первый и второй перемножители 32 и 33, триггер 34, выходной регистр- 35 и блок 36 управления.

Логический блок 23 состоит из первого 37 и второго 38 элементов И и первого 39 и второго 40 элементов НЕ Блок управления включает хронизатор 41, первый, второй, третий счетчики 42-44, триггеры 45-49 с первого по пятый, первый и второй ключи 50 и 51 первый 52 и второй 53 элементы ИЛИ и элементы 54-58 задержки с первого по пятый.

Квантизатор 2 может состоять из преобразователя 59 на (М-1) триггерах 60, формирователя 61 пороговых уровней, дешифратора 62 на (М-2) элементах 63 И и многоустойчивого эле- мента 64. Квантизатор 2 предназначей для преобразования входного аналогомутаторов 30, 31 и выходного регистра 35. Введение блока З б управления, логияескйго блока 23, блока 24 усилителей 25, делителя 26, перемножителя 32 И коммутатора 29 позволяет сократить время анализа, если решение о : правильном приеме может быть принято по первьи двум из трех повторений. /2 з.п. ф-лы, 3 ил.

вого сигнала, дискретизированного в аналоговом демодуляторе, в выходной М-ичный дискретный сигнал.

Первый элемент 5И открыт только на время обработки сигналов второго повторения, а второй элемент 6И от- . крыт только на время прохождения первого и третьего повторов информационных символов. I

Источник 27 опорных напряжений выдает на первые выходы напряжения, соответствующие определенным значениям количеств М зон квантования, а на вторые выходы - напряжения, соответствующие определенным значениям количеств Н повторов.

Физическая сущность алгоритма функционирования заключается в том, что при вынесении решения по соответствующему информационному символу

учитывают не только все повторения этого символа,.ной имеющееся число :повторений. С учетом этого замечания

алгоритм функционирования устройства имеет вид

i

1, если

(М-1)

о, если 21 X; + (H-i)(M-1) (

Н(М-1) 2

(1)

У 1,к; V, 1, н.

де Y: - j-й информационный сигнал (символ);

Х| - i-e повторение j-ro инфор- M aiyioHHoro сигнала в виде соответствующего сигнала на выходе квантизатора 2;

Н - количество повторений информационного сигнала;

М - количество зон квантования в квантизаторе 2.

3

Из анализа выражения (1) следует, что решение может быть вынесено не только по И повторениям (,Н), но и по меньшему их количеству, что сокращает время на принятие решения.

Коммутаторы 28 и 29 выполнены в виде наборных полей. Выходные напряжения определяются положением соответствующих перемычек.

Счетчик 22 выполнен таким образом что сигнал переполнения на его выходе появляется при поступлении на его вход К -го сигнала (здесь К - количество информационных сигналов в кодограмме)По управляющему сигналу от блока 36 управления счетчик устанавливается в исходное (нулевое)состояние.

Коммутаторы 30 и 31 управляются . сигналами с выхода блока 36. управления. Выходы коммутатора 31 соединены с единичными входами ячеек памяти регистра 35, выходы коммутатора 30 соединены с нулевыми входами соответствующих ячеек памяти регистра 35.

Блок 36 управления (фиг. 2) работает следующим образом. С помощью хронизатора 41 формируется НК (для кодов с трехкратным повторением - ЗК) тактовых импульсов, которые подаются на аналоговый демодулятор 1 и через первый элемент 54 задержки на коммутаторы 30 и 31. Первый тактовый импульс устанавливает первый триггер 45 в единичное состояние, которое в виде соответствующего сигнала подается на первый вход логического блока 23. Тактовые импульсы поступают также на вход первого счетчика 42, импульс переполнения на выходе которого формируется при поступлении на его вход К-го импульса. Этот импульс переполнения устанавливает второй триггер 46 в единк сное состояние. При этом от- крьшается первый ключ 50, на втором выходе блока 36 управления формируется управляющий сигнал для блоков 9 и 10 ключей 11 и логического блока 23, и третий триггер 47 устанавливается в единичное положение, открывая тем самым первый элемент И5 и закрывая второй элемент И6. Через открытый первый ключ 50 проходит на вход второго счетчика 43 вторая группа из К тактовых импульсов. При этом последний, то есть 2К-Й тактовый импульс (возвращает третий триггер 47 в исходное нулевое состояние и тем самым открьшает элемент И6, закрывая элемент И5 . Этот же импульс с выхода -.

43101, 4

счетчика 43 подается на четвертый триппер 48 и устанавливает его в еди-, ничное состояние, Выходной единичный сигнал четвертого триггера 48 уста- 5 навливает первый триггер 49 в единичное состояние. Выходной сигнал пятого триггера 49 подается на соответствующие входы блоков 9 и 10 кх|ючей 1 1 и логического блока 23. Выходной

10 сигнал четвертого, триггера 48, кроме того, открывает второй ключ 51. Через открытый ключ 51 тактовые импульсы подаются на вход третьего счетчика 44 и через элемент ИЛИ 52 - на входы

15 обнуления счетчик:а 22 и регистра 35 для их сброса (для этой же цели пода - ется на другой вход элемента ИЛИ 63 выходной сигнал первого ключа 50). i Импульс переполнения третьего счет20 чика 44 через четвертый элемент 57 задержки поступает на один из вхо- . , дов второго элемента ИЛИ 53, на выхо- де которого формируется сигнал Обну-. - ление. Выходной сигнал счетчика 44,

25 пройдя третий элемент 56, возвращает пятый триггер 49 в исходное состояние . На второй вход блока 36 управления подается и выходной сигнал счетчика 22. Этот сигнал после за.jg держки в пятом элементе 58 появляется :на выходе второго элемента ИЛИ 53 в виде сигнала Обнуление.

Устройство для мажоритарного деко4 дирования в .целом работает следующим, . образом.

На вход устройства поступает последовательный составной сигнал с из-. быточностью

s(t)s,,(t), S2,(t),...-, s,,(t),

40 S,) S2j(t),..., S,,(t), 5,3(1), S,,(t),..., S,j(t)J,

где К - количество информационных

сигналов в кодограмме с Н-3- кратным повторением. . В блоке 36 управления формируется последовательность тактовых импульсов, которые подают на второй вход аналогового демодулятора 1. На первый вход демодулятора поступают элементарные

канальные сигналы S (t) . В демодуляторе они преобразуются в аналоговые элементарные сигналы (существо этой операции определяется способом .приема элементарных сигналов, их типом, ха5 рактеристиками канала связи, отношением сигнал - шум и т.д.), которые определяют составной аналоговый сигнал с избыточностью .

5

V 9

X (X, X,, ,

11 12 . z °

3 ПЭ - 9

Аналоговый сигнал X последова- тельно поступает на вход квантизатора 2, а точнее - на входы триггеров 60 преобразователя 59. На другой вход каждого триггера 60 с соответствующего выхода формирователя 61 поро- гового напряжения подаются напряжения, определяющие порог срабатывания данного триггера 60, Если входной аналоговый сигнал квантизатора 2 меньше (или равен) величины первого уровня, то все триггеры 60 находятся в исходном (нулевом) состоянии. При этом на всех входах многоустойчивого элемента 64 управляющие сигналы отсутствуют j вследствие чего на выходе формируется сигнал О. Если же входной аналоговый сигнал больше первого но меньше (или равен) второго порогового уровня напряжения, то срабатывает первый триггер 5 на первом входе элемента 64 формируется управляющий сигнал, вследствие чего на выходе многоустойчивого элемента 64 фор удару ется сигнал 1. Если величина сигнала на выходе аналогового демодулятор 1 такова, что срабатывает первый и второй триггеры 60j то управляющие сигналы появляются на первых двух входах элемента 64, а его выходной сигнал имеет значение 2 и т.д. Если же величина аналогового сигнала больше величины последнего порогового уровня напряжения, то срабатывают все триггеры 60 преобразователя 59 Управляющие сигналы будут присутст- вовать на всех входах элемента 64. При этом на выходе элемента 64 появ- ляется сигнал М-1, Таким образом, с помощью квантизатора 2 аналоговые сигналы преобразуют в дискретные М- ичные сигналы. На выходе квантизатора 2 формируется последовательный дискретный избыточный сигнап

В (Ь„ , Ъ, , . о , Ь(,, Ь,2, bgj

г;

9 К

, ... 5 Ькз) 9

где efo.,1,2..., M-l, который представляет собой трехкратно повторенные информационные М-ичные символы (сигналы). Сигнал & последо-55 вательно поступает на вход первого регистра 3 памяти и одновременно через элемент ИЛИ 7 - на вход второго

регистра 4 памяти. Кроме TorOj этот сигнал подается на первые входы сумматоров 1 2 и 13. На другие входы этих cyм aтopoв поступают нулевые сигналы (т.е. на эти входы сигнал не подаются) Следовательно, на первые входы сумматоров 12 и 13 последовательно поступают сигналы Ъ,, Ь, . . ,, Ь, . На выходе этих сумматоров формируется сигнал, соответствующий сумме входных сигналов, т.е. первым выходньи сигналом каждого из рассматриваемых сумматоров будет сигнал, равный сумме Ь,, с двумя нулевыми сигналами. Далее на сумматоры подаются тактовые импульсы, которые сбрасывают этот выходной сигнал. После этого на выходе сумматоров 12 и 13 формируется сигнал, равный сумме Ъу с нулевыми сигналами, и т.д.

Наконец появляется на выходе, каждого из сумматоров 12 и 13 сигнал.

равньш сумме b

IC1

с. нулевыми сигнала

Вьгходр ой сигнал первого сумматора 12 подается на в.ход третьего сумма- гора 14, на другой вход которого поступает с выхода второго перемножителя 33 сигнал (H-i).(M-l). Этот сигнал формируется следующим образом Сигналы с соответствующих выходов источника 27 опорных напряжений через ко мму- таторы 28 и 29 подаются соответственно на входы третьего вычитателя 17 и четвертого вычитателя 18, Этот входной сигнал вычитателя 17 опреде-,, ляет значение М . На другой его вход с триггера 34, всегда находящегося в единичном состоянии, поступает сигнал 1. На выходе вычитателя 17 формируется сигнал М-1. Он подается на первые входы перемножителей 32 и 33. Входной сигнал вычитателя 18 оп- ределягет значение Н . На другой вход вычитателя 18 поступает сигнал, опред ляющий величину i, соответствующую номеру повторения информацион- ньпс сиг н;ялов В данном случае эта величина равна 1 ., Формируется номер повторения следующим образом. Для первого повторения на первом выходе блока 36 управления формируется управляющий сигнал, а на втором и третьем выходах сигналов нет. Поэтому в логическом блоке 23 сигнал формируется только ка выходе первого элемента PI 37.. Этот сигнал после соответствующего усиления в блоке 24 усилителей 25 подается на другой вход четвертого вычитателя 18. Поэтому на выходе вычитателя 18 формируется сигнал, соответствующий величине (H-i). Этот сигнал подается на второй вход второго перемножителя 33 (на его первом входе - сигнал M-l). Выходной сигнал перемножителя 33 сооувегствует величине (H-i) (). Он и подается на второй вход третьего сумматора 14, На выходе этого сумматора формируется сигнал

bji + о + о + (Н-1) (М-1), Vj 1,К.

Он поступает на первый вход второго вычитателя 15. На второй вход этого вычитателя подается сигнал

Н(М-1)

, который формируется следующим образом. На первьш вход перемножителя 32 подается сигнал, соответствующий величине (М-1). На другой его вход - сигнал, соответствующий величине Н . Поэтому на выходе перемножителя 32 формируется сигнал Н.(М-1). Этот сигнал с помощью делителя 26

Н(М-1)

преобразуется в сигнал , который и подается на второй вход первого вычитателя 15 (а также на второй вход второго вычитателя 16). На выходе вычитателя 15 формируется сигнал

bj, + (3-1)(М-1)- ,

который подается на вход второго по- рогового элемента 20. Если входной сигнал этого порогового элемента отрицательный (или равен нулю), то на его выходе формируется управляющий единичный сигнал. В противном случае единичный сигнал не формируется. Единичный выходной сигнал подается через второй элемент ИЛИ 8 на вход счетчика 22, изменяя при этом состояние последнего, и через третий ком- мутатор 30 на нулевой вход соответствующей ячейки памяти регистра 35 (т.е. для входного сигнала bjj по первому входу сумматора 13 соответствующий выходной сигнал элемента 19 за- писывается в первую ячейку и т.д., для входного сигнала Ь. - соответственно в К-ю ячейку регистра 35) .

5 0

S

Выходной сигнал второго сумматора 13 подается на первый вход второго вычитателя 16, так как на другой его вход поступает сигнал

Н(М-1) 2

то на выходе вычитателя 16 формируется разностный сигнал

, , Н(М-1)

bj, 2

V; 1, К,

0

J

который подается на вход второго элемента 20, с выхода которого этот сигнал через элемент НЕ 21 поступает на первьм вход второго элемента ШШ8. На выходе элемента НЕ 21 появляется единичный сигнал только в том случае, когда выходной сигнал вычитателя 16 является положительным. Элемент НЕ 21 предназначен для того, чтобы использовать в схеме устройства идентичные пороговые элементы 19 и 20. Выходной сигнал элемента НЕ 21 обрабатывается так же, как и выходной сигнал порогового элемента 19.

Если после обработки сигнала Ь,. на выходе счетчика 22 появится импульс переполнения, то с помощью этого сигнала осуществляется считывание информации из регистра 35 на выход устройства, после чего с помощью это-: го же сигнала в блоке 36 формируется i |Сигнал Обнуление. Если же импульса переполнения не было, то из блока 36 управления подается сигнал начальной установки счетчика 22 и регистра 35.

Далее с выхода квантизатора 2 последовательно подаются сигналы второго повторения Ь,2 Ь22. . bj . Они последовательно подаются на первые входы сумматоров 12 и 13, на вход регистра 3 памяти и через открытый в это время второй элемент И 6 и элемент ИЛИ 7 на вход второго регистра 4 памяти считьшается из первого регистра 3 памяти комбинация первого повтора. Таким образом, при обработке второго повторения информационных сигналов на первые входы сумматоров 12 и 13 подается соответствукиций символ второго повторения, на вторые входы сумматоров 12 и 13 подается соответствующий сигнал первого повторения через открытый сигналом со второго выхода блока 36 управления ключ 11 блока 9 ключей и соответствующий ключ блока 10 ключей. На третьем

входе каждого из сумматоров 12 и 13 сигналы отсутствуют. Выходные сигналы сумматоров 12 и 13 теперь определяются уже суммами первого и второ- го повторений соответствующих инфор- мационньгх сигналов и обрабатываются так же, как и сигналы первого повторения (точнее не первого повторения, а первого предъявления). При этом следует только отметить, что ненулевые сигналы присутствуют на первом и втором входах логического блока 23, а единичный сигнал формиру€;тся только на втором ее выходе. Он yci-шивается в блоке 24 усилителей, и в виде сигнала, определяющего номер второго , повторения, появляется на первом входе четвертого вычитателя 18. При этом на входе первого порогового эле- мента 19 формируется сигнал, соответствующий величине

bj, + (3-2)(М-1)- 11 ,

Vj 1, К,

а на входе второго порогового элемента 20 формируется сигнал, соответствующий величине30

(М-1)

j К.

Наконец, на выходе квантизатора 2 формируются сигналы третьего повторения , b2,,...,b j( информационных сигналов. Б это время появляется сигнал на третьем выходе блока 36 управления, вследствие чего открываются все ключи блоков 9 и 10 ключей и от- крывается пороговый элемент И5. Символы третьего, повторения сдвигают из регистра 3 символы второго повторения, а из регистра 4 - символы первого повторения. В результате на первых входах сумматоров 12 и 13 последовательно появляются символы третьего повторения, на вторых входах зтихсун маторов - символы второго повторения, на третьих входах - символы пер вого повторения. Следовательно, на выходах сумматоров 12 и 13 формируются сигналы, соответствующие сумме символов повторений одного и того же информационного символа. Выходные сигналы сумматоров 12 и 13 обрабатываются так же, как и при первом повторении . Единичные сигналы присутствуют теперь во всех входах логическо

го блока 23, вследствие чего выходной сигнал формируется только на третьем его выходе. Он усиливается и на первом входе вычитателя 18 определяет третий повтор. Входной сигнал порогового элемента 19 соответствует величине

И-З

Т-Ъ- + (з-з)(м-1)Н(М-1)

Vj Ь к.

входной сигнал элемента 20 определяется величиной

Н 5

.2::ь-,; Н(М-1)

; 1, К.

Таким образом,, для одного из повторений решение принимается по всем информаБ;ионным сигналам (срабатывает счетчик 22) и оно в виде двоичной кодовой комбинации из выходного регистра 35 считывается на выход устройства.

Очевидно, что скорость принятия решения зависит от качества канала связи: чем оно выше, тем быстрее принимается: решение.

Из выражения (1) следует, что минимально возможное число повторений, по которым принимается достоверное решение, определяется как

Гн(М-1)

1

L2(M-1)

--.1

если Н - нечетно; если Н - четно.

Следовательно, если канал хорошего качества, то решение при трехкратном повторении выносится по двум повторениям.

Формула изобретения

1. Устройство для мажоритарного декодирования в целом, содержащее аналоговый демодулятор, квантизатор, первый и второй регистры памяти, первый и второй элементы И, первый элемент ИЖ, первьш и второй сумматорь:, соединенные последовательно первый вычитатель и первый пороговый элемент, соединенные.последовательно второй вычитатель, второй пороговый элемент и элемент НЕ, третий и четвертый вы- читатели, триггер, источник опорных

напряжений и первый коммутатор, вход которого подключены к соответствующи первым выходам источника опорных напряжений, выход триггера соединен с первым входом третьего вычитателя, первый вход аналогового демодулятора является входом устройства, выход подключен к входу квантизатора,.выход которого соединен с первыми вхо- дами первого сумматора, первого элемента И и входом первого регистра памяти, выход которого соединен с первым входом второго элемента И, втрой вход которого объединен с вторым входом первого элемента И, выходы первого и второго элементов И соединены с входами первого элемента ИЛИ, выход которого подключен к входу второго регистра памяти, отличаю- щ е е с я тем, что, с целью повышения быстродейс вия, в него введены блок управления, логический блок, блок усилителей, делитель, первый и второй перемножители, второй, третий и четвертый коммутаторы, второй элемент ИЛИ, счетчик, выходной регистр, третий сумматор и первый и второй блоки ключей, первые и вторые входы которых объединены и подключены к выходам соответствующих регистров памяти, выходы блоков ключей соединены с входами соответственно первого и второго сумматоров, первые входы которых объединены, выход второго сум- матора подключен к первому входу второго вычитателя, выход первого CJTM- матора подключен к первому входу третьего сумматора, выход которого соединен с первым входом первого вычита- теля 5 второй вход которого объединен с вторьм входом первого вычитателя и подключен к выходу делителя, вход которого соединен с выходом первого перемножителя, первый вход которого объединен с первым входом второго перемножителя и подключен к выходу третьего вычитателя, второй вход которого соединен с выходом первого коммутатора, выход второго перемножителя подключен к второму.входу третьего сумматора, а второй вход соединен с выходом четвертого вычитателя, первый вход которого по дключен к выходу блока усилителей,второй вход объединен с вторым входом первого перемножи теля и подклюг ен к- выходу второго коммутатора, входы которого соединены

с соответствуюЕцими вторыми выходами источника опорных напряжений, входы блока усилителей соединены с соответствующими выходами логического блока первый вход которого соединен с первым выходом блока управления, второй и третий входы логического блока объединены соответственно с первыми и вторыми управляющими вхрдами блоко ключей и подключены соответственно к второму и третьему выходам блока управления, четвертый выход которого соедийен с вторым входом аналогового демодулятора, первый вход которого объединен с первым входом блока управления, пятый выход KOTORoro соединен с вторыми входами первого и второго элементов И, шестой выход блока управления подключен к вторым входам первого и второго сумматоров и управляющим входам третьего и четвертого сумматоров, йходы которых объединены с соответствующими входами второго элемента ИЛИ и подключены к выходам соответственно первого порогового элемента и элемента НЕ, выходы третьего и четвертого коммутаторов соединены соответственно с первыми и вторыми входами выходного регистра, выход которого является выходом устройства, вход обнуления выходного регистра объединен с входом обн уления счетчика и.подключен к седьмому выходу блока управления, вход счетчика соединен с выходом второго элемента ИЛИ, выход счетчика подключен к управляющему входу выходного регистра и второму входу блока управления, восьмой выход которого соединен с входами обнуления квантизатора и регистров памяти.

2. Устройство по п. 1, отли- чающееся тем, что логический блок состоит из первого и второго элементов И и первого и второго элементов НЕ, выходы которых подключены к первым входам соответствующих, элементов И, выходы которых являются соответствующими выходами логического блока, второй вход первого элемента И является первым входом логического блока, второй вход второго элемента И объединен с входом первого элемента НЕ и является вторым входом.логического блока, вход второго элемента НЕ является третьим входом логического блока и объединен с третьим выходом логического блока.

3. Устройство по п, 2, отличающееся тем, что блок управления содержит триггеры с первого по пятый, эле менты. задержки с первого по пятый, первьш, второй, третий счетчики, первый и второй ключи, первый и второй элементы ИЛИ и хрониза- тор, выход которого является первым входом блока управления, первый выход хронизатора подключен к первым входам первого и второго ключей и входам первого элемента задержки, первого счетчика и первого триггера, выход которого является первым выходом блока управления, выход первого счетчика соединен с .входом второго триггера, выход которого подключен к второму входу первого ключа и первому входу третьего триггера и является вторым выходом блока управления, выход первого ключа соединен с первым входом первого элемента ИЛИ и входом второго счетчика, выход которого подключен к входам второго элемента

задержки и четвертого триггера, выход которого соединен с вторым входом второго ключа и первым входом пятого

триггера, выход которого является третьим выходом блока управления, второй выход хронизатора, выходы третьего триггера и первого элемента задержки являются соответственно четвертьм, пятым и шестым выходами блока управления, выход второго элемента задер}кки подключен к второму входу третьего триггера, выход второго ключа соединен с входом третьего счетчика и вторым входом первого элемента ИЛИ, выход которого является седьмым выходом блока управления, выход третьего счетчика подключен через третий и четвертый элементы задержки соот- )

ветственно к второму входу пятого триггера и первому входу второго элементу ИЛИ,выход которого является восьмым выходом блока управления, а в торой вход через пятый элемент задержки соединек свторым входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования | 1982 |

|

SU1045383A1 |

| Устройство для мажоритарного декодирования в целом | 1983 |

|

SU1109902A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема и обработки избыточной информации | 1983 |

|

SU1140141A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема сигналов с избыточностью | 1983 |

|

SU1128281A1 |

Изобретение может найти применение в системах передачи информации с трехкратным дублированием сообще- ний. Применение этого устройства позволяет повысить быстродействие. Устройство содержит аналоговый демодулятор 1, квантизатор2, регистры 3, ; 4 памяти, элементы И 5, 6, элементы 1ШИ 7, 8, блоки 9, 10 ключей 11, сумматоры 12 - 14, вычитатели 15 - 18, пороговые элементы 19, 20, элемент НЕ 21, счетчик 22, логический блок 23,- блок 24 усилителей 25, делитель 26, источник 27 опорных напряжений-, коммутаторы 28 - 31, перемножители 32, 33, триггер 34, выходной регистр 35 и блок 36 управления. Запись каждого повторения квантованного и дис- кретизированного входного сигнала (О (Л СО

Фиг. г

Редактор П. Коссей

Составитель О. Ревинский

Техред О.Сопко Корректор С. Шекмар

Заказ 3716/55ТиРаж 816п

кнммтл п ираж «16Подписное

«НИИПИ Государственного комитета.СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,,д. 4/5

-,тп-1

Производственно-полиграфическое предприятие, г. УжгородГулГпроёктная™

Фиг.З

| Устройство для мажоритарного декодирования | 1982 |

|

SU1045383A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для мажоритарного декодирования в целом | 1983 |

|

SU1109902A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-07-07—Публикация

1984-12-20—Подача