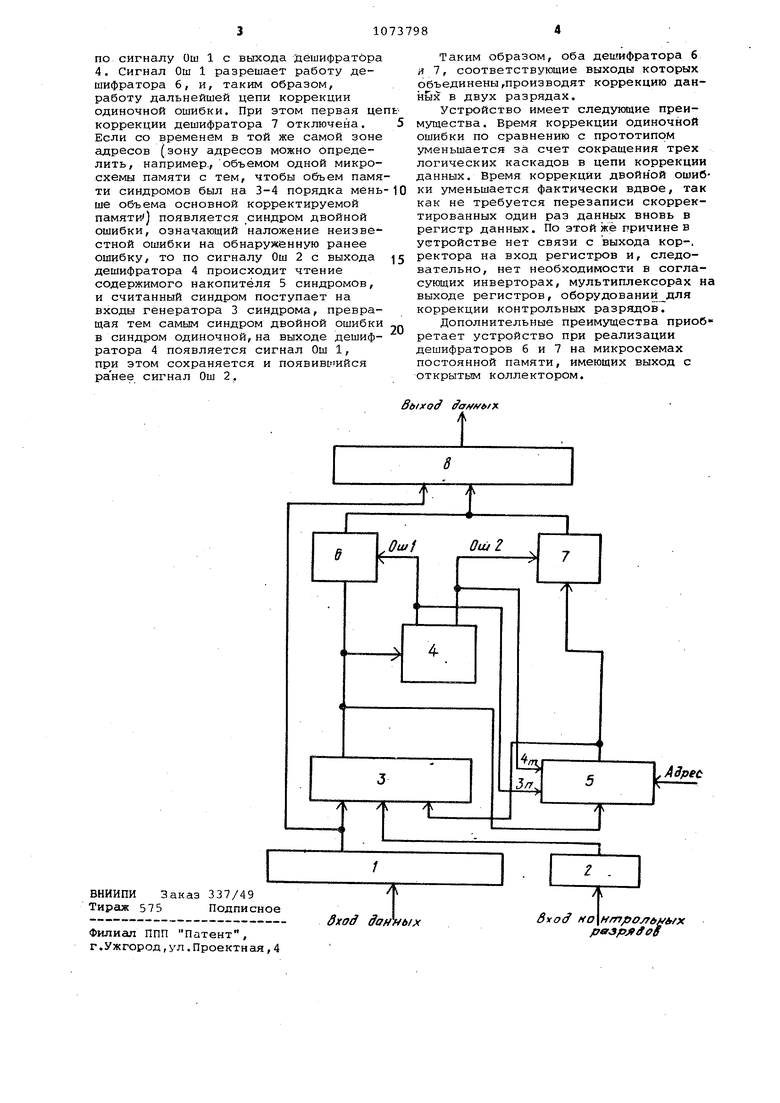

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах электронных вычислительных машин. Известно устройство для исправления ошибок в блоках памяти, содер жащее формирователь проверочного кода, дешифратор одноразрядных ошибок, блок обнаружения двойных ошибок, формирователи четности, сумматоры и элементы И и ИЛИ. Испол зование устройства на выходе блоков памяти позволяет корректировать оди ночную и определять двойную ошибку 1 . Недостатком- известного устройства является низкая эффективность контроля за счет того, что оно не может исправлять двойные ошибки. Наиболее близким к изобретению является устройство коррекции двойных ошибок блоков памяти, содержащее первый регистр, выход которого подключен к первому входу генератор синдромов и к первому входу коррек тора данных, выход которого являетс выходом устройства, второй регистр, выход которого подключен к второму входу генератора синдромов, третий вход которого подключен к накопителю синдромов, входы первого и второго регистров являются соотв-етственно входами данных и входами контрольны разрядов устройства, выход генератор синдромов подключен к первому входу первого дешифратора, второй вход которого подключен к первому выходу второго дешифратора и к первому упр ляющему входу накопителя синдромов, адресные входы которого являются адресными входами устройства, выход первого дешифратора подключен к второму входу корректора данных 2 Недостатком данного устройства является его низкое быстродействие как в случае отсутствия ошибок, так и при коррекции ошибок, вызванное удлинением цепи обработки даннЬш за счет последовательного включения .мультиплексоров, инверторов и регистра синдрома, а также последова тельным двойным срабатыванием цепи коррекции при наличии двойной ошибки. Кроме того, устройство имеет боль шие аппаратурные затраты, определенные необходимостью мультиплексироваНИН данных, необходимостью коррекции не только данных, но и контрольных разрядов и наличием ряда инверторов для согласования по фазе входных и выходных данных. . Цель изобретения - экономия оборудования и повышение быстродейст вия устройства. Поставленная цель достигается тем, -ЧТО в устройство для коррекции ошибок, в блоках памяти, содержащее первый регистр, выход которого подключен к первому входу генератора синдромов и первому входу корректора данных, выход которого является выходом устройства, второй регистр, выход которого подключен к второму входу генератора синдромов, третий вход которого подключен к накопителю синдромов, входы первого и второго; регистров являются соответственно входами данных и входами контрольных разрядов устройства,- выход генератора синдромов подключен к первому входу первого дешифратора, второй вход которого подключен к первому выходу второго дешифратора и первому управляющему входу накопителя синдромов, второй выход второго дешифратора подключен к второму управляющему входу накопителя синдромов, адресные входы которого являются адресными входами устройства, выход первого дешифратора подключен к второму входу корректора данных, дополнительно введен третий дешифратор, выход которого подключен к третьему входу корректора данных, первый и второй входы третьего дешифратора подключены соответственно к выходу накопителя синдромов и второму выходу второго дешифратора, выход генератора синдромов подключен к информационным входам накопителя синдромов и входу второго дешифратора. Сущность изобретения заключается в том, что дешифраторы выполнены в виде полупроводниковых постоянных запоминающих устройств с идентичной информацией. На чертеже представлена функциональная схема предлагаемого устрой- ства. Устройство состоит из регистра 1 для хранения данных, регистра 2 для контрольных разрядов, генератора 3 синдромов, дешифратора 4 вида ошибки, накопителя 5 синдромов, дешифраторов 6 и 7, корретора 8 данных. Выход Ош 1 дешифратора 4 ошибки, сигнал на котором соответствует наличию одиночной ошибки, соединен с управляющим входом дешифратора 6 и с управляющим входом 3ц (запись) памяти накопителя синдромов 5. Выход дешифратора Ош 2, сигнал на котором соответствует наличию двойной ошибки, соединен с управляющим входом дешифратора 7 и с управляющим входом 4fj, (чтение) накопителя 5 синдромов . Устройство работает следующим образом. При появлении одиночной ошибки синдром ошибки поступает с выходов генератора 3 синдромов на входы накопитед|я. 5 синдромов и записывается . в ..ячейку определяемую адресом данных

по сигналу Ош 1 с выхода Дешифратора 4. Сигнал Ош 1 разрешает работу дешифратора 6, и, таким образом, работу дальнейшей цепи коррекции одиночной ошибки. При этом первая цекоррекции дешифратора 7 отключена. Если со временем в той же самой зоне адресов (зону адресов можно определить, например., объемом одной микросхемы памяти с тем, чтобы объем памяти синдромов был на 3-4 порядка мень ше объема основной корректируемой памяти) появляется синдром двойной ошибки, означающий наложение неизвестной ошибки на обнаруженную ранее ошибку, то по сигналу Ош 2 с выхода дешифратора 4 происходит чтение содержимого накопителя 5 синдромов, и считанный синдром поступает на входы генератора 3 синдрома, превращая тем самым синдром двойной ошибки в синдром одиночной,на выходе дешифратора 4 появляется сигнал Ош 1, при этом сохраняется и появившийся ранее сигнал Ош 2.

Таким образом, оба дешифратора б л 7, соответствующие выходы которых Объединены,производят коррекцию данных в двух разрядах.

Устройство имеет следующие преимущества. Время коррекции одиночной ошибки по сравнению с прототипом уменьшается за счет сокращения трех логических каскадов в цепи коррекции данных. Время коррекции двойной ошибки уменьшается фактически вдвое, так как не требуется перезаписи скорректированных один раз данных вновь в регистр данных. По этой же причинен устройстве нет связи с выхода кор-. ректора на вход регистров и, следовательно, нет необходимости в согласующих инверторах, мультиплексорах н выходе регистров, оборудовании для коррекции контрольных разрядов.

Дополнительные преимущества приобретает устройство при реализации дешифраторов б и 7 на микросхемах постоянной памяти, имеющих выход с открытым коллектором.

BtllifOif Of/fft l)fI

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1608754A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Устройство для контроля блоков коррекции ошибок в памяти | 1980 |

|

SU951407A1 |

| Устройство для контроля блоков обнаружения и коррекции ошибок,работающих с кодом Хэмминга | 1982 |

|

SU1072050A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК В БЛОКАХ ПАМЯТИ, содержащее первый регистр, выход которого подключен к первому входу генератора синдромов и первому входу корректора данных, выход которого является выхог дом устройства, второй регистр, выход которого подключен к второму входу генератора синромов, третий вход которого подключен к накопителю синдромов, входы первого и второго регистров являются соответственно входами данных и входами контрольных разрядов устройства, выход генератора синдромов подключен к первому входу первого дешифратора, второй вход которого подключен к первому выходу второго дешифратора и первому управляющему входу накопителя синдромов, второй выход второго дешифратора подключен к второму управ. ляющему входу накопителя синдромов, адресные входы которого являются адресными входами устройства, выход первого дешифратора подключен к второму входу корректора данных, отличаю тем, что, с целью экономии оборудования и повышения быстродействия, оно содержит третий дешифратор, выход кртр- . S рого подключен к третьему входу коррекСП тора данных,первый и второй входы третьего дешифратора подключены соотс ветственно к выходу накопителя синдромов и второму выходу второго дешифратора, выход генератора синдромов подключен к информационным входам накопителя синдромов и входу второго дешифратора. 41 :о ;о 00

J

Ош2

Ош1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ УПРАВЛЕНИЯ ЧАСТОТОЙ КАДРОВ ЗАПИСИ И СООТВЕТСТВУЮЩЕЕ УСТРОЙСТВО | 2020 |

|

RU2782255C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4139148, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1984-02-15—Публикация

1982-04-20—Подача