бретение относится к вычислитель- снике и может быть использовано для ;ния контролепригодности оперативИз(

ной те: повыш НЫХ за|поминающих устройств.

Uej

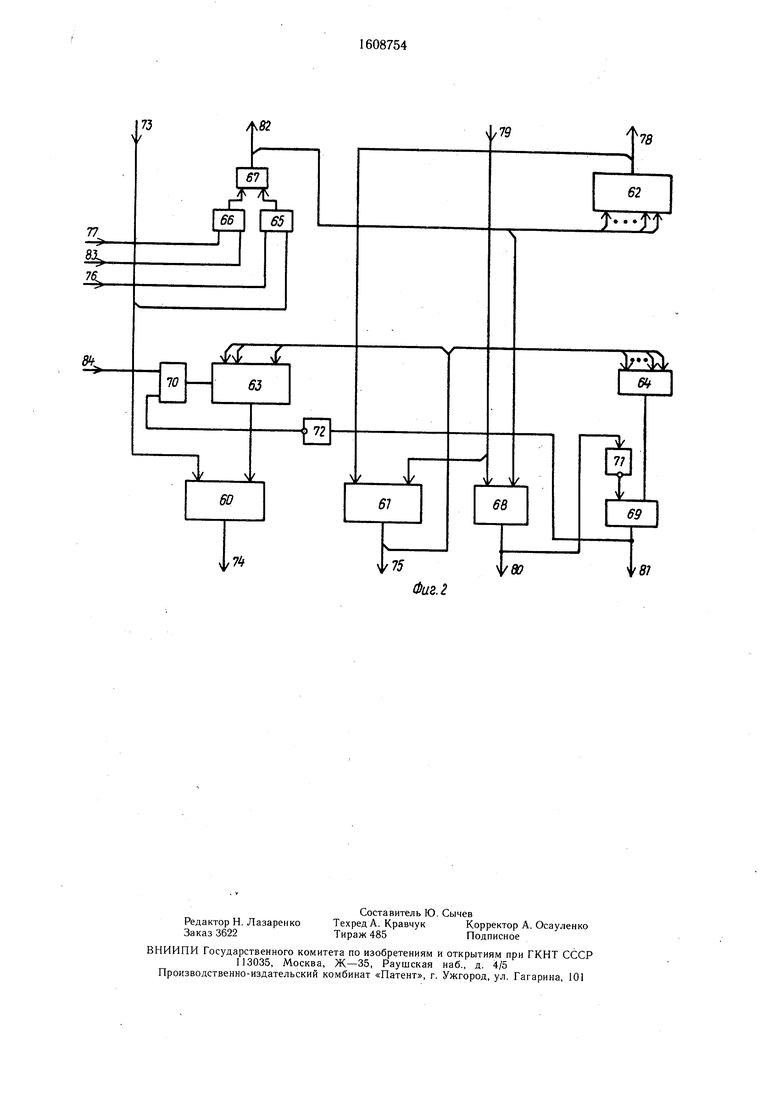

ь изобретения - повышение достофиг. 1 приведена схема запоминаю- /стройства с самоконтролем;на

- схема блока коррекции.

верности контроля.

На щего фиг. 2гг--

Запоминающее устройсво с самоконтролем содержит регистр 1 адреса, накопители информационных 2 и контрольных 3 разрядов, регистры числа 4 и состояний 5, первую 6-10,.. .-..

тую 20

тов И,

пы элементов ИЛИ, восемь элементов И 36-

зторую 11 - 15, третью 16-19, четвер- и 21 и пятую 22-26 группы элемен- первую 27-31 и вторую 32--35 груп43, блок 44 коррекции, первую 45 и вторую 46 группы приемопередающих элементов, два элемента НЕ 47 и 48 и элемент ИЛИ 49, адресные входы 50, выход 51 признака отключения коррекции, выход 52 одиночной ошибки, выход 53 двойной ошибки, информационные входы-выходы 54, вход 55 признака записи, вход 56 обращения устройства, вход 57 признака чтения, вход 58 признака обращения к накопителю, вход 59 признака обращения к регистру состояния.

Блок коррекции содержит три группы сумматоров 60-62 по модулю два, дешифратор 63, элемент ИЛИ 64, первую 65 и вторую 66 группы элементов И, группу элементов ИЛИ 67, сумматор 68 по модулю два, два элемента И 69 и 70 и два элемента НЕ 71 и 72,

О5

о 00 ел .

информационные входы 73 и выходы 74, выходы 75 синдрома ошибки, первый 76 и второй 77 управляющие входы, выходы 78 и входы 79 контрольных разрядов, выходы признака одиночной 80 и двойной 81 ошибок, выходы 82 информационных разрядов, информационные входы 83, третий управляющий вход 84.

Запоминающее устройство с самоконтролем может р-аботать в диагностическом и рабочем режимах.

В диагностическом режиме проверяется функционирование накопителей информационных и контрольных разрядов и работоспособность блока 44 коррекции. При проверке накопителей не накладывается никаких ограничений на кратность возможной ошибки.

Рассмотрим работу устройства при проверке накопителей информационных и контрольных разрядов.

Сначала устройство приводится в исходное состояние путем занесения в регистры адреса 1 числа 4 и состояний 5 нулевой информации. Затем осуществляется запись и чтение из ячеек памяти контрольных кодовых комбинаций.

В процессе записи адрес выбранной ячейки поступает на адресные входы 50 устройства, записываемое число - на информационные входы-выходы 54, признак записи - на вход 55, признак обращения к накопителю - на вход 58. Адрес ячейки записывается в регистр 1 адреса, откуда выдается на адресные входы накопителей информационных и контрольных разрядов. Записываемое число проходит на информационные входы 83 блока коррекции и на вторые входы группы элементов И 66. Признак записи и признак обращения к накопителю поступают на входы устройства высокими уровнями напряжения, поэтому на выходе элемента И 38 оказывается логическая единица (высокий потенциал), которая проходит на второй управляющий вход 77 блока коррекции и на первые входы группы элементов И 66. В результате, записываемое число поступает через группы элементов И 66 и ИЛИ 67 на входы Q2 группы сумматоров по модулю два и на выходы 82 информационных разрядов блока коррекции.

Сумматоры 62 по модулю два формируют контрольные разряды кода Хэмминга, которые выдаются на выходы 78 контрольных разрядов блока коррекции. С выходов 82 и 78 информационные и контрольные разряды проходят на входы приемопередающих элементов первой 45 и второй 46 групп, которые при наличии логической единицы на управляющих входах передают информацию с входов на свои входы-выходы и далее па входы- выходы накопителей 2 и 3.

Признак записи поступает в накопители 2 и 3 высоким уровнем с входа 55 устройства, а непосредственная запись кодового слова

10

15

25

осуществляется по сигналу обращения со входа 56. Последний проход ит в накопитель информационных разрядов 2 и через элемент И 43 в накопитель контрольных разрядов 3 (элемент И 43 открывается, так как на его первом входе в этот момент присутствуют логическая единица, поступающая через элемент ИЛИ 49 с инверсного выхода первого разряда регистра 5 состояний). Затем выполняется запись в следующую ячейку и т.д.

Перед началом процесса чтения производится отключение коррекции с тем, чтобы считанные данные выдавались из устройства без изменений. Отклонение коррекции выполняется путем записи единицы в первый разряд регистра состояний 5. С этой целью на входы-выходы 54 устройства выдается записываемое число с единицей в первом разряде и нулями в остальных, а на входы 55 и 59 - высокие уровни признака записи и

20 признак обращения к регистру 5 состояний. С входов-выходов 54 записываемое число поступает на первые входы группы элементов И 22-26 и, так как на их вторых входах присутствует высокий уровень признака записи, проходит на входы регистра состояний 5 (первый разряд - непосредственно, остальные - через группу элементов ИЛИ 32-35). При наличии признака обращения к регистру 5 состояний производится запись, в результате чего на прямом выходе его первого разряда оказывается логическая единица, а на инверсном - логический ноль (низкий потенциал).

В процессе чтения адрес выбранной ячейки поступает на входы 50, признак обращения к накопителю - на вход 58, признак чте5 ния - на вход 57. С приходом сигнала обращения на вход 56 данные считываются из накопителей информационных и контрольных разрядов 2 и 3 и поступают на входы-выходы приемопередающих элементов 45 и 46. Поскольку признак записи на входе 55 отсутст вует, на выходе элемента И 38 и на управляющих входах приемопередающих элементов 45 и 46 сохраняется логический ноль, что приводит к передаче данных с их входов- выходов на входы 73 и 79 информационных

g и контрольных разрядов блока 44 коррекции. В дальнейшем информационные разряды с входов 73 проходят на первые входы группы сумматоров 60 по модулю два. Так как коррекция отключена, на третьем управляющем входе 84 блока 44 коррекции присутствует логический ноль, что вызывает появление низкого уровня на выходе элемента И 70 и управляющем входе дешифратора 63. В результате на выходах дешифратора 63 сохраняются логические нули независимо от состояния его информационных входов, поэтому данные с первых входов группы сумматоров 60 по модулю два проходят на числовые выходы 74 блока 44 коррекции без изменений. Затем они посту30

0

5

пают ся в пы э.

на входы регистра 4 числа, записывают lero и выдаются на первые входы груп шментов И 6-10. Поскольку признак чтения приходит на вход 57 устройства высоким уровнем, на обоих входах элемента И 36 оказываются логические единицы и на его выхоЬе также формируется логическая единица. Пройдя на вторые входы элементов И 6- 10, она вызывает выдачу записанного в регистре 4 числа через элементы И 6-10 и ИЛИ27-31 на входы-выходы 54 устройства, откуда она поступает в процессор для сравнения с

ХОДОЕ

эталоном.

Одновременно контрольные разряды с вы- приемо-передающих элементов 46 по- ступаот на вторые входы группы элементов И 20 и 21. В этот момент на обоих входах элемента И 39 присутствуют высокие уровни и лог 1ческая единица с его выхода выдается на пе|)вые входы группы элементов И 20 и 21. В результате считанные контрольные разряды пр )ходят элементы И 20 и 21, ИЛИ 34 и 35 и зашсываются в регистр 5 состояний.

После завершения цикла чтения данных из накопителя информационных разрядов производится считывание регистра 5 состояний. Для этого на входы 57 и 59 устройства выдаются высокие уровни признаков чтения и обращения к регистру 5 состояний. На обоих входах элемента И 37 оказываются

ЛОГИЧ(

тывае

входы ходам санна5 И 11

пител5

Tai

одной требуе телю состояний.

Пр )верка

доват

ские единицы и на его выходе выраба- ся высокий потенциал, поступающий на втооые входы элементов И 11 - 15. Первые последних подключены к прямым вы- регистра 5 состояний, поэтому запи- в нем информация проходит элементы 15, ИЛИ 27-31 и выдается на входы- выход 1 54 и далее в процессор. Затем осу- щестЕшется чтение следующей ячейки накоинформационных разрядов.

сим образом, для чтения содержимого ячейки в диагностическом режиме тся один цикл обращения к накопи- один цикл обращения к регистру

работоспособности блока 44 коррейцин проводится в следующей послельности.

Сначала выполняется включение коррекции п|тем записи нулей в регистр 5 состояний. ПЬсле этого в накопитель записывается кодовое слово, как описано ранее, и производится отключение коррекции (в первый разря; ница). же cat,

ней оп 49 и на

сигнал теля к( нем со;

регистра 5 состояний заносится еди- Затем в накопитель записывается то юе число, но с инвертированным первым ра|зрядом. В течение выполнения послед- рации на обоих входах-элемента ИЛИ первом входе элемента И 43 присутствует НИЗКИЙ уровень напряжения, поэтому

обращения с входа 56 на вход накопи- )нтрольных разрядов не проходит. В :раняются записанные ранее по этому

10

15

5

адресу контрольные разряды, а кодовое слово в целом содержит ощибку в первом информационном разряде.

В дальнейщем коррекция вновь включается (в регистр 5 состояний заносятся нули) и осуществляется считывание данной ячейки. При этом информационные и контрольные разряды поступают на входы 73 и 7.9 блока 44 коррекции. Так как на его первом управляющем входе 76 присутствует логическая единица, информационные разряды проходят группы элементов И 65, ИЛИ 67 и выдаются на входы группы сумматоров 62 по модулю два. С выходов сумматоров 62 по модулю два сформированные контрольные разряды кода Хэмминга поступают на первые входы группы сумматоров 61 по модулю два, на вторые входы которых подаются считанные контрольные разряды с входов 79. Сумматоры 61 по модулю два сравнивают их между собой, в результате чего на их выхо20 дах формируется синдром ошибки, который выдается на выходы 75, входы элемента ИЛИ 64 и информационные входы дешифратора 63- Одновременно сумматор 68 по модулю два, складывая информационные и контрольные

25 разряды, формирует признак одиночной ошибки.

Если блок коррекции работает правильно, полученный синдром соответствует ошибке в первом информационном разряде, а на

30 выходе сумматора 68 по модулю два появляется логическая единица. Последняя инвертируется элементом НЕ 71 и запрещает формирование признака двойной ошибки на выходе элемента И 69. Логические значения признаков одиночной и двойной ощибок в

5 дальнейщем поступают на выходы 80 и 81 блока 44 коррекции (соответственно единица и ноль).

Логический ноль с выхода элемента И 69 поступает также на вход элемента НЕ 72 и на его выходе и втором входе элемента И 70 оказывается высокий уровень напряжения. На первом входе элемента И 70 присутствует высокий уровень признака включенной коррекции, поэтому на выходе элемента И 70 и управляющем входе дещифратора 63 появ5 ляется логическая единица. Дешифратор 63 выдает высокий уровень на выход, соответствующий первому информационному разряду, что приводит к его инверсии с помощью сумматоров 60 по модулю два.

В дальнейшем исправленная информация

0 с числовых выходов 74 блока 44 коррекции записывается в регистр 4 числа , откуда поступает на первые входы группы элементов И 6-10. Так как на их вторых входах присутствует логическая единица с выхода элемента И 36, считанные данные выдаются на входы-выходы 54 устройства.

Одновременно синдром и логические значения признаков одиночной и двойной ошиб- бок с выходов 75, 80 и 81 блока 44 коррекции

0

поступают на вторые входы элё-ментов И 16- 19. Поскольку регистр 5 состояний обнулен, на выходах элементов И 42, 41, 40 и первых входах элементов И 16-19 оказываются высокие уровни напряжения, поэтому синдром и логические значения признаков одиночной и двойной ошибок проходят элементы И 16- 19, ИЛИ 32-35 и записываются в нем.

В следующем цикле содержимое регистра состояний считывается. О правильной работе блока коррекции свидетельствует исправление первого разряда числа и наличие в регистре состояний соответствующего синдрома и признака одиночной ощибки. Затем описанная последовательность действий повторяется для второго разряда и т.д.

Записывая при отключенной коррекции числа с несколькими инвертированными разрядами, можно проверить формирование синдрома при одиночной ощибке и контрольных, разрядах или убедиться в правильности выдачи признака двойной ошибки. Последний поступает на выход элемента И 69 при отсутствии признака одиночной ошибки и наличии ненулевого синдрома (поступления единицы хотя бы на один вход элемента ИЛИ 64).

В рабочем режиме информацией с внешними устройствами производится при включенной коррекции. В случае обнаружения ошибки в одном из разрядов считанного числа происходит ее исправление, а признак одиночной ошибки и синдром записываются в регистр состояний. При этом на выход 52 устройства выдается логический ноль, извещающий процессор о возникшей неисправности. Если при последующем чтении данных из накопителя будет обнаружена еще одна

третий элементы И и элемент ИЛИ, информа ционные входы регистра адреса являются адресными входами устройства, выходы ре- . гистра адреса соединены с соответствующи g ми адресными входами накопителей инфор мационных и контрольных разрядов, инверс ные выходы трех младщих разрязов регистра состояний являются соответственно выходами признаков отключения коррекции одиночной и двойной ошибки устройства, выхо 0 ды элементов И первой и второй групп сое динены с соответствующими входами элементов ИЛИ первой группы, выходы которых являются информационными входами-выходами устройства, выходы элементов И треть 5 ей и четвертой групп соединены с соответствующими входами элементов ИЛИ второй группы, отличающееся тем, что, с целью по- выщения достоверности контроля, в него введены первая и вторая группы приемопередающих элементов, пятая группа элементов И,

20 с четвертого по восьмой элементы И, первый и второй элементы НЕ, выходы информационных и контрольных разрядов блока коррекции соединены соответственно с входами приемопередающих элементов первой и вто„J. рой групп, выходы которых соединены с входами информационных и контрольных разрядов блока коррекции, входы-выходы приемопередающих элементов первой и второй групп соединены с соответствующими входами-выходами накопителей информационных

30 и контрольных разрядов, выход первого элемента И пятой группы соединен с информационным входом младшего разряда регистра со стояний, выходы других элементов И пятой группы соединены с соответствующими входами элементов ИЛИ второй группы, выхоодиночная ошибка, то записи нового синдро- 35 Д которых соединены с информационными

ма в регистр состояний не произойдет, так как на первом входе элемента И 40 оказывается низкий уровень напряжения. Однако при обнаружении двойной ошибки ее признак заносится в регистр состояний и выдается низким уровнем на выход 53 устройства. Получив признак одиночной ошибки, процессор считывает содержимое регистра состояний, определяя по записанному синдрому отказавшую микросхему накопителя. В дальнейщем она заменяется в удобное для пользователя время. Признак двойной ошибки свидетельствует о потере работоспособности памяти. Тем не менее его появление не препятствует последующей записи в регистр состояний синдрома при обнаружени одиночной ошибки.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее блок коррекции, регистр

входами других разрядов регистра состояний, прямые выходы регистра числа соединены с первыми входами элементов И первой группы, вторые входы которых соединены с выходом первого элемента И и с первым управляю40 щим входом блока коррекции, прямые выходы регистра состояний соединены с первыми входами элементов И второй группы, вторые входы которых соединены с выходом второго элемента И, управляющие входы

g приемопередающих элементов первой и второй групп соединены с вторым управляющим входом блока коррекции и выходом третьего элемента И, выход четвертого элемента И соединен с первыми входами элементов И четвертой группы, вторые входы которых сое50 динены с соответствующими выходами приемопередающих элементов второй группы, выход пятого элемента И соединен с первыми входами элементов И третьей группы, кроме второго, первый вход которого соединен с выходом шестого элемента И, вторые входы

адреса, накопитель информационных и конт- 55 элементов И третьей группы, кроме первого

рольных разрядов, регистр числа, регистр состояний, четыре группы элементов И, две группы элементов ИЛИ, первый, второй и

второго и последнего элементов, соединены с соответствующими выходами синдрома ощибки блока коррекции, информационные выхотретий элементы И и элемент ИЛИ, информационные входы регистра адреса являются адресными входами устройства, выходы ре- . гистра адреса соединены с соответствующи- g ми адресными входами накопителей информационных и контрольных разрядов, инверсные выходы трех младщих разрязов регистра состояний являются соответственно выходами признаков отключения коррекции одиночной и двойной ошибки устройства, выхо 0 ды элементов И первой и второй групп сое динены с соответствующими входами элементов ИЛИ первой группы, выходы которых являются информационными входами-выходами устройства, выходы элементов И треть5 ей и четвертой групп соединены с соответствующими входами элементов ИЛИ второй группы, отличающееся тем, что, с целью по- выщения достоверности контроля, в него введены первая и вторая группы приемопередающих элементов, пятая группа элементов И,

0 с четвертого по восьмой элементы И, первый и второй элементы НЕ, выходы информационных и контрольных разрядов блока коррекции соединены соответственно с входами приемопередающих элементов первой и втоJ. рой групп, выходы которых соединены с входами информационных и контрольных разрядов блока коррекции, входы-выходы приемопередающих элементов первой и второй групп соединены с соответствующими входами-выходами накопителей информационных

0 и контрольных разрядов, выход первого элемента И пятой группы соединен с информационным входом младшего разряда регистра состояний, выходы других элементов И пятой группы соединены с соответствующими входами элементов ИЛИ второй группы, выхо5 Д которых соединены с информационными

Д которых соединены с информационными

входами других разрядов регистра состояний, прямые выходы регистра числа соединены с первыми входами элементов И первой группы, вторые входы которых соединены с выходом первого элемента И и с первым управляющим входом блока коррекции, прямые выходы регистра состояний соединены с первыми входами элементов И второй группы, вторые входы которых соединены с выходом второго элемента И, управляющие входы

приемопередающих элементов первой и второй групп соединены с вторым управляющим входом блока коррекции и выходом третьего элемента И, выход четвертого элемента И соединен с первыми входами элементов И четвертой группы, вторые входы которых соединены с соответствующими выходами приемопередающих элементов второй группы, выход пятого элемента И соединен с первыми входами элементов И третьей группы, кроме второго, первый вход которого соединен с выходом шестого элемента И, вторые входы

лементов И третьей группы, кроме первого

элементов И третьей группы, кроме первого

второго и последнего элементов, соединены с соответствующими выходами синдрома ощибки блока коррекции, информационные выходы которого соединены с входами регистра числа, вторые входы первого, и последнего элеменгов И третьей группы соединены с выходом одиночной ошибки блока коррекции, выход признака двойной ошибки которого соедин(;н с вторым входом второго элемента

И трбТ1

еи группы, первые входы элементов И

пятой группы соединены с соответствующими

ационными входами блока коррекции 1ами элементов ИЛИ первой группы.

элемен

инфop и выхо вторые объеди чтения рольныЬс разрядов, первым входом третьего

динен с первым входом пятого элемента И, инверсный выход третьего разряда регистра состояний соединен с первым входом шестого элемента И, выход седьмого элемента И соединен с вторыми входами пятого и шестого элементов И, выход первого элемента НЕ соединен с вторым входом элемента ИЛИ, выход которого соединен с первым выходом восьмого элемента И, вход выборки накопителя контрольных разрядов соединен с выховходы элементов И пятой группы 10 дом восьмого элемента И, второй вход кото- „„„„ рого соединен с входом выборки накопителя

информационных разрядов и является входом обраш,ения устройства, второй вход четвертого элемента И соединен с вторым вхо1ены и соединены с входами записи- накопителей информационных и конта И, входом первого элемента НЕ

и являн тся входом признака записи устройст-дом седьмого элемента И, первыми входами

Ы14ПРГ Г и UT ТЛ 1 Lf vr nb ntonti i-ir j- -.rtrt.-i..ва, инверсный выход младшего разряда регистра состояний соединен с первым входом седьмою элемента И, третьим управляющим входом блока коррекции, первым входом

элемен а ИЛИ и входом второго элементадом признака обращения к накопителю устНЬ, вы од которого соединен с первым вхо- 20 ройства, второй вход второго элемента И

первого и второго элементов И и является входом признака чтения устройства, второй вход первого элемента И соединен с вторым входом третьего элемента И и является входом четвертого элемента И, инверсный вы ход второго разряда регистра состояний соеявляется входом признака обращения к регистру состояний устройства.

динен с первым входом пятого элемента И, инверсный выход третьего разряда регистра состояний соединен с первым входом шестого элемента И, выход седьмого элемента И соединен с вторыми входами пятого и шестого элементов И, выход первого элемента НЕ соединен с вторым входом элемента ИЛИ, выход которого соединен с первым выходом восьмого элемента И, вход выборки накопителя контрольных разрядов соединен с выхо дом восьмого элемента И, второй вход кото- рого соединен с входом выборки накопителя

.дом признака обращения к накопителю устпервого и второго элементов И и является входом признака чтения устройства, второй вход первого элемента И соединен с вторым входом третьего элемента И и является вхоявляется входом признака обращения к регистру состояний устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1988 |

|

SU1531177A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК И КОРРЕКЦИЕЙ ОДИНОЧНОЙ ОШИБКИ | 1993 |

|

RU2062512C1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

Изобретение относится к вычислительной технике и может быть использовано для повышения контролепригодности оперативных запоминающих устройств. Цель изобретения - повышение достоверности контроля. Запоминающее устройство с самоконтролем содержит регистр адреса, накопители информационных и контрольных разрядов, регистр числа, регистр состояний, первую, вторую, третью, четвертую и пятую группы элементов И, первую и вторую группы элементов ИЛИ, элементы И, блок коррекции, первую и вторую группы приемопередающих элементов, элементы НЕ, элемент ИЛИ, выход признака отключения коррекции, выход одиночной ошибки, выход двойной ошибки, информационные входы-выходы, вход признака записи, вход обращения, вход признака чтения, вход признака обращения к накопителю и вход признака обращения. Устройство позволяет до начала решения задачи определить отказавшие микросхемы в накопителе как информационных, так и контрольных разрядов при ошибках любой кратности и проверить работоспособность блока коррекции. В рабочем режиме обеспечивается локализация одиночных ошибок (основных при одноразрядной организации БИС оперативного запоминающего устройства), что позволяет своевременно проводить профилактический ремонт памяти. 2 ил.

78

Авторы

Даты

1990-11-23—Публикация

1987-12-25—Подача