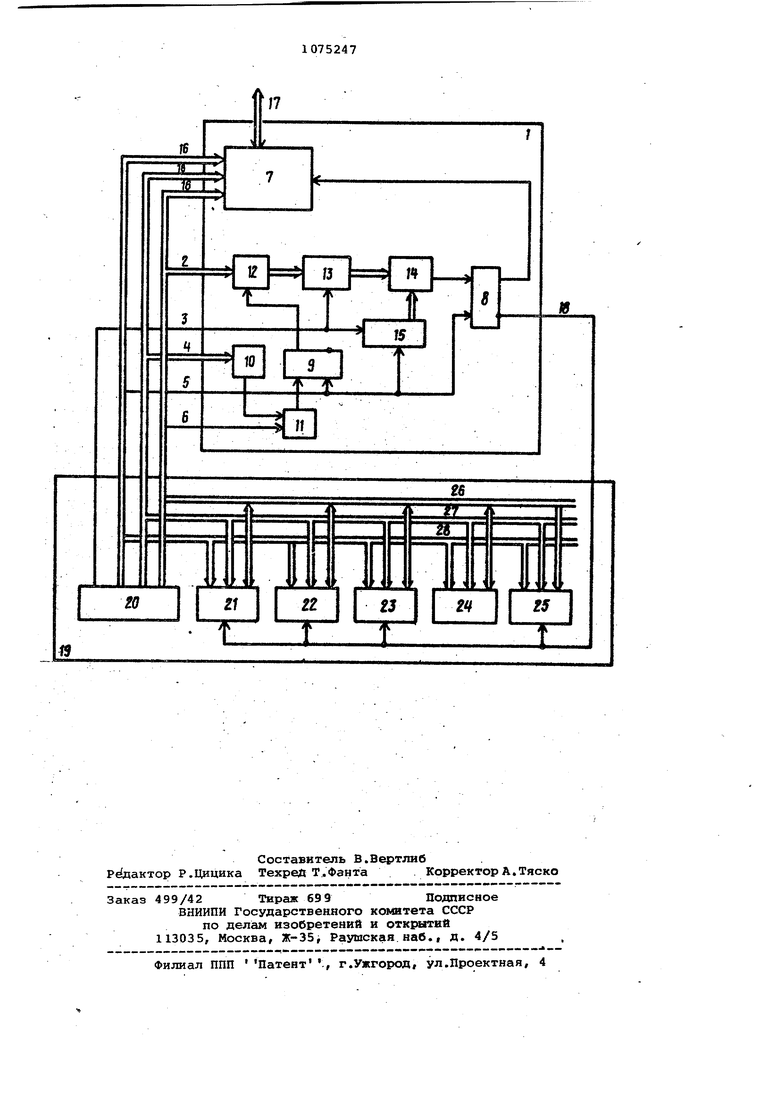

Изобретение относится к вычислительной технике и может быть использовано в системах контроля микропроцессоров для сопряясения магистрали контролируемого микропроцессора и контролирующей ЭВМ. Известно устройство для ссшряжения управляющей ЭВМ с объектами конт роля, содержащее блоки приема и выдачи управляющей информации, блок приема информации контроля, блок сбо ра информации к блок управления диаграммой обмена, включающий узел управления видом обмена, фОрмирова-. тель ОПОРНОЙ частоты, счетчик, две. схемы сравнения, два формирователя временных интервалов/ промежуточные памяти кодов времени приема и выдает чи Г1. . . : Нздостаток устройства, состоит в больших затратах оборудования. Наиболее близким к изобретению по технической сущности является устрой ство для сопряжения ЭВМ с периферийными устройствами содержащее блоки усилителей сигналов связи, группы входов-выходов которых .являются соотв-етствуклдими ,группа ж входов-выходов устройства, первые и вторые входы и выходы подключены .к..соотве.тствующим выходам я входам-блока управления обменом, первые рходы дешифраг тора и п.ервого и второго триггеров соединены соответственно с вторым, третьим и четвертым выходом первого блбка усилителей сигналов связи, выходы из группы выходов второго блока .усилителей сигналов связи соединены с соответствуюл1ими входам.и сдвигового регистра, блока формирования четности, первого коммутатора, блока выдачи прерывания иблока управления обменом, группа входов которого подключена к групце выходов дешифратора, выходы которого соединены с соответствующими входами триггеров пёрвого й второго коммутаторов и. сдвигового регистра, группа выходов которого подключена к группе входов второго коммутатора, выход первого триггера соединен с вторым входом блока вьдачи прерывания, выход первого коммутатора и вход-выход второго коммутатора соединены с.вторым входом первого блока усилителей сиг налов связи. БЛОК управления обменом содержит триггер, четыре элемен-; та ИЛИ, пять влементов И, четыре элемента НЕ и элемент задержки 2 J. Недостаток этого устройства состоит в ограниченной области принене ния. Указанное устр6йс,тво обеспечивает сопряжение между двумя магистралями ввода-вывода, в частности магистралью типа.Общая шина ЭВМ н магистралью ввода-вывода перифери ных устройств, но не обеспечивает логического объединения сопрягаемых магистралей. В результате применение этого устройства в системах контроля, например, микроэвм, имеющих магистральную структуру, практически невозможно, так как процесс контроля занимает большое время, а контролируемая микроэвм должна содержать большой объем тестовых программ. . Целью изобретения является расширение области применения устройства. Поставленаая цель достигается тем, что в устройство, содержащее сдвиговый регистр, дешифратор адреса, элемент И и блок шинных формирователей, первый и второй информацион- ные входы-вЕлходы которого являются соответственно пёрвьгм и вторым вхо-дами-выходами устройства, а управляющий вход подключен к единичному выходу триггера переключения магистралей, синхронизирунщий вход которого соединен с синхронизирующим входом триггера режима и синхронизирующим входом устройства, вход дешифратора адреса соединен с адресным входом устройства, а выход - с первым входом элемента И, введены дешифратор команд, регистр команды и схема сравнения, причем информационный вход дешифратора команд и второй вход элемента И соединены соответственно с командным и управляющим входами устройства, информсщионный вход регистра команды подключен к выходу дешифратора команд, управляющий вход которого соединен с выходом триггера режима, информационным входом подключенного к выходу элемента И, управлякицие входы регистра команды и сдвигового регистра соединены с тактовым входом устройства, а выходы - соот- ветственно с. первым и входами схемы сравнения, выход которой подключен к информационному входу триггера переключения магистралей, нулевой выход которого является блокирую щим выходом устройства, синхронизирующий вход сдвигового регистра соединен с синхрониэируквдим входом устройства. На чертеже представлена блок-схема устройства в составе системы контроля ЭВМ. На чертеже показаны устройство 1, содержащее шины 2-6 командного тактового, адресного, синхронизирующего и управляющего входов устройства, блок 7 шинных формирователей, триггер 8 переключения магистралей, триггер 9 режима, дешифратор 10 . адреса, элемент И 11, дешифратор 12 команд, регистр 13 команд, схему 14 сравнения, сдвиговый регистр 15, шины 16 и 17 первого и второго входов выходрв устройства, .блокирующий выход 18 и контролирующую ЭВМ 19, состогвдую, например, из микропроцессора 20, постоянного запоминающего устройства (ПЗУ) 21, оперативного запо-.

минающего устройства (ОЗУ) 22, бло ка ТЗ связи с магнитофоном, генератора 24 сигнатуры, блока 25 индикации и управления, информационные 26, адресные 27 и управлянщие 28 шины магистрали.

К шинам 16 подключаются шины 26 28 магистрали контролирующей ЭВМ 19, к шинам 17. - магистрали контролируемой ЭВМ (не показана) .

Устройство работает следующим образом.

При наличии сигнала на единичном выходе триггера 8 блок 7 находится во включенном состоянии и соединяет шины 26 - 28 магистрали ЭВМ 19с аналогичными шинами ЭВМ, Подключенной к шинам 17. В таком режиме ЭВМ 19 может генерировать команды и данные, содержащиеся в ОЗУ 22

и ПЗУ 21 на магистраль другой ЭВМ. блок 7. и шины 17, а также получать команды и данные из дру.гой ЭВМ.

Моменты включения блока 7 определяются содержимым регистра 13 и состоянием сдвигового регистра 15. При совпадении соответствукицих разрядов регистра 13 и сдвигового регистра 15 схема 14 сравнения устанавливает триггер 8 в состояние, при котором блок 7 включается, при несовпадении блок 7 отключается, и связь между шинами 16 и 17 разрывается, предоставляя возможность каждой из ЭВМ работать по собственным программам.

В схеме подключения, показанной на чертеже, ЭВМ 19 является ведущей и ее программа определяет моменты включения и отк1почения блока 7.

В процессе выполнения программы ЭВМ 19 на информационных шинах 26 появляются гкоманды, которые после дешифрации на деядафратрре 12, дано- сятся в регистр 13. Разрешение на ешифрацию команд, проходшцих по шинам 26, осуществляет триггер 9, включаемый ЭВМ 19 при обращениях к устройству 1. Устройство 1 является как бы одним из блоков ЭВМ.19, который имеет собственный адрес, фиксируемый дегиифратором 10. Пр . . обращениях к устройству 1 прогргичма ЭВМ 19 генерирует на шинах 27 адрес устройства 1 и выставляет на ши нах 26 позиционный код, стробируя ий элемент И 11. Если дешифратор 10 расшифровал адрес устройства 1 и присутствует строб на шинах 26 , то триггер 9 разрешает дешифратору 12 анализ кодов команд на шинах 26.

Пример использования устройства Г в системе контроля и диагностики ЭВМ

Система, показанная на чертеже, использует принцип сигнатурного анализа, при котором на проверяемой ЭВМ производится отработка тестовьос последовательностей, хранящихся в постоянном 21 или оперативном 22 запоминающих устройствах, подсчет с помощью генератора 24;сигнатуры двоичных переключений в различных его 5 в определенные интервалы времени и сравнение полученных значений (сигнатур) с эталонными, хранящимися в тех же запоминающих устройствах.

Аппаратура переключения магистра& лей устройства обеспечивает микропроцессору 20 доступ к магистрали проверяемой ЭВМ и позволяет выпбл; нять тестовые последовательности в нем при выходе из строя любого бло- . 5 ка/ подключенного к ее магистрали.

После подключения проверяемой ЭВМ шинами 17 через блок 7 микропроцессор 20 контролирующей ЭВМ 19 ока зывается подключенным к соответствуют оЩим шинам магистрали проверяемой ЭВМ, В ПЗУ 21 и ОЗУ 22 хранятся наб.эры тестовых программ и эталонньк сиг. натур.

Тестовая программа подготавливает в ОЗУ 22 необз сдимые даннь4е и рабо|чие поля, после чего вьтолняет команду вывода для установки триггера 9, который служит для включения активного режима {режима распределения). Триггер 9 адресуется как порт ввода/ /вывода и устанавливается в единичное или нулевое состояние в зависимости от состояния одного из разря;дов ьшны 26. Дешифратор 10 расшифровывает адрес триггера 9. Высокий уровень сигнала с выхода дёшифратора 10 поступает на элемент И 11, который разрешает установку или гашение триггера 9, производимые в зависимости от состояния разряда данных, поступающего с шины 26. Установка или гашение триггера 9 производится по син хронизирующему сигналу, поступающему на вход триггера 9 с шины 28 Нулевое значение сигнала на выходе трйгг.ера 9 разрешает работу дешифра тора 12, который служит для определения номер ов циклов, в которых, включается блок 7, для каждой команды, исполняемой микропроцессором 20. При этом каждому номеру цикла .соответст вует отдельных выход дешифратора 12, и ко7шчество выходов должно быть равно максимошьному числу циклов в командах микропроцессора 20. Дешифратор 1 2 может быть выполнен на кристгшлах постоянного запоминающего устроЯства с ёмкостью, равной количеству команд микропроцессора 20.

После включения триггера 9 дешифратор 12 анализирует коды на шинах 26 и после дешифрации кода команды, вы,полнвемой микропроцессором 20, устанавливает сигналы единичного уровня на тех своих выходах, которые соответствуют в данной команде, номерам

циклов, где необходимо произвести включение блока 7.

Номер командных циклов в которых производится подключение проверяемой ЭВМ, с выходов дешифратора 12 запоминается в регистре 13 по синхрониэирующему сигналу выборки команды, поступаххцему по шине 3 с выхода микропроцессора 20.

Сдвиговый регистр 15 предназначен для определения номера текущего командного цикла. Каждому командному циклу соответствует свой выход сдвигового регистра 15. По сигналу выборки команда, поступающему с микропроцессора 20 в младший разряд сдвигового регистра 15, записывается , которая затем сдвигается по каждому синхронизирутацему импульсу на шине 5, определяющему начало нового командного цикла. В рассматриваемом призере импульс на шину 5 поступает с шин 28 ЭВМ 19.

Схема 14 сравнения предназначена вьщеления тех командных циклов, в которых производится включение блока 7. При совпадении номера текущего командного цикла с номером цикла, в котором должно производиты ся включение блока 7, на выходе схемы 14 сравнения хч: танавливается единичный уровень. Выход схемы 14 сравнения соединен с инфомационным входом триггера 8. Триггер 8 служит для включения блока 7 и блокировки раббты ПЗУ 21, ОЗУ 22, блоков 24 и 25. По единичному сигналу с BHIIOда схемы 14 сравнения на единичном выходе триггера 16 устанавливается

сигнал высокого уровня, включакади блок 7, а на его нулевом выходе устанавливается сигнал низкого уровня, блокируннций работу блоков ЭВМ 19. Гашение триггера 8 производится при несовпадении номеров командных циклов. Микропроцессор 20 выдает проверочное воздействие в проверяемую ЭВМ или считывает результат предьвдущего проверочного воздействия. Генератор 24 сигнатуры поочередно подключается к. контрольным точкам проверяемой ЭВМ, номер которых индицируется в блоке 25. Полученные сигнатуры программы ЭВМ 19 сравнивает с эталонными. При их несовпадении автоматически зацикливается программа генерации тестовой последовательности сигнатурного анализа для блока или устройства, в котором обнаружена ошибка, и производится локализация отказа путем проверки сигнатур всех схем, входящих в неисправный блок. После обнаружения неисправной Схемы или группы схем их номер индицируется в блоке 25.

В конце теста после окончания проверки выполняется команда вывода информации, гасящая триггер 9, после чего микропроцессор 20 отключается от магистрали контролируемой ЭВМ и работает только с внутренними ресурсами ЭВМ 19.

Таким образом, устройство позволяет осуществить связь между двумя ЭВМ без применения принципа внутрисхемной эмуляции, что и обеспечивает расширение области применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1501065A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

УСТРОЙСТВО ДЛЯ ЗАХВАТА МАГИСТРАЛИ ЭВМ, содержащее сдвиговый регистр, дешифратор адреса, элемент К и блок шинных формирователей, первый и второй информационные входы-выходы которого являются соответственно первым и вторым входами-выходами устройства, а управляющий вход подключен к единичному выходу триггера переключения магистралей, синхронизирующий вход которого соединен с синхронизирующим входом триггера режима и синхронизирующим входом устроййтва, вход дешифратора адреса соединен с адресным входом устройства, а выход с первым входом элемента И, о т личающеес я тем, что., с целью расширения области применения устройства, в него введены дешифратор команд, регистр команд и схема сравнения, причем информационный вход дешифратора команд и второй вход элемента И соединены соответственно с командным и управляющим входами устройства, информационный вход регистра команды подключен к йькоду дешифратора команд, управляющий вход которого соединен с вькодом триггера реяшма, информационным входом подключенного к выходу элемента И, управляющие в;:оды регистра команды и сдвигового регистра Соединены с так(П товым входом устройства, а выходы соотв етственно с первым и .вторым входами схемы сравнения, выход которой подключен к информационному входу триггера переключения магистралей, нулевой выход которого является блокирующим выходом устройства, синхронизирующий вход сдвигового регистра соединен с синхронизирующим входом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена управляющей эвм с объектами контроля | 1977 |

|

SU783780A1 |

| С, 06 F 3/04, 1977 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ьвторское свидетельство СССР но заявке № 3286965/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-04-05—Подача