вым управляющим входом двунаправленных магистральных усилителей данных группы, со стробирующим входом дешифратора управляющих сигналов и входом режима устройства, а четвертый и пятый входы - соответственно с входом сигнала ожидания и входом разрешения доступа к магистрали устройства, третий вход триггера готовности является входом сигнала ответа устройства, третий выход блока асинхронного обмена соединен с управляющими входами магистральных усилителе адреса группы и вторыми управляющиьш входами двунаправленных магистральных усилителей данных группы, причем блок асинхронного обмена содержит два триггера, два элемента И и элемент ИЛИ,- причем выход элемента ИЛИ соединен с первым выходом блока асинхронного обмена, а входы образуют третий вход блока асинхронного обмена, установочный вход первого триггера является вторым входом блока асинхронного обмена, а выход является вторым выходом блока асинхронного обмена и соединен с первым входом первого элемента И, второй вход которого соединен с четвертым входо блока асинхронного обмена и с инверсным установочным входом второго триггера, информационный вход и выход которого подключены соответственно к выходу первого элемента И и третьему выходу блока асинхронного обмена, синхронизирующие входы первого и второго триггеров соединены с первым входом блока асинхронного обмена, первый и второй входы второго элемента И соединены соответственно с пятым входом блока асихронного обмена и выходом элемента ИЛИ, а выход - с информационным входом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

УСТРОЙСТВО МИКРОПРОЦЕССОРНОЙ СВЯЗИ, содержащее группу магистральных усилителей адреса, группу двунаправленных магистральньк усилителей данных, элемент И, регистр состояния, управляющий вход которого соединен с.выходом элемента И, дешифратор управлякицих сигналов, блок асинхронного обмена, триггер готовности, триггер запроса доступа к магистрали и генератор тактовых сигналов, выходом соединенный с первыми входами триггера готовности, триггера запроса доступа к магистрали, блок асинхронного обмена, элемента И и синхронизирующим выходом устройства, причем информационные входы магнйстральных усилителей адреса группы соединеныс адресным входом устройства, а выходы - с адресным выходом устройства, первые информационные входы-выходы двунаправленных магистральных усилителей данных группы соединены с первым информационным входом-выходом устройства и информационным входом регистра состояния, а вторые информационные входывыходы - с вторым информационным входом-выходом устройства, выход регистра состояния соединен с информационным входом дешифратора управляющих сигналов, группа выходов которого является группой выходов управляющих сигналов устройства, первый выход блока асинхронного обмена соединен с разрешающим входом дешифратора управляющие си1налов, второй выход с вторым входом триггера запроса доступа к магистрали, выход которого является выходом запроса доступа (Л к магистрали устройства, второй вход элемента И соединен с входом синхронизации устройства, выход триггера готовности является выходом готовности устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач, в устрой1 9 ство введены память микропрограмм nU 1C СП и дешифратор адреса, причем информационные входы дешифратора адреса и памяти микропрограмм соединены с адресным входом устройства, первый выход дешифратора адреса соединен с управляющим входом памяти микропрограмм, а второй выход соединен с вторыми входами триггера готовности и блока асинхронного обмена и третьим входом триггера запроса дог ступа к магистрали, а управляющий вход - с выходом регистра состояния выход ламяти микротфограмм соединен с первым информационным входом-выходом устройства, третий вход блока асинхронного обмена соединен спер

1

Изобретение относится к вь4числительной технике и может быть использовано при построении средств микропрограммного управления в системах обработки данных и регулирования.

Известны устройства для связи микропроцессора с внешними устройствами, содержащие микропроцессор, генератор тактовых импульсов, многорежимные буферные регистры, шинные формирователи и систему шин, образующих интерфейсную магистраль 1 .

В этих устройствах отсутствуют средства, обеспечивающие доступ к работе с интерфейсной магистралью другим активным устройствам (микропроцессор занимает интерфейсную магистраль не только на время цикла обмена, но и при выполнении внутренних операций). Для использования магистрали другими активными устройствами в микропроцессорах предусмотрена шина Блокировка. При наличии на этой щине сигнала от внешнего активного устройства микропроцессор останавливает выполнение программы (входит в режим Блокировка), переводит в высокоимпедансное состояние выходы адреса и данных, снимает

управляющие сигналы и выдает сигнал Подтверждение блокировки, по которому активное устройство, выдавшее сигнал Блокировка, может использо5 вать интерфейсную магистраль для обмена информацией.

Недостатком известньк устройств является низкая пропускная способность, так как при такой организа10 ции захвата магистрали активными устройствами микропроцессор разрешает доступ к магистрали не в процессе его подготовительных действий и выполнения внутренних операций, 5 а в остановленном состоянии.

Наиболее близким по техническому решению является устройство микропроцессорной связи, содержащее регистр данных, интерфейсную магист0 раль, группу магистральных усилителей адреса, группу двунаправленных магистральных усилителей данных, элемент И, регистр состояния,, уцравляимций вход которого соединен с вы ходом элемента И, дешифратор управляюицис сигналов, блок асинхронного обмена, триггер готовности, блок запроса доступак магистрали и генератор тактовых сигналов, выходом 3 соединенный с первыми входами триггера готовности, блока запроса дост па к магистрали, блока асинхронного обмена, элемента И и с синхронизирующим выходом устройства, причем информационные входы магистральных усилителей адреса группы являются адресным входом устройства, а выходы - адресным выходом устройства, первые информационные входы-выходы двунаправленных магистральных усили телей данньк группы соединены с пер вым информационным входом-выходом устройства и информационным входом регистра состояния, а вторые информационные входы-выходы - со вторым информационным входом-выходом устройства, выход регистра состояния соединен с информационным входом де шифратора управляющих сигналов, группа выходов которого является группой выходов управляющих сигнало устройства, первый выход блока асин хронного обмена соединен с разрешаю щим входом дешифратора управляющих сигналов, второй вькод - со вторым входом блока запроса доступа к маги страли, выход которого является выходом запроса доступа к магистрал устройства, второй вход элемента И соединен с входом синхронизации уст ройства, выход триггера готовности является выходом готовности устройства . Работа данного устройства органи зована таким образом, что во время пауз, обусловленных выполнением микропроцессором внутренних операци его интерфейсная магистраль может принадлежать другому активному устррйству(2). Недостаток устройства состоит в ограниченном классе решаемых задач, так как при чтении командных слов микропроцессор занимает интерфейсную магистраль, так как память, хранящая программу, составляет част общего поля адресуемой памяти. Цель изобретения - расширение класса решаемых задач устройства за счет высвобождения его интерфейсной магистрали при выполнении микропроцессором микропрограммы и обеспечение возможности использования освободившегося адресного поля другими активньми устройствами, подключенными к этой магистрали. 5 Поставленная цель достигается тем, что в устройство микропроцессорной связи, содержащее группу магистральных усилителей адреса, группу двунаправленных магистральных усилителей данных, элемент И, регистр состояния , управлякжшй вход которого соединен с выходом элемента И, дешифратор управляющих сигналов, блок асинхронного обмена, триггер готозности, триггер запроса доступа к магистр али и генератор тактовых сигналов, выходом соединенный с первыми входами триггера готовности, триггера запроса доступа к магистрали, блока асинхронного обмена, элемента И и синхронизирующим выходом устройства, причем информационные входы магистральных усилителей адреса, группы соединены с адресным входом устройства, а выходы - с адресным выходом устройства, первые информационные входы-выходы двунаправленных магистральных усилителей данных группы соединены с первым информацнонньм входом-выходом устройства и информационным входом регистра состояния, а вторые информационные входывыходы - со вторым информационным входом-выходом устройства, выход регистра состояния соединен с инфор мационным входом дешифратора управляющих сигналов,группа выходов которого является группой выходов управляющих сигналов устройства, первый выход блока асинхронного обмена соединен с разрешакшщм входом дешифратора .управляющих сигналов, второй выход - со вторым входом триггера, запроса доступа к магистрали, выход которого яйляется выходом запроса доступа к магистранта устройства, . второй вход элемента И соединен с входом синхронизации устройства, выход триггера готовности является выходом готовности устройства, введены память микропрограмм и дешифратор адреса, причем информационные входы депшфратора адреса и пайяти микропрограмм соединены с адрес7 ным входом устройства, первый выход дешифратора адреса соединен с управляющим входом памяти микропрограмм, а второй выход - соединен со вторыми входами триггера готовности и блока асинхронного обмена и третьим входом триггера запроса доступа к магистрали, а управляющий вход с выходом регистра состояния, выход

памяти микропрограмм соединен с первым информационным входом-выходом устррйства, третий вход блока асинхронного обмена соединен с первым управляющим входом двунаправленных магистральных усилителей данных группы, со стробирующим входом дешифратора управляющих сигналов и входом режима устройства, а четвертый и пятый входы - соответственно со входом сигнала ожидания и входом разрешения доступа к магистрали устройства, третий вход триггера готовности является входом сигнала ответа устройства, третий выход блока асинхронного обмена соединен с управлякмцими входами магистральных усилителей адреса группы и вторыми управляющими входами двунаправленных магистральных усилителей данных группы, и тем, что блок асинхронного обмена содержит два триггера, два элемента И и элемент ИЛИ, причем выход элемента ИЛИ соединен с первым выходом блока асинхронного обмена, а входы - образуют третий вход блока асинхронного обмена, установочный вход первого триггера является вторым входом блока асинхронного обмена, а выход - является вторым выходом блока асидхронного обмена и соединен с первым входом первого элемента И, второй вход которого соединен с четвертым входом блока .асинхронного обмена и с инверсным установочным входом второго триггера, информационный вход и выход которого подключены соответственно к выходу первого элемента И и третьему выходу блока асинхронного обмена, синхронизирующие входы первого и второго триггеров соединены С первым входом блока асинхронного обмена, первый и второй входы второго элемента И соединены соответственно с пятым входом блока асинхронного обмена и выходом элемента ИЛИ, а выход с информационным входом первого триггера .

I

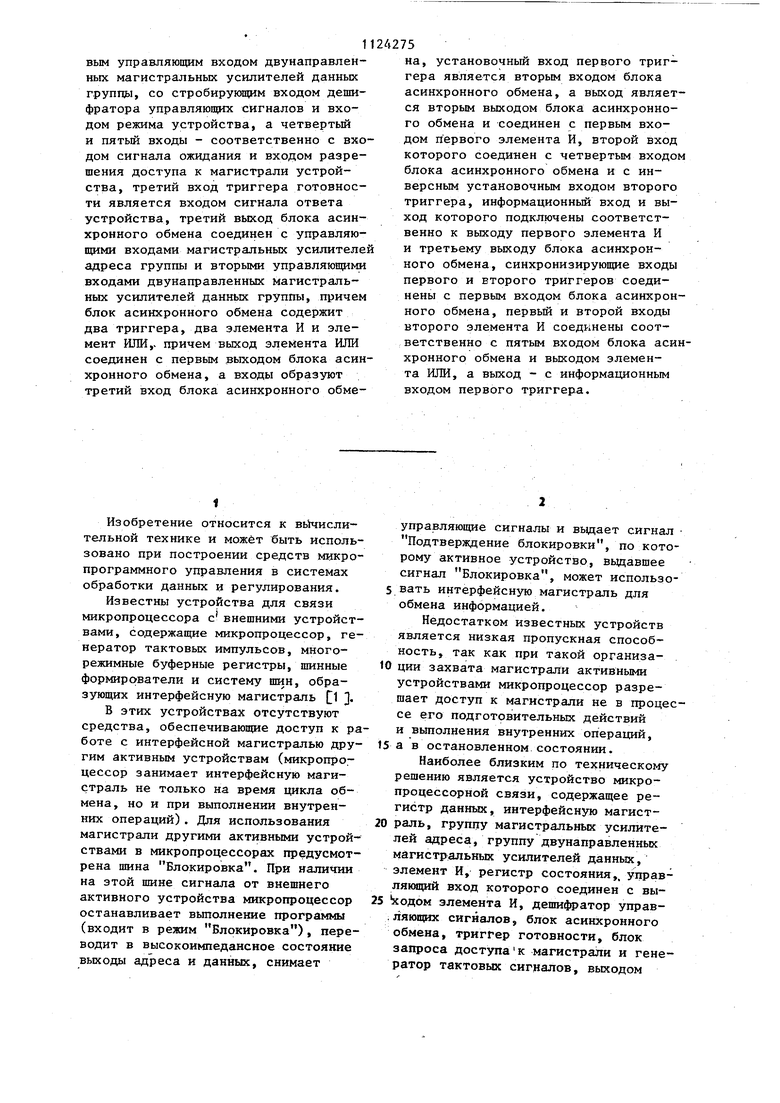

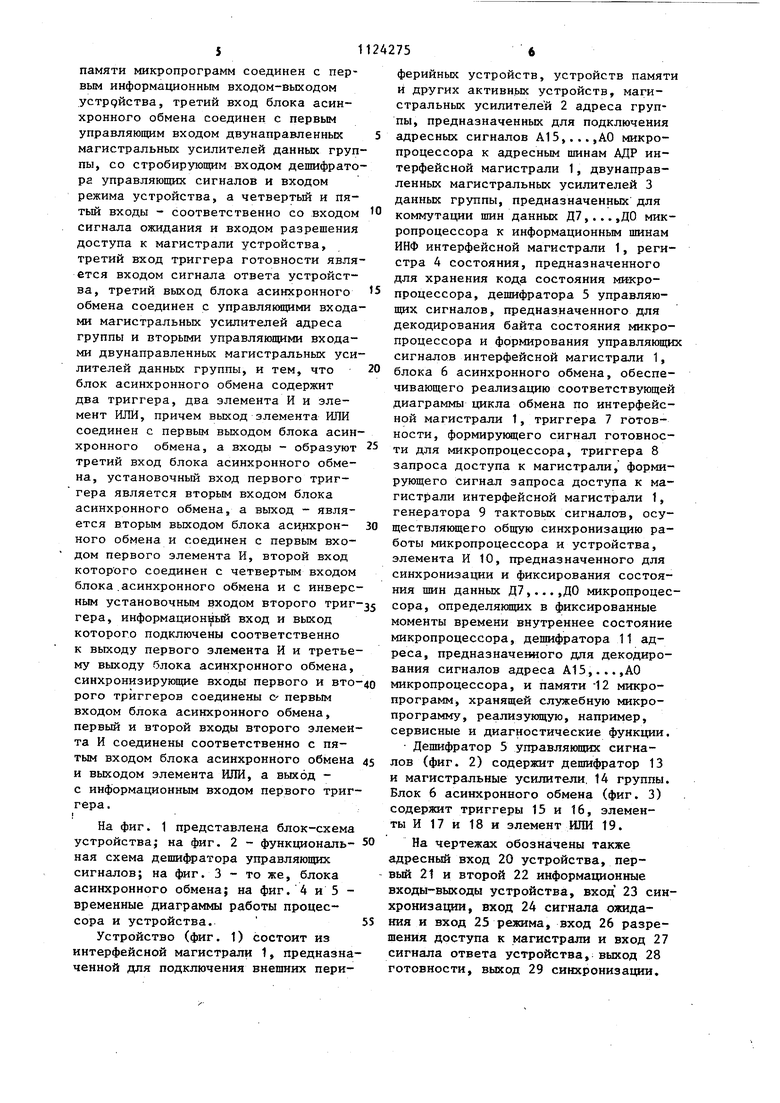

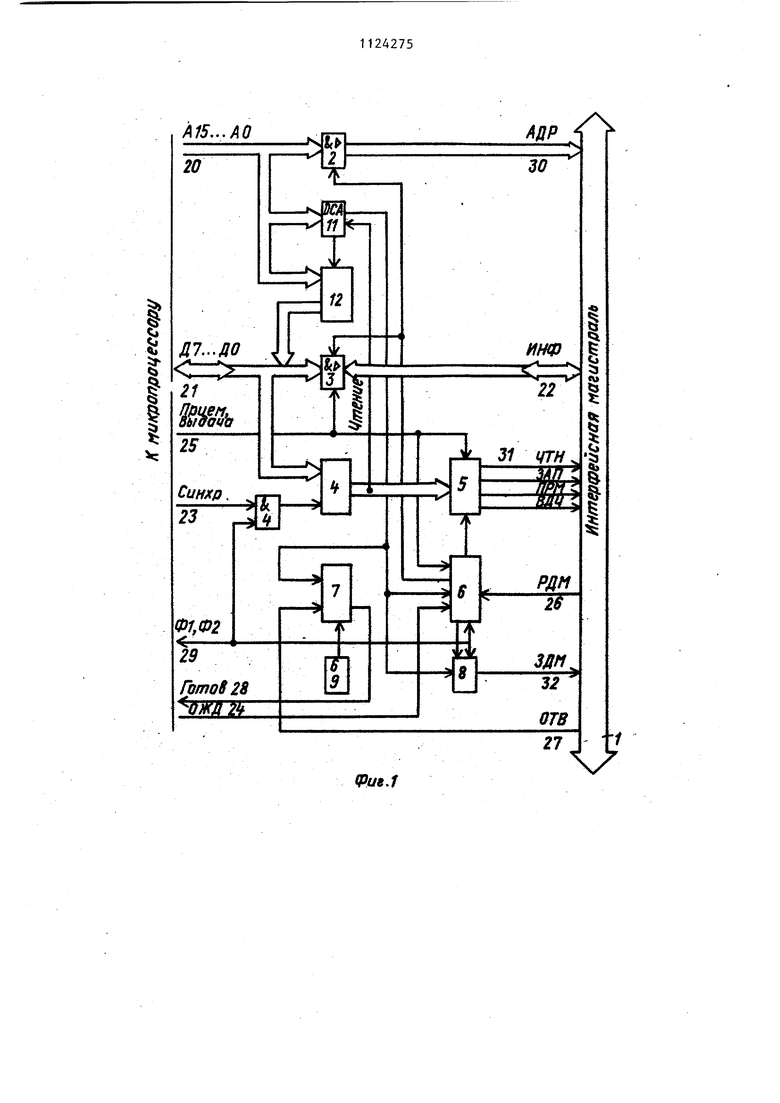

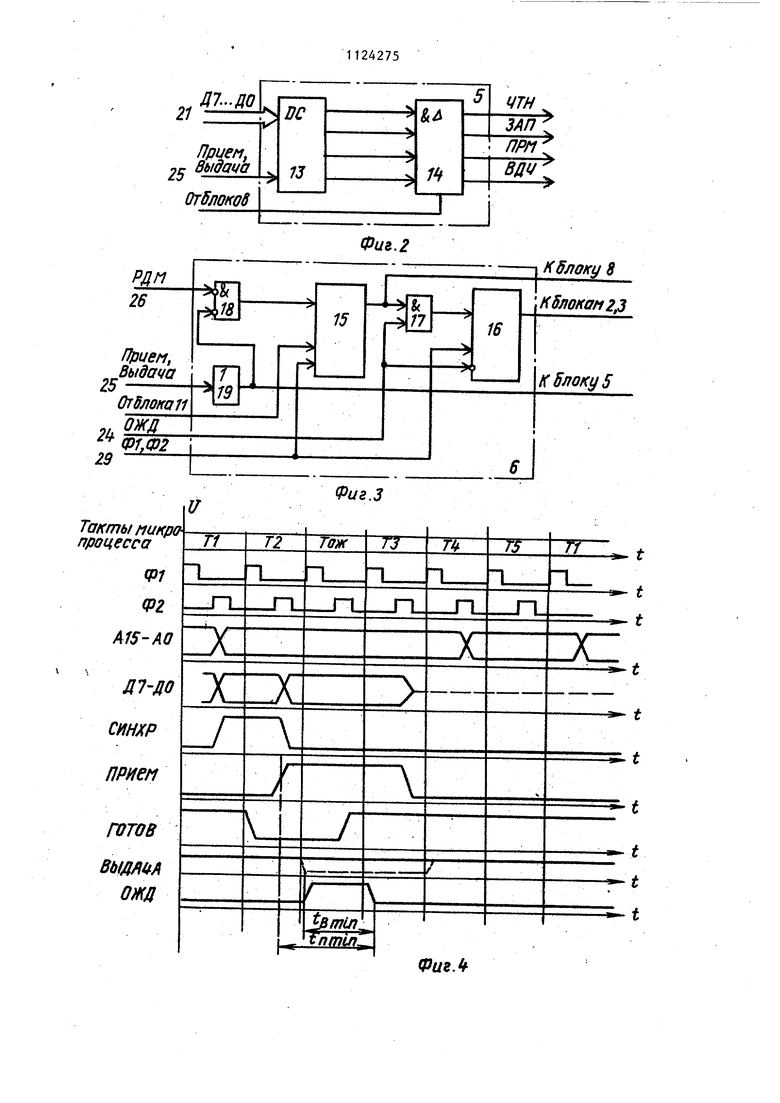

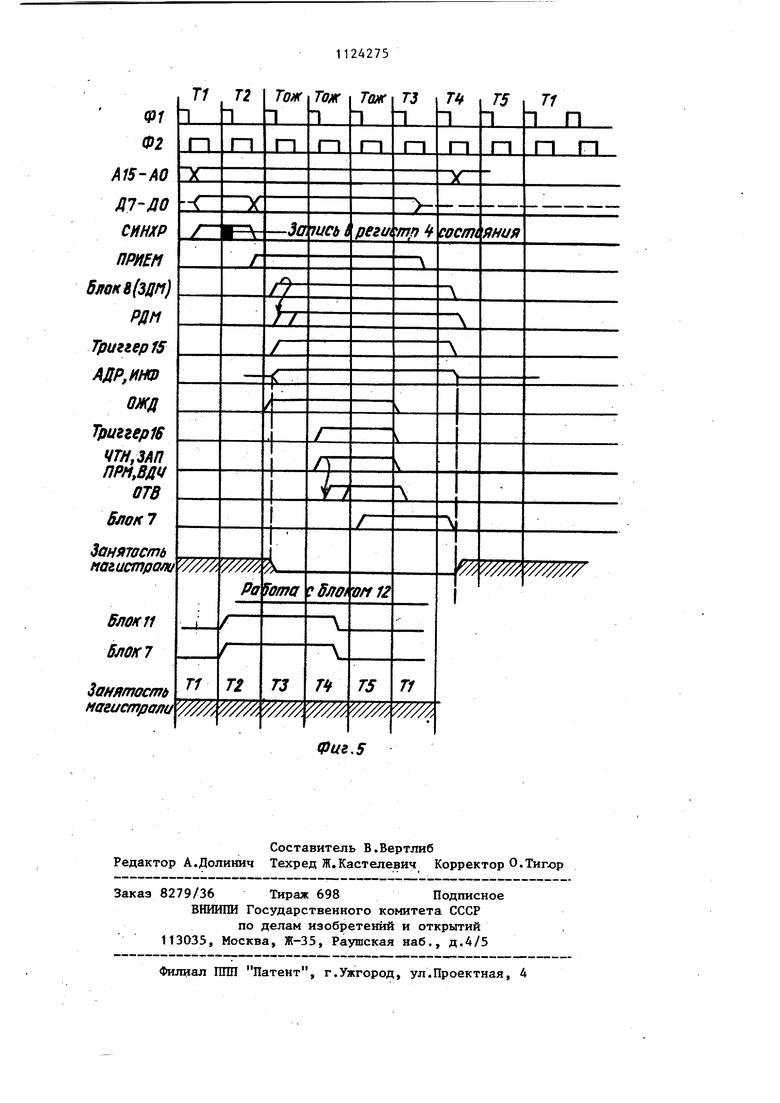

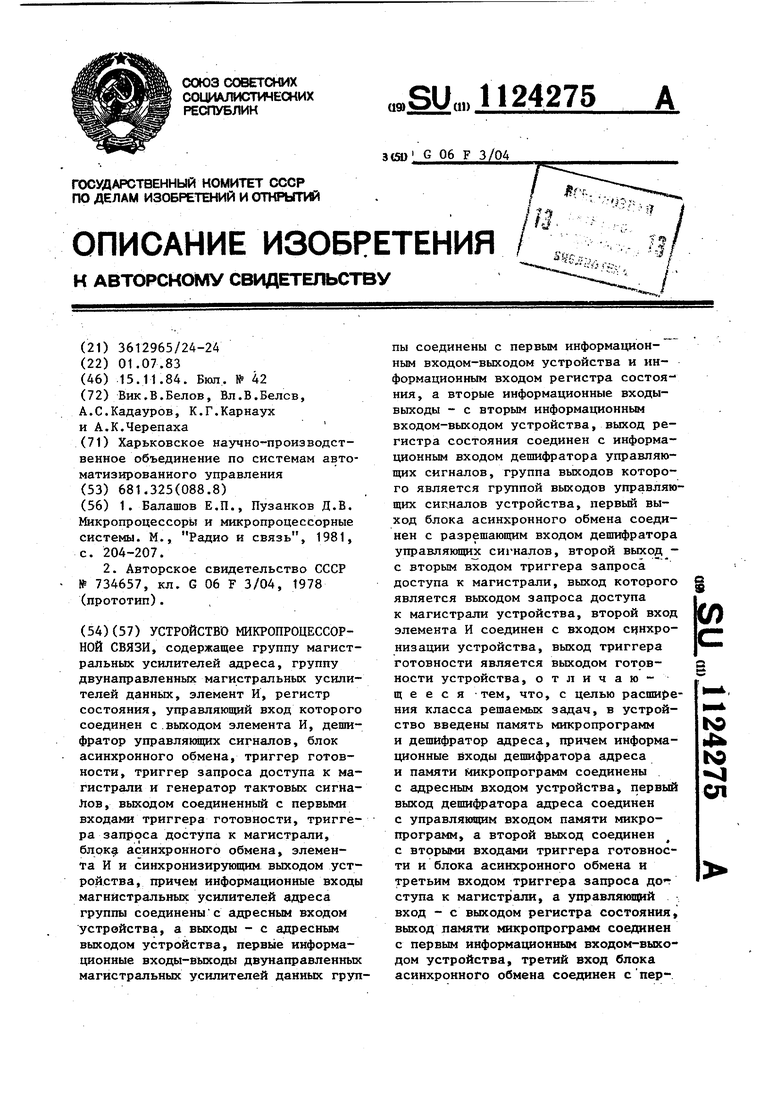

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема дешифратора управляющих сигналов; на фиг. 3 - то же, блока асинхронного обмена; на фиг. 4 и 5 временные диаграммы работы процессора и устройства.

Устройство (фиг. 1) состоит из интерфейсной магистрали 1, предназначенной для подключения внешних периферийных устройств, устройств памяти и других активн.ых устройств, магистральных усилителей 2 адреса группы, предназначенных для подключения адресных сигналов А15,...,АО микропроцессора к адресным шинам АДР интерфейсной магистрали 1, двунаправленных магистральных усилителей 3 данных группы, предназначенных для коммутации шин данных Д7,...,ДО микропроцессора к информационным шинам ИНФ интерфейсной магистрали 1, регистра 4 состояния, предназначенного для хранения кода состояния микропроцессора, дешифратора 5 управляюпщх сигналов, предназначенного для декодирования байта состояния микропроцессора и формирования управляющи сигналов интерфейсной магистрали 1, блока 6 асинхронного обмена, обеспечивающего реализацию соответствующей диаграммы цикла обмена по интерфейсной магистрали 1, триггера 7 готовности, формирующего сигнал готовности для микропроцессора, триггера 8 запроса доступа к магистрали, формирующего сигнал запроса доступа к магистрали интерфейсной магистрали 1, генератора 9 тактовых сигналов, осуществлякядего общую синхронизацию работы микропроцессора и устройства, элемента И 10, предназначенного для синхронизации и фиксирования состояния шин данных Д7,...,ДО микропроцессора, определякицих в фиксированные моменты времени внутреннее состояние микропроцессора, дешифратора 11 адреса, предназначенного для декодирования сигналов адреса А15,...,АО микропроцессора, и памяти 12 микропрограмм, хранящей служебную микропрограмму, реализующую, например, сервисные и диагностические функции.

Дещифратор 5 управляющих сигналов (фиг. 2) содержит дешифратор 13 и магистральные усилители, 14 группы. Блок 6 асинхронного обмена (фиг. 3) содержит триггеры 15 и 16, элементы И 17 и 18 и элемент ИЛИ 19.

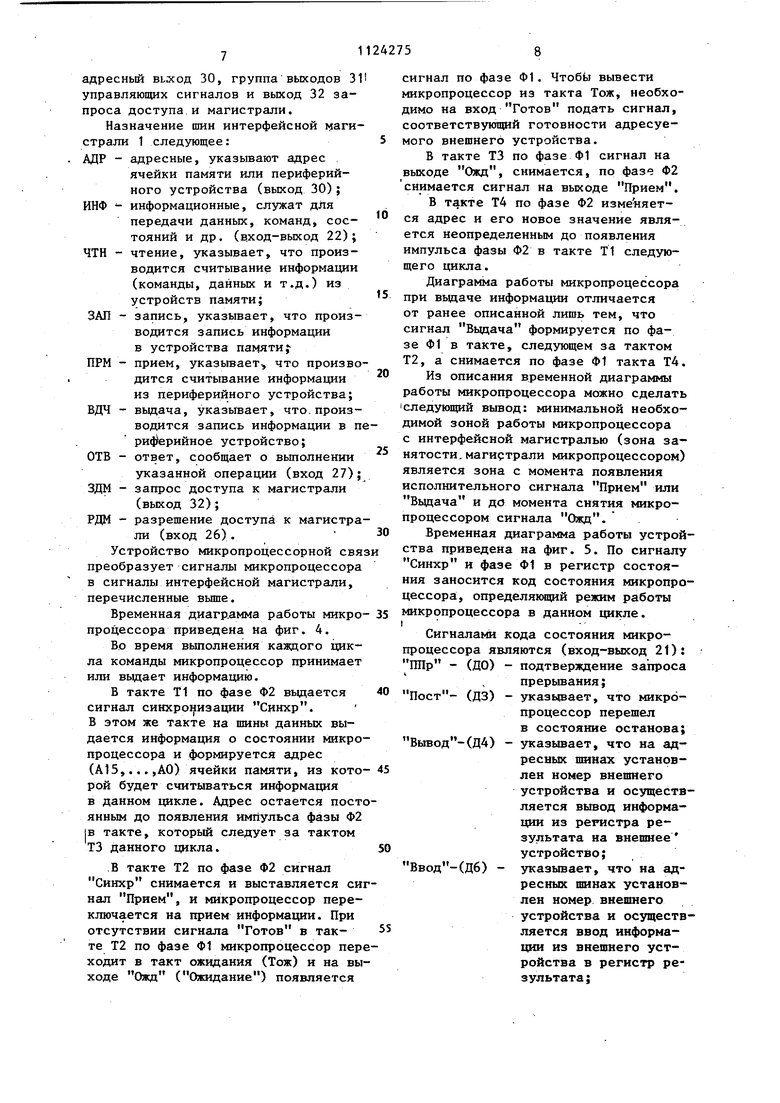

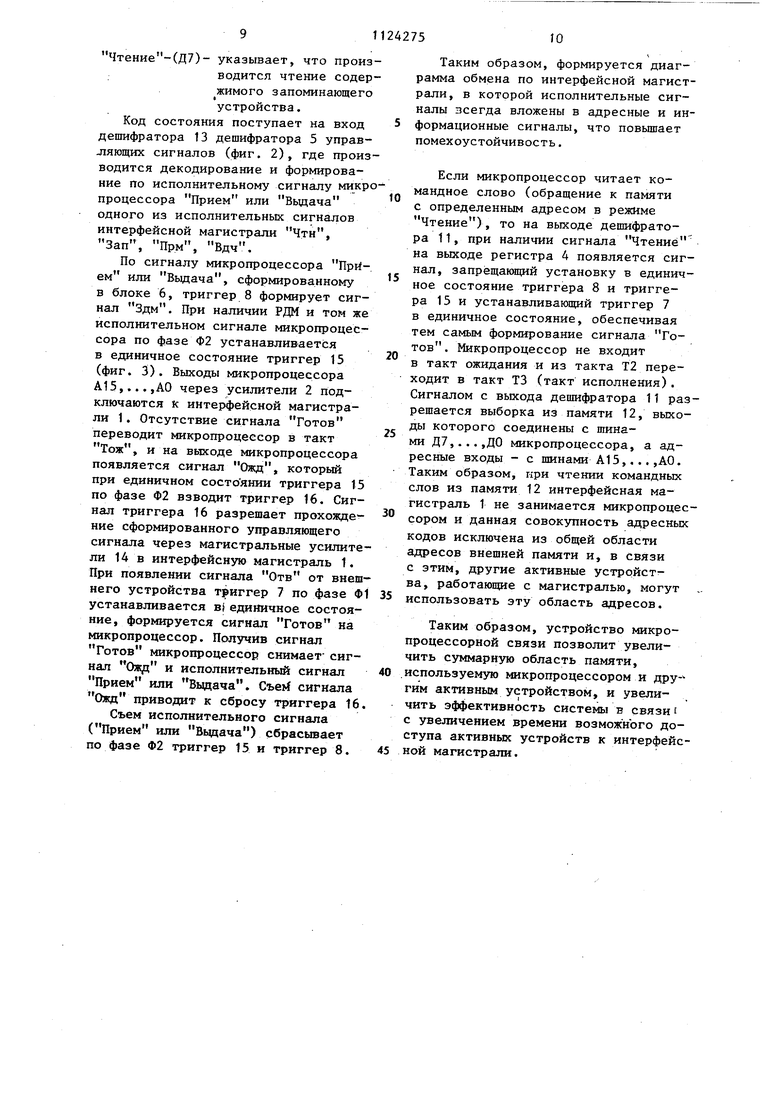

На чертежах обозначены также адресный вход 20 устройства, первый 21 и второй 22 информационные входы-выходы устройства, вход 23 синхронизагщи, вход 24 сигнала ожидания и вход 25 режима, вход 26 разрешения доступа к магистрали и вход 27 сигнала ответа устройства, выход 28 готовности, выход 29 синхронизации. адресный вьход 30, группа выходов 3 управляющих сигналов и выход 32 запроса доступа.и магистрали. Назначение шин интерфейсной магистрали 1 следующее: АДР - адресные, указывают адрес . ячейки памяти или периферийного устройства (выход 30); ИНФ - информационные, служат для передачи данных, команд, состояний и др. (эход-выход 22); ЧТН - чтение, указывает, что производится считывание информации (команды, данных и т.д.) из устройств памяти; ЗАЛ - запись, указывает, что производится запись информации в устройства памятиf ПРМ - прием, указывает, что произво дится считывание информации из периферийного устройства; ВДЧ - выдача, указывает, что.производится запись информации в п ри4 ерийное устройство; ОТВ - ответ, сообщает о выполнении указанной операции (вход 27) ЗДМ - запрос доступа к магистрали (выход 32); РДМ - разрешение доступа к магистра ли (вход 26). Устройство микропроцессорной свя преобразует сигналы микропроцессора в сигналы интерфейсной магистрали, перечисленные выше. Временная диаграмма работы микро процессора приведена на фиг. 4. Во время выполнения каждого цикла команды микропроцессор принимает или вьщает информацию. В такте Т1 по фазе Ф2 вьщается сигнал синхронизации Синхр. В этом же такте на шины данных выдается информахщя о состоянии микро процессора и формируется адрес (А15,...,АО) ячейки памяти, из кото рой будет считываться информация в данном цикле. Адрес остается пост янным до появления импульса фазы Ф2 IB такте, который следует за тактом ТЗ данного цикла. ,В такте Т2 по фазе Ф2 сигнал Синхр снимается и выставляется си нал Прием, и микропроцессор переключается на прием информации. При отсутствии сигнала Готов в такте Т2 по фазе Ф1 микропроцессор пер ходит в такт ожидания (Тож) и на вы ходе Ожд (Ожидание) появляется сигнал по фазе Ф1. Чтобы вывести микропроцессор из такта Тож, необходимо на вход Готов подать сигнал, соответствующий готовности адресуемого внешнего устройства. В такте ТЗ по фазе Ф1 сигнал на выходе Ожд, снимается, по фазе Ф2 снимается сигнал на выходе Прием. В такте Т4 по фазе Ф2 изменяется адрес и его новое значение является неопределенным до появления импульса фазы Ф2 в такте 11 следующего цикла. Диаграмма работы микропроцессора при вьдаче информации отличается от ранее описанной лишь тем, что сигнал Вьщача формируется по фазе Ф1 в такте, следующем за тактом Т2, а снимается по фазе Ф1 такта Т4. Из описания временной диаграммы работы микропроцессора можно сделать следующий вывод: минимальной необходимой зоной работы микропроцессора с интерфейсной магистралью (зона занятости, магистрали микропроцессором) является зона с момента появления исполнительного сигнала Прием или Вьщача и до момента снятия микропроцессором сигнала Ожд. Временная диаграмма работы устройства приведена на фиг. 5. По сигналу Синхр и фазе Ф1 в регистр состояния заносится код состояния микропроцессора:, определяющий режим работы микропроцессора в данном цикле. I - Сигналаьт кода состояния микропроцессора являются (вход-выход 21): ШТр - (ДО) - подтверждение запроса , прерывания; (ДЗ) - указывает, что микропроцессор перешел в состояние останова; Вывод -(Д4) - указывает, что на адресных шинах установлен номер внешнего устройства и осуществляется вывод информации из регистра результата на внешнее устройство; (Дб) - указывает, что на адресных шинах установлен номер внешнего устройства и осуществляется ввод информации из внешнего устройства в регистр результата ; Чтение -(Д7)- указывает, что произ водится чтение содер жимого запоминающего устройства. Код состояния поступает на вход дешифратора 13 дешифратора 5 управляющих сигналов (фиг. 2), где произ водится декодирование и формирование по исполнительному сигналу микр процессора Прием или Выдача одного из исполнительных сигналов интерфейсной магистрали Чтн, Зап, Прм. Вдч. По сигналу микропроцессора Прием или Вьщача, сформированному в блоке 6, триггер 8 формирует сигнал Здм, При наличии РДМ и том же исполнительном сигнале микропроцессора по фазе Ф2 устанавливается в единичное состояние триггер 15 (фиг. 3). Выходы микропроцессора А15,...,АО через усилители 2 подключаются к интерфейсной магистрали 1. Отсутствие сигнала Готов переводит микропроцессор в такт Тож, и на выходе микропроцессора появляется сигнал Ожд, который при единичном состоянии триггера 15 по фазе Ф2 взводит триггер 16. Сигнал триггера 16 разрешает прохождение сформированного управляющего сигнала через магистральные усилите ли 14 в интерфейсного магистраль 1. При появлении сигнала Отв от внеш него устройства триггер 7 по фазе Ф устанавливается в| единичное состояние, формируется сигнал Готов на микропроцессор. Получив сигнал Готов микропроцессор снимает- сигнал Ожр и исполнительный сигнал Прием или Ввдача. Съе сигнала Ожд приводит к сбросу триггера 16 Съем исполнительного сигнала (Прием или Вьщача) сбрасывает по фазе Ф2 триггер 15 и триггер 8. Таким образом, формируется диаграмма обмена по интерфейсной магистрали, в которой исполнительные сигналы всегда вложены в адресные и информационные сигналы, что повьшает помехоустойчивость. Если микропроцессор читает командное слово (обращение к памяти с определенным адресом в режиме Чтение), то на выходе дешифратора 11, при наличии сигнала Чтение на выходе регистра 4 появляется сигнал, запрещающий установку в единичное состояние триггера 8 и триггера 15 и устанавливающий триггер 7 в единичное состояние, обеспечивая тем самым формирование сигнала Готов. Микропроцессор не входит в такт ожидания и из такта Т2 переходит в такт ТЗ (такт исполнения). Сигналом с выхода дешифратора 11 разрешается выборка из памяти 12, выходы которого соединены с шинами Д7,...,ДО микропроцессора, а адресные входы - с шинами А15,...,АО. Таким образом, при чтении командных слов из памяти 12 интерфейсная магистраль 1 не занимается микропроцессором и данная совокупность адресных кодов исключена из общей области адресов внешней памяти и, в связи с зтим, другие активные устройства, работающие с магистралью, могут использовать эту область адресов. Таким образом, устройство микропроцессорной связи позволит увеличить суммарнзто область памяти, используемую микропроцессором и другим активным устройством, и увеличить эффективность системы Е связиi с увеличением времени возможного доступа активных устройств к интерфейсной магистрали.

7

fPut.l

26

15

прием, Bbidat/a

25

Ог9лока11

Фиг. 2

К 5локу 8

К5локан2

& 77

fS

КЬлокуЗ

2LO-M Ф1,Ф2 29

Такты пикропроцесса

Ф1 Ф2

АГ5-АО

СИНХР

ПРнеп

готов

BbmttA ожд

Фиг л

Фиг, 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Балашов Е.П., Пузанков Д.В | |||

| Микропроцессоры и микропроцессорные системы | |||

| М., Радио и связь, 1981, с | |||

| Ротационный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию, и т.п. работ | 1924 |

|

SU204A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-01—Подача