Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов (СОК), а также в аппаратуре передачи данных использующей коды СОК.

Целью изобретения является повышение быстродействия.

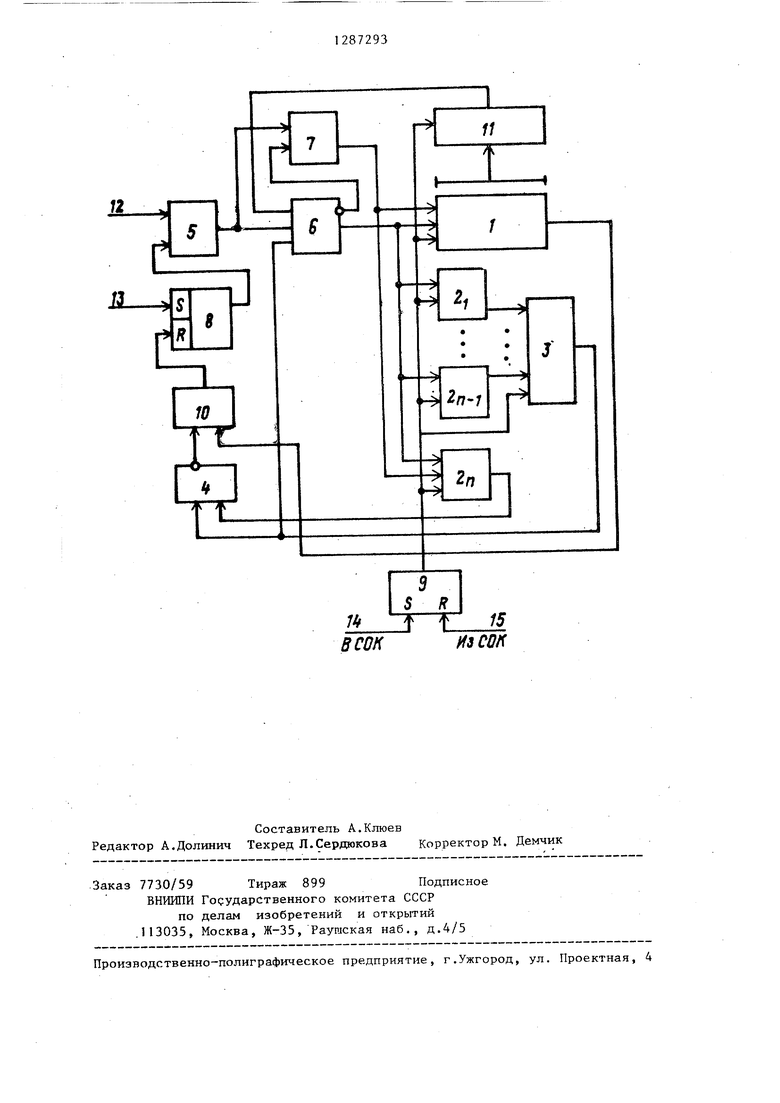

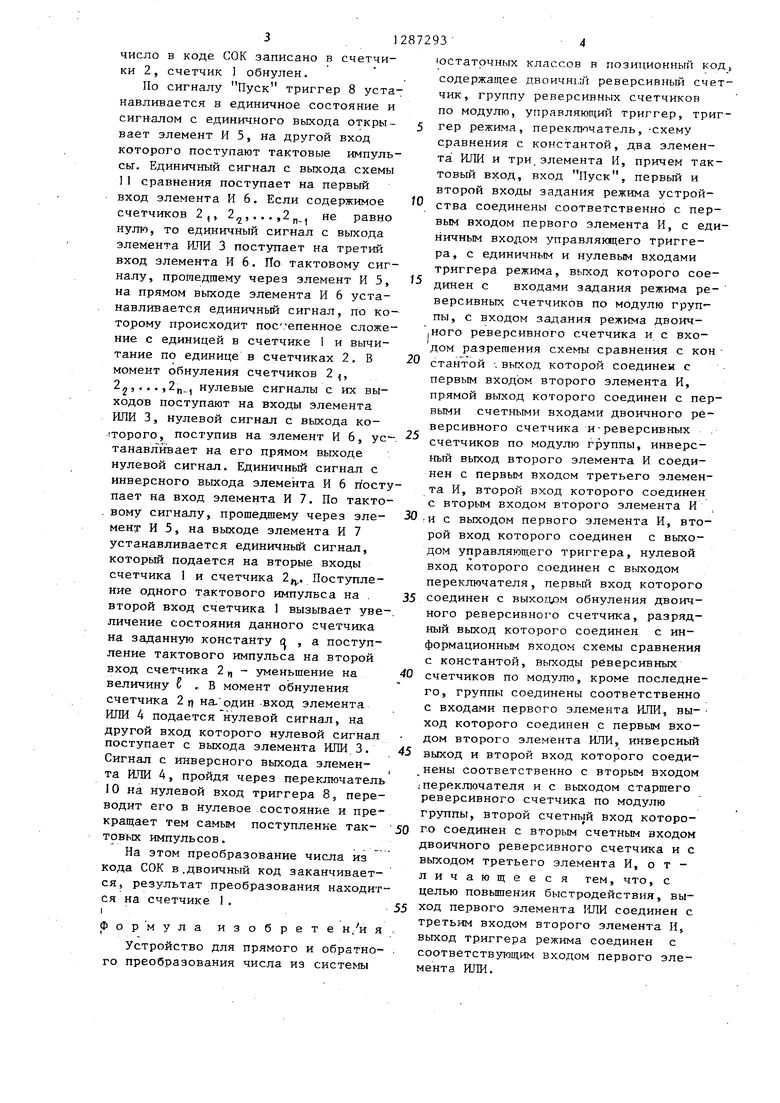

На чертеже представлена схема уст ройства для прямого и обратного преобразования числа из системы остаточных классов в позиционный код.

Устройство для прямого и обрат - ного преобразования числа из системы остаточных классов в позиционньш код содержит двоичный реверсивный счетчик 1, группу реверсивных счетчиков 2,- 2 J, по модулю, элементы ИЛИ 3, 4, элементы И 5-7, управляющий триггер 8, триггер 9 режима, переключатель 10, схему II сравнения с константой, тактовый вход 12, вход 13 Пуск устройства, входы 14 и 15 задания режима устройства.

Двоичный реверсивный счет чик 1 позволяет увеличивать или уменьшать содержащееся в нем число на единицу

константу

или заданную для него

п-1 i- „

q п р, {реверсивньш модульный счет0 ;« .

1М

ЧИК

нем число

2 у, - изменять

содержащееся в на единицу или заданную

П-1

для него константу

/,1

mod Р,

При обнулении каждого из модульных реверсивных счетчиков 2 и двоичного реверсивного счетчика 1 с его выхода выдается сигнал логического нуля. Каждый из модульных счетчиков 2, 2j,,,,, 2„ производит счет по модуле соответствующего основания СОК. - Схе;- а -11 сравнения вьтолняет срав нение с константой о.

Устройство для прямого и обрат - ного преобразования числа из системы остаточных классов в позиционный код работает следующим образом.

Вход 14, сигнал на который подает ся при преобразовании числа из двоичного кода в код СОК, подключен к единичному входу триггера 9. Сигнал, пришедший на вход 14, переключает триггер 9 в единичное состояние, и сигнал с его выхода подготавливает двоичный реверсивный счетчик 1 к ра- боте в режиме .Вычитание, счетчики 2 - к работе в режиме Сложение..

0

5

0

5

0

5

0 5

Преобразуемое число в двоичном коде записано в счетчике 1, счетчики 2 обнулены. Сигнал, приходящий на вход 13 Пуск, устанавливает триггер 8 в единичное состояние, сигналом с единичного выхода которого открьшается элемент И 5 по второму , входу, на первый вход которого поступают тактовые импульсы.

Единичный сигнал с выхода элемента ИЛИ 3 поступает на третий вход элемента И 6. Если содержимое счетчика 1 больше или равно величине константы, то нулевой сигнал с выхода схемы 11 сравнения, пройдя через первый вход элемента И 6, устанавливает на его прямом вьсходе нулевой сигнал. Единичный сигнал с инверсного выхода элемен та И 6 подается на первый вход элемента И 7. По тактовому сигналу, прошедшему через элемент И 5, на выходе элемента И 7 устанавливается единичньй сигнал. При этом по единичному сигналу с выхода элемента И 7 происходит постепенное вь1читание константы CJ в счетчике 2 и сложение с константой 6 в счетчике 2п. Когда содержимое снетчи- ка 1 станет меньше величины « , на выходе схемь 11 сравнения будет единичный сигнал, что в свою очередь вызывает при наличии тактового им- Нульса единичный сигнал на прямом .... выходе элемента И 6 и нулевой сигнал на выходе элемента И 7. По единичному сигналу с выхода элемента И 6 происходит постепенное вычитание по единице в счетчике 1 и сложение с единицей в счетчиках 2. В момент обнуления счетчика 1 с его выхода выдается сигнал, который пройдя через переключатель 10, переводит триггер 8 в нулевое состояние. При этом прекращается поступление тактовых импульсов .

В счетчиках 2 зарегистрирован код СОК, соответствующий двоичному коду, первоначально записанному в счетчике 1.

Вход 15 при преобразовании числа из кода СОК в двоичный код подключен к нулевому входу триггера 9, сигнал с выхода которого поступает на вход элемента ИЛИ 3, а также устанавливает выход схемы 11 сравнения в единичное состояние и подготавливает счетчик 1 к работе в Сложение, а счетчики 2 к работе в режиме Вычитание. Преобразуемое

31287293

исло в коде СОК записано в счетчии 2 , счетчик обнулен.

По сигналу Пуск триггер 8 устаавливается в единичное состояние и игналом с единичного выхода открыает элемент И 5, на другой вход оторого поступают тактовые импульы. Единичный сигнал с выхода схемы 1 сравнения поступает на первый ход элемента И 6. Если содержимое

Ш

(о с ч по г ср та то вт ст вы ни ра тр ди ве пы ,но до ст пе пр вы ве сч ны не та с и ро до вх пе со но ны фо с сч го с хо до вы не пе ре гр го дв вы л цел

(

,2 не равно

счетчиков 2

нулю, то единичный сигнал с выхода элемента ИЛИ 3 поступает на третий вход элемента И 6. По тактовому сигналу, прошедшему через элемент И 5, на прямом выходе элемента И 6 устанавливается единичный сигнал, по которому происходит пос . епенное сложение с единицей в счетчике 1 и вычитание по единице в счетчиках 2. В момент обнуления счетчиков 2 ,, 2.,., .,2 I нулевые сигналы с их выходов поступают на входы элемента ИЛИ 3, нулевой сигнал с выхода ко- tToporo, поступив на элемент И 6, ус- танавхГй;вает на его прямом выходе нулевой сигнал. Единичньй сигнал с инверсного выхода элемента И 6 riocry пает на вход элемента И 7. По тактовому сигналу, прошедшему через элемент И 5, на выходе элемента И 7 устанавливается единичный сигнал, который подается на вторые входы счетчика 1 и счетчика 2,. Поступле

ние одного тактового импулвса на . второй вход счетчика 1 вызывает увеличение состояния данного счетчика на заданную константу о , а поступление тактового импульса на второй вход счетчика 2 - уменьшение на величину С . В момент обнуления счетчика 2 г на. один -вход элемента ИЛИ 4 подается нулевой сигнал, на другой вход которого нулевой сигнал поступает с выхода элемента ИЛИ 3. Сигнал с инверсного выхода элемента ИЛИ 4, пройдя через переключатель 10 на нулевой вход триггера 8, переводит его в нулевое состояние и прекращает тем самым поступление так- товых импульсов.

На этом преобразование числа из кода СОК в.двоичный код заканчивается, результат преобразования находится на счетчике I. I

Формула изобретен, и я

Устройство для прямого и обратного преобразования числа из системы

Ш

J5

0

-5

(остаточных классов в позиционный код, содержащее двоичньа реверсивный счетчик, группу реверсивных счетчиков по модулю, управляющий триггер, триггер режима, переключатель, -схему сравнения с константой, два элемента ИЛИ и три,элемента И, причем тактовый вход, вход Пуск, первый и второй входы задания режима устройства соединены соответственно с первым входом первого элемента И, с единичным входом управляющего триггера, с единичным и нулевым входами триггера режима, выход которого соединен с входами задания режима реверсивных счетчиков по модулю группы, с входом задания режима двоич- ,ного реверсивного счетчика и с вхо- дом разрешения схеьпзг сравнения с кон стантой , выход которой соединен с первым входом второго элемента И, прямой выход которого соединен с первыми счетными входами двоичного реверсивного счетчика и-реверсивных счетчиков по модулю группы, инверсный выход второго элемента И соединен с nepBbtM входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента И и с выходом первого элемента И, второй вход которого соединен с выходом управляющего триггера, нулевой вход которого соединен с выходом переключателя, первый вход которого соединен с выходрм обнуления двоичного реверсивного счетчика, разрядный выход которого соединен с информационным входом схемы сравнения с константой, выходы реверсивных счетчиков по модулю, кроме последнего, группы соединены соответственно с входами первого элемента ИЛИ, вы- ход которого соединен с первым входом второго элемента ИЛИ, инверсный выход и второй вход которого соединены соответственно с вторым входом переключателя и с выходом старшего реверсивного счетчика по модулю группы, второй счетнь1й вход которого соединен с вторым счетным входом двоичного реверсивного счетчика и с выходом третьего элемента И, о т - личающееся тем, что, с целью повышения быстродействия, вы5 ход первого элемента ИЛИ соединен с третьим входом второго элемента И, выход триггера режима соединен с

соответствующим входом первого элемента ИЛИ.

0

5

0

5

0

BOOK

Составитель А.Клюев Редактор А.Долинич Техред Л.Сердюкова Корректор М. Демчик

Заказ 7730/59 Тираж 899Подписное

ВНИШ1И Государственного комитета СССР по делам изобретений и открытий

.113035, Москва, Ж-35, Раушская наб., д.4/5

---.--..-..

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

и SCO к

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код | 1982 |

|

SU1075254A1 |

| Устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код | 1983 |

|

SU1089573A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1985 |

|

SU1290536A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1984 |

|

SU1257850A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Вычислительное устройство для диагностики заболеваний | 1984 |

|

SU1238105A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов (сок), а также в аппар.атуре передачи данных, использующей коды СОК. Целью изобретения является повьтение быстродействия. Поставленная цель достигается за счет новой организации связей в устройстве, содержащем двоичный реверсивный счетчик,группу . реверсивных счетчиков по модулю, триггер режима, управляющий триггер, переключатель, схему сравнения с константой, два элемента ИЛИ и три элемента И. 1 ил. с € (Л

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1984 |

|

SU1200429A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код | 1982 |

|

SU1075254A1 |

Авторы

Даты

1987-01-30—Публикация

1985-09-25—Подача