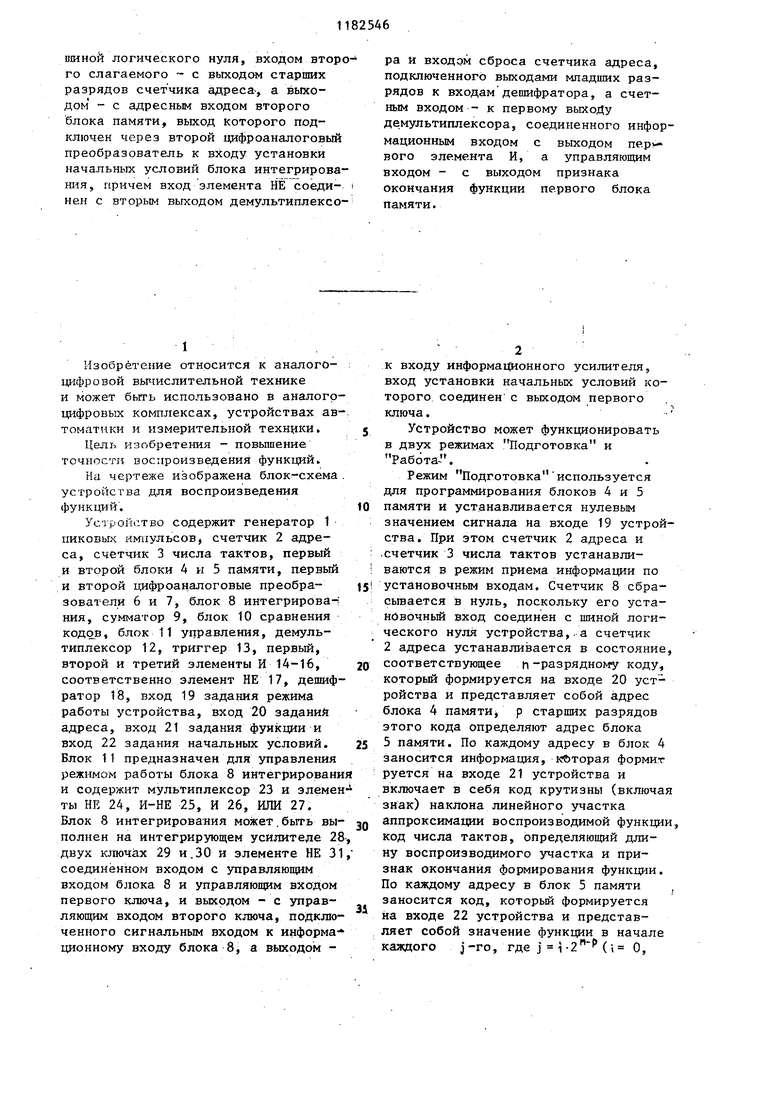

пшной логического нуля, входом второго слагаемого с выходом старших разрядов счетчика адреса-, а выходом - с адресным входом второго блока памяти, выход которого подключен через второй цифроаналоговый преобразователь к входу установки начальных условий блока интегрирования, причем вход элемента НЕ соединей с вторым выходом демультиплексора и входом сброса счетчика адреса, подключенного выходами младших разрядов к входамдешифратора, а счетным входом - к первому выхоДу демультиплексора, соединенного инфомационным входом с выходом nepvвого элемента И, а управляющим входом - с выходом признака окончания функции первого блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Формирователь сложных сигналов | 1983 |

|

SU1153391A1 |

| Устройство для воспроизведения запаздывающих функций | 1984 |

|

SU1168973A1 |

| Устройство для реализации булевых функций | 1986 |

|

SU1310801A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для решения обратных задач теории поля | 1984 |

|

SU1164748A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

УСТРОЙСТВО ДЛЯ ВОСПРСИЗВЕДЕШ-1Я ФУНКЦИЙ, .содержащее блок управле ния, счетчик адреса, подключенный выходом к адресному входу первого блока памяти,- соединенного выходом кода крутизны с входом первого цифроаналогового преобразователи, а выходом кода длительности участка аппроксимадии - с первым входом блока сравнения кодов, подключенного вторым входом к выходу счетчика числа тактов, а выходом - к информационному входу триггера, соединенного синхронизирующим входом с выходом генератора тактовых и myль- сов и с первыми входами первого и второго элементов И, подключенных вторыми входами к прямому и инверсному выходам триггера соответственно, вь1ход первого элемента И соединен с входом сброса счетчика числа тактов, счетный вход которого подключен к выходу второго элемента И, а выход первого цифроаналогового преобразователя соединен с информационным входом блока интегрирования, выход которого подключен к выходу устройства, причем блок управления содержит элементы НЕ, ИтНЕ и мультиплексор, соединенный выхоД рм с входом управления режимом работы блока интегрирования, а первым информационным входом - с выходом элемента НЕ блока управления, подключенного входом к входу задания режима работы, устройства и к входам управления устан овкой кода счетчика .адреса и счетчика цикла тактов отличающееся тем, что, с целью повышения точности воспроизведения функций, в него дополнительно введены второй цифроапалоговый преобразователь, второй блок памяти, сумматор, дешифратор демультиплексор, элемент НЕ и третий элемент И, а блок управления дополнительно содержит элемент ИЛИ и fi элемент И, соединенньй входами с вым выходом демультиплексора и выходом дешифратора, а выходом - с первьм входом элемента ИЛИ блока управ00 ления, подключенного вторым входЬм tc к второму выходу -демультиплексора, СП а выходом - к первому.входу элемента 4 Од И-НЕ блока управления, соединенного выходом с управляющим входом мультиплексора блока управле1шя, а вторым входом - с вторым информационным входом мультиплексора блока управления, входом задания режима работы устройства, управляющим входом генератора тактовых импульсов и первьм входом третьего элемента И, подключенного вторым входом к ,выхрд5; элемента НВ, а выходом- к младшему разряду входа первого слагаемого сумматора, соединенного остальными разpядa iи входа первого слагаемого с

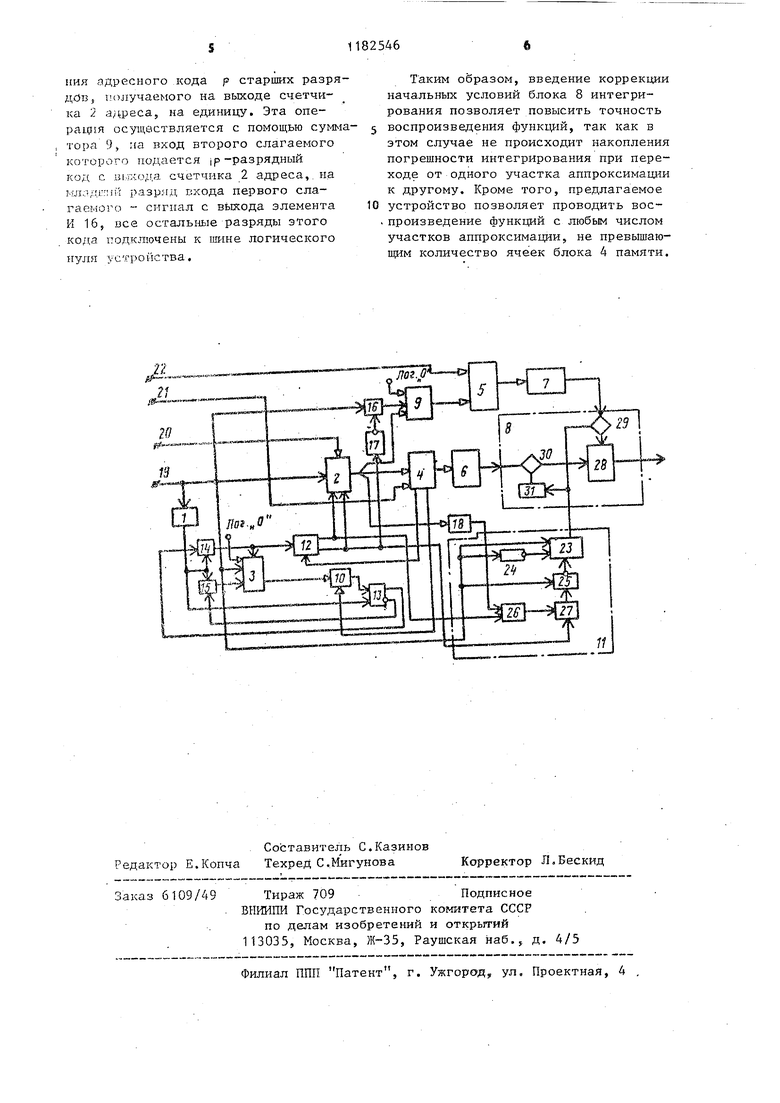

Изобретение относится к аналогецифровой вычислительной технике и может быть использовано в аналогоцифровых комплексах, устройствах автематики и измерительной техники. Цель изобретения - повьппение точности Боспроизведения функций. На чертеже изображена блок-схема устройства для воспроизведения функций, Устройство содержит генератор 1 пиковых импульсов, счетчик 2 адреса, счетчик 3 числа тактов, первый и второй блоки 4 и 5 памяти, первый и второй цифроаналоговые преобразователи 6 и 7, блок 8 интегрирова-; ния, сумматор 9, блок 10 сравнения кодов, блок 11 управления, демультиплексор 12, триггер 13, первый, второй и третий элементы И 14-16, соответственно элемент НЕ 17, дешиф ратор 18, вход 19 задания режима работы устройства, вход 20 заданий адреса, вход 21 задания функции и вход 22 задания начальных условий. Блок 11 предназначен для управления режимом работы блока 8 интегрировани и содержит мультиплексор 23 и элеме ты НЕ 24, И-НЕ 25, И 26, ИЛИ 27. Блок 8 интегрирования может.быть вы полнен на интегрирующем усилитеде 2 двух клпочах 29 и.30 и элементе НЕ 3 соединённом входом с управляющим входом блока 8 и управляющим входом первого ключа, и выходом - с управляющим входом второго ключа, подклю ченного сигнальным входом к информа ционному входу блока 8j а выходо1м к входу информа1 онного усилителя, вход установки начальных условий которого соединен с выходом первого ключа.Устройство может функционировать в двух режимах Подготовка и Работа.. Режим Подготовка используется для программирования блоков 4 и 5 памяти и устанавливается нулевым значением сигнала на входе 19 устройства . При этом счетчик 2 адреса и .счетчик 3 числа тактов устанавливаются в режим приема информации по установочным входам. Счетчик 8 сбрасьгаается в нуль, поскольку его установочньй вход соединен с Ш1ной логического нуля устройства,.а счетчик 2 адреса устанавливается в состояние, соответствующее п-разрядному коду, который формируется на входе 20 устройства и представляет собой адрес блока 4 памяти, р старших разрядов этого кода определяют адрес блока 5 памяти. По каждому адресу в блок 4 заносится информация, которая формит руется на входе 21 устройства и включает в себя код крутизны (включая знак) наклона линейного участка аппроксимации воспроизводимой функции, код числа тактов, определяющий длину воспроизводимого участка и признак окончания формирования функции. По каждому адресу в блок 5 памяти , заносится код, который формируется на входе 22 устройства и представляет собой значение функции в начале каждого j-ro, где j (i О, 1, 2,..., 2 ), участка аппроксимации. По окончанию программирования блоков 4 и 5 памяти счетчик 2 адреса сбрасьгоается в нулевое состояние При этом нулевой сигнал на выходе блока 11 управления разрешает запись содержимого нулевой ячейки блока 5 памяти, которое является начальным значением воспроизводимой функции, преобразованного в аналоговую форму цифроаналоговым преобразователем 7, в блок 8 интегрирования. Режим Работа -устанавливается единичны значением сигнала на входе 19 устройства. Генератор 1 тактовых импульсов синхронизируется сигналом на входе 19 устройства таким образом, что момент появления единич ного сигнала на входе 19 соответству ет началу паузы между тактовыми импульсами. При этом счетчики 2 и 3 переводятся в счетный режим, а блок 8 - в режим Интегрирование (первый ключ закрыт, а второй ключ открыт). Код крутизны из нулевой ячей блока 4 памяти поступает на вход циф роаналогового преобразователя 6, и на выходе устройства формируется первьш участок аппроксимации временной функции. Длительность участка аппроксимации кратна периоду следования тактовых импульсов и задается (-разрядным кодом с соответствующего выхода блока 4 памяти, подаваемым на первый вход блока 10 сравнения. Если при этом на данном выходе блока 4 памяти формируется код 00 (при 2), совпадающий с выходным кодом счетчика 3, то на выходе блока 10 сравнения появляется сигнал логической единицы. С приходом тактового импульса на прямом выходе триггера 13 появляется сигнал логической единицы, которьй .открьтает элемент И 14, а на инверсном выходе - сигнал логического нуля , который закрывает элемент И 15 Тактовы импульс проходит через элемент И 14 и подтверждает нулевое состояние счетчика 3.. Если на выходе признака окончания функции блока 4 памяти стоит нуль, то тактовый импульс про дит на первый выход демультиплексор 12 и, постзтая на счетный вход счет чика 2, увеличивает его выходной код на единицу. Если же на )cj,-разр ном выходе блока 4 памяти формирует ся код, отличный от нуля, то на вы16 10 сравнения прявляет.:я ходе блока сигнал логического нуля, что приводит к сбросу триггера 13 очередным тактовым импульсом. При этом элемент И 14 закрывается, а элемент И 15 открьшается, и тактовые импульсы начинают поступать на счетный вход счетчика 3 до тех пор, пока его выходной код не станет равным коду длительности участка аппроксимации. Совпадение этих кодовприводит к очередному перебрасыванию триггера 13, .в результате чего счетчик 3 сбрасьгоается в нуль, а адрес на выходе счетчика 2 увеличивается на единицу. При появлении единичного сигнала на выходе признака окончания формирования функции блока 4 памяти очередной тактовьй импульс с выхода элемента И 14 проходит на второй выход демультиплексора 12, что приводит к сбросу счетчика 2 адреса. Одновременно этот импульс поступает через элемент ИЛИ 27 и элемент И-НЕ 25 блока 11 на управляющий вход мультиплексора 23, а также формирует нулевой сигнал на выходе первого слагаемого сумматора 9. При этом к выходу мультиплексора 23 подключается его первый информационный вход, и на выходе блока 11 управления формируется сигнал лoгичedкого нуля, по-длительности равный длительности тактового импульса, который переводит блок 8 интегрирования в режим приема начальных условий, и в интегратор блока 8 вновь записьшается содержимое нулевой ячейки блока 5 памяти, которое является начальным значением воспроизводимой функции, после чего процесс воспроизведения функции повторяется. Коррекция начальньЬс условий ин-с тегратора блока 8 осуществляется после формирования каждых,. 2 участков аппроксимации следующим образом. Дешифратор 18 вьфабдтывает единичный сигнал, если на его вход подается код Все единицы в виде (n-fi ) младших разрядов-адресного кода. При этом тактовый импульс с первого выхода демультиплексора 12 проходит через элементы И 26, ИЛИ 27, И-НЕ 25 и формирует на выходе блока 11 сигнал логического нуля, переводя блок 8 в режим приема начальных условий. Требуемый адресный код блока 5 памяти формируется путем увеличеПИЯ адресного кода р старших разря д-Ов, ьолучаемого на выходе счетчика 2 адреса, на единицу. Эта опеpaipiH осуществляется с помощью сумм тора 9, иа вход второго слагаемого которого подается ip-разрядный код с иияод.а счетчика 2 адреса,, на Mjj.;i.it,i-r;) разряд входа первого слагаемого - сигнал с вькода элемента К 16, все остальные разряды этого кода гтодключены к шине логического нуля устройства. Таким образом, введение коррекции начальных условий блока 8 интегрирования позволяет повысить точность воспроизведения функций, так как в этом случае не происходит накопления погрешности интегрирования при перекоде от одного участка аппроксимации к другому. Кроме того, предлагаемое устройство позволяет проводить воспроизведение функций с любым числом участков аппроксимации, не превьшающим количество ячеек блока 4 памяти.

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 0 |

|

SU389519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный генератор | 1977 |

|

SU746581A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1984-04-21—Подача