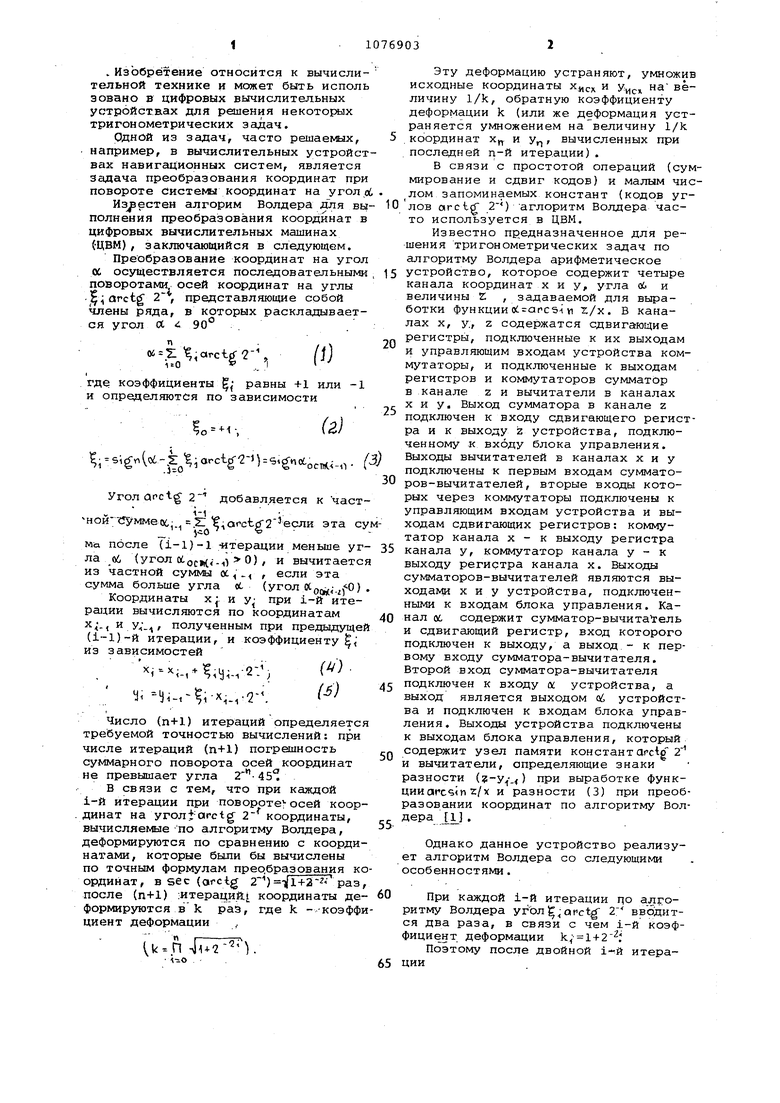

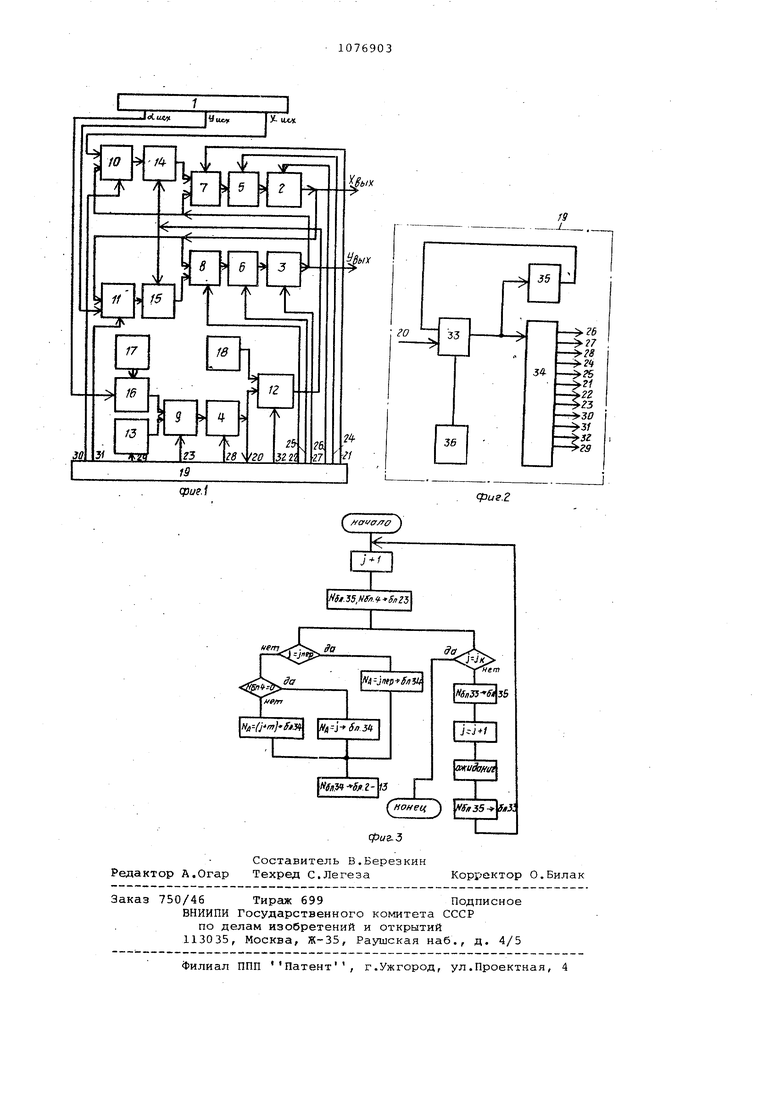

. Изобретение относится к вычислительной технике и может быть исполь эовано в цифровых вычислительных устройствах для решения некоторых тригонометрических задач. Одной из задач, часто решае№1х, например, в вычислительных устройст вах навигационных систем, является Зсшача преобразования координат при повороте Системы координат на угол о Известен алгорим Волдера для вы полнения преобразования координат в цифровых вычислительных машинах (ЦВМ) , заключающийся в следующем. Преобразование координат на угол Oi осуществляется последовательными поворотами, осей координат на углы arctg 2 , представляющие собой члены ряда, в которых раскладывается угол Л 4 90° .. .,a. fjj где коэффициенты равны +1 или -1 и определяются по зависимости fo-1-, ,slg4oi-k,arctg-2-ib g: ot,.,, - ( Угол arc tg- добавляется к част Йуммеоб. .ZI,агсЪ 2если эта су ма после {i-l)-l -итерации меньше уг ла об (угол otQf,-.,) 0) , и вычитаетс из частной сумим . , если эта сумма больше угла Л (угол 1)С(,-.,0) Координаты X . и при i-й итершдии вычисляются по координатам х., и у;., полученным при предыдущей (1-1)-й итерации, и коэффициенту из зависимостей ,,.-2-;; У. Ч.-,,-х,.,.Г Число (п+1) итераций определяется требуемой точностью вычислений: при числе итераций (п+1) пограчность суммарного поворота осей координат не превышает угла 45 В связи с тем, что при каждой i-й итерации при повороте осей координат на yгoлiaгctg 2 координаты, вычисляемые-по алгоритму Волдера, деформируются по сравнению с координатами, которые были бы вычислены по точным формулам преобразования ко ординат, в sec (arctg )-/1+Т раз после (п+1) :итераций. координаты деформируются в k раз, где k --коэффи циент деформации и П iJi + 2 Эту деформацию устраняют, умножив исходные координаты я УИС« личину 1/k, обратную коэффициенту деформации k (или же деформация устраняется умножением на величину 1/k координат Xfy и УГ, , вычисленных при последней п-й итерации). В связи с простотой операций (суммирование и сдвиг кодов) и малым запоминаемых констант (кодов углов arctg ) аглоритм Волдера часто используется в ЦВМ. Известно предназначенное для решения тригонометрических задач по алгоритму Волдера арифметическое устройство, которое содержит четыре канала координат х и у, угла и и величины Z , задаваемой для выработки функции (-аГС54 и z/x. В каналах X, у., Z содержатся сдвигающие регистры, подключенные к их выходам и управляющим входам устройства коммутаторы, и подключенные к выходам регистров и коммутаторов сумматор в канале z и вычитатели в каналах X и у. Выход сумматора в канале z подключен к входу сдвигающего регистра и к выходу z устройства, подключенному к входу блока управления. Выходы вычитателей в каналах х и у подключены к первым входам сумматоров-вычитателей, вторые входы которых через коммутаторы подключены к управляющим входам устройства и выходам сдвигающих регистров: коммутатор канала х - к выходу регистра канала у, коммутатор канала у - к выходу регистра канала х. Выходы сумматоров-вычитателей являются выходал1и X и у устройства, подключенными к входам блока управления. Канал и. содержит сумматор-вычитагель и сдвигающий регистр, вход которого подключен к выходу, а выход - к первого входу сумматора-вычитателя. Второй вход сумматора-вычитателя подключен к входу у. устройства, а выход является выходом об устройства и подключен к входам блока управления. Выходы устройства подключены к выходам блока управления, который содержит узел памяти констант arctg 2 и вычитатели, определяющие знаки разности (.) при выработке функции arc п z/x и разности (3) при преобразовании координат по алгоритму Волдера 11 . Однако данное устройство реализует алгоритм Волдера со следующими особенностями. При каждой 1-й итерации по алгоритму Волдера 2: вводится два раза, в связи с чем i-й Коэффициент деформации k; l + Поэтому после двойной итерации--.н ,н2 Ч,М.н(,-„-2- , где X. , у - недеформированные координаты, которые был бы выработаны после этой- итерации по точным формулам преобразования координат. При каждой итерации в каждом из каналов деформация устраняется тем, что в сумматор и вычитатели из сдви гающих регистров вводягся как сама координата, так и t (через коммутатор) эта же координата, сдвинутая вправо на 1 разрядов, причем благодаря выполнению итерации два раза полный сдвиг координаты вправо происходит на 21 разрядов. Сдвинутая на 21 разрядов вправо координата вы читается из несдвинутой координаты, деформированной после выполнения преобразования по алгоритму Волдера и содержащей дополнительное деформи рующее координату слагаемое х- -2 или у, - 2Ч Вычитание из деформированной координаты указанной (сдви нутой на 21 разрядов вправо) устраняет деформацию. Кроме, того, реализация трех зави симостей (3) - (5) алгоритма Волдера производится не в одном вычислительном блоке, а в трех параллельно работающих каналах х, у и к, (канал Z при решении задачи преобразования координат не используется). Однако время вычисления увеличивается изт за устранения деформации не один раз, а (п+1) раз - при каждой итера ции, причем итерации в устройстве двоичные. Таким образом, данное устройство характеризуется низким быстродействием. Известно также устройство для вычисления значений координат : вектора, содержащее три канала х, у и 0 , выходы которых являются вы ходами устройства. Каждый канал содержит сумматор-вычитатель и сдвига щий регистр, вход которого подключен к выходу своего сумматора-вычитателя, а выход - к входу этого сум матора- вычитателя, второй вход кото рого в каналах х и у через коммутатор подключен к выходам сдвигающего регистра другого канала, Второй вход сумматора-вычитателя канала об подключен к выходу четвертого сдвигающего регистра, входы которого подключены к выходам блока памят констант и элемента И. Входы элемен та И подключены к выходам четв ртого сдвигающего регистра и управляющ .му входу устройства 2. В данном устройстве зависимости (3) - (5) алгоритма Волдера решаютс в трех параллельных каналах, что сокращает время вычисления. Кроме того, в блоке памяти констант запоминаются(п + 1)/3 различных констант а -ctg 2Г, которые при выполнении первых(п-И)/3 итераций поступают из блока памяти констант в сумматор-вычитатель канала ос, через четвертый сдвигающий регистр без сдвига кода, так как элемент И закрыт. После этого сигналом, поступающим на вход устройства, элемент И открывается,, и все следующие константы arct , поступающие в сумматор-вычитатель канала « из четвертого сдвигающего регистра, образуются путем сдвига последней записанной в блоке памяти константы вправо на число разрядов начиная с одного разряда до числа 2(3 п разрядов. Благодаря этому в три раза сокращается число констант, подле- . жащих хранению в блоке памяти кон- стант, но несколько увеличивается время вычисления из-за необходимости сдвига кодов для формирования констант. Недостатком указанного устройства является большое время вычисления из-за необходимости выполнения всех (n-t-1) итераций по алгоритму Волдера, причем с увеличением номера итерации увеличивается время ее выполнения из-за увеличения числа разрядов сдвига кодов координат перед пересылкой их в другой канал. Наиболее близким к изобретению по технической рущности является цифровой преобразователь координат, содержащий блок памяти исходных коор динат и угла, три подключенных к нему канала к , х и у, в каждом из которых решаются зависимости соответственно (3) - (5), программный блок управления и блок памяти величины 1/k, обратной коэффициенту деформации. Каждый из каналов х и у содержит последовательно включенные KOMMytaTop, сдвигатель и накапливающий сумматор-вычитатель, причем второй вход каждого коммутатора подключен к блоку памяти исходных координат и угла, первый вход - к выходу другого канала, а выходы каналов являются выходами преобраз.ователя. Канал, oi содержит блок..памяти констант, подключенный к нему первым входом третий коммутатор и подключенный к коммутатору накапливающий Сумматор-вычитатель. Второй вхсд коммутатора подключен к блоку памяти исходных координат и угла, выход .сумматора-вычитателя подключен к входу программного блока управления, к другому входу КОТОРОГО подключен выход.-блока памяти величины 1/k. Управляющие входы сумматоров-вычитателей, сдвигателей, коммутаторов и блока памяти констант подключены к выходам программного блока управления от первого до девятого 3. И.эвестиый цифровой преобразователь координат работает по командам из программного блока управления, в котором содержится программа вычисления в виде Последовательности наборов команд, посылаемых в следую щих друг за другом тактах в управляемые блоки.. В начале работы коды исходных ко ординат и угла через коммутаторы вв дятся в регистры сумматоров-вычитателей Потом по командам из програм много блока управления выполняются итерации по алгоритму Волдера от до . При каждой i-й итерации код одной координаты поступает в ка нал другой координаты, сдвигается вправо на i разрядов и алгебраически суммируется с хранящимся в регист ре сумматора-вычитдтеля кодом другой координаты: прибавляется и вычитается в соответствии со знаком плюс для координаты х и минус для координаты у и со значением коэффициента . Одновременно в канале об из полученного при предыдущей итерации остаточного угла (-() вычитается : угол | cif с tg , а программный блок управления по знаку полученного нового остаточного угла х QCW опреде ляет значение коэффициента +i для следующей {1-1-1)-й итерации. После выработки кодов х и у при выполнении последней итерации с номером эти коды по командам прог раммы умножения умножаются в суммат рах- вычитателях на величину 1/k, че устраняется деформация координат, возникающая при выполнении итераций по алгоритму Волдера. Благодаря одновременному решению всех трех зависимостей(3) - (5) алгоритма Волдера для преобразования координат цифровой преобразователь кобрдинат выполняет вычисление за время примерно в три раза меньшее чем классическая ЦВМ, содержащая од но арифметическое устройство. Тем не менее время вычисления в указанном преобразователе Остается большим из-за необходимости выполнения всех (n-t-1) итераций по алгоритму Волдера, особенно в тех случаях, когда требуется высокая точность вы числения и, соответственно большое число итераций и сдвиг кодов координат во второй половине итераций на большое число разрядов. .Цель изобретения - повышение быст родействия цифрового преобразователя координат. Поставленная цель достигается тем, что в цифровой преобразователь координат, содержаний блок памяти исходных координат и угла, первый, второй и третий сумматоры-вычитатели, первый и второй сдвигатели, первый, второй и третий коммутаторы, блок памяти констант, блок памяти величины, обратной коэффициенту деформации, и програмтиный блок управления, причем первый информационный вход первого коммутатора подключен к выходу второго сумматора-вычитателя, а выход - к информационному входу первого сдвигателя, выход которого подключен к информационном входу первого сумматора-вычитателя, пер вый информационный вход второго коммутатора подключен к выходу первого сумматора-вычитателя, а выход - к информационному входу второго сдвигателя, выход которого подключен к информационному входу второго сумматора-вычитателя, первый информацион- . ный вход третьего коммутатора подключен к выходу блока памяти констант а выход - к информационному входу третьего сумматора-вычитателя, выход которого соединен с входом программного блока управления, выходы которого .с первого по девятый подключены к управляющим входам первого, второго и третьего коммутаторов, первого и второго сдвигателей, первого, второго и третьего сумматоров-вычитателей и блока памяти констант соответственно, выходы первого и второго сумматоров-вычитателей являются выходами преобразователя, введены первый, второй и .третий множительные блоки, четвертый, пятый и шестой коммутаторы и блок памяти масштабного коэффициента, причем первый, второй и третий выходы блока памяти исходных координат и угла подключены к первым информационным входам четвертого и пятого коммутаторов и третьего множительного блока соответственно, вторые информационные входы четвертого и пятого коммутаторов подключены к выходам соответственно второго и первого сумматоров-вычитателей, а выходы - к первым информационным входам соответственно первого и второго множительных блоков, выходы которых подключены к вторым информационным входам соответственно первого и второго коммутаторов, вторые информационные входы первого и второго множительных блоков. Лбдключенык выходу шестого коммутатора, информационные входы которого подключены к выходу блока памяти величины, обратной коэффициенту деформации, и выходу третьего сумматора-вычитателя, второй информационный вход третьего множительного, блока подключен к выходу блока памяти масштабного коэффициента, выходы программного блока управления с десятого по двенадцатый подключены к управляющим входам четвертого, пято го и iiiecToro коммутаторов соответственно. На фиг. 1 представлена структурная схема цифрового преобразователя координат; на фиг. 2 - структурная схема программного блока управления на фиг. 3 - блок-с ема алгоритма работы программного блока управления, Преобразователь содержит блок 1 памяти исходных координат и угла, первый 2, второй 3 и третий 4 сумматоры-вычитатели, первый 5 и второй 6 сдвигатели, выходы которых подключены к информационным входам соответ ственно первого 2 и второго 3 сумматоров-вычитателей, а информадионные входы - к выходам соответственно первого .7 и. второго 8 коммутаторов, первые информационные входы которых подключены соответственно к выходам .сумматоров-вычитателей 3 и 2, и третий коммутатор 9, выход которого под ключен к информационному входу треть его сумматора-вычитателя 4. К выходам сумматоров-вычитателей 3 и 2 подключены также вторые информационные входы соответственно четвертого 10 и пятого 11 коммутаторов, первые информационные входы- которых подключены к первому и второму выходам бло ка 1 памяти исходных координат и угла. К выходу сумматора-вычитателя 4 подключен информационный вход шестого коммутатора -12,. а информационный вход коммутатора 9 подключен к выходу блока 13 памяти констант. К выходу коммутатора 12 подключены вторые информационные входы первого 14 и второго 15 множительных блоков первые информационные входы которых подключены к выходам коммутаторов 10 и 11 соответственно. Первый инфор мационный вход третьего множительного блока 16 подключен к третьему выходу блока 1 памяти исходных координат и угла, второй информационный вход - к выходу блока 17 памяти масштабного коэффициента, а выход к второму информационному входу коммутатора 9. Выход блока 18 памяти величины, обратной коэффициенту деформации, подключен к информационному входу коммутатора 12, а выход сумматора-вычитателя 4 соединен с входом программного блока 19 управления, выходы которого с первого по двенадцатый подключены к управляющим входам первого 7, второго 8 и третье го 9 коммутаторов, первого 5 и второ го 6 сдвигателей, первого 2, второго 3 и третьего 4 сумматоров-вычитателей, блока 13 памяти констант, а так же четвертого 10, пятого 11 и.шестого 12 коммутаторов. Выходы сумматоро вычитателей 2 и 3 являютсй выходами преобразователя. . Блок 19 имеет вход 20 и выходы 21-32 и содержит узел 33 микропрограммного - управленйя (в качестве которого используется, например, микросхема К589ИК01), узел 34 памяти текущих команд, узел 35 памяти кодов -управления адресом следующей комаяды и генератор 36 тактовых импульсов . . . Преобразователь работает по программе, заложенной в программном блоке 19 управления в виде последовательности кодов, отдельные разрящы или группы разрядов которых представляют собой команды, выдаваемые в управляемые блоки. В коммутаторы 7-12 - команды подключения к информационному входу следующего за коммутатором блока выхода одного из двух блоков, подключенных к информационным входам коммутатора, в сумма.торы-вычитатели 2 - 4 - команды прибавления или вычитания кодов, поступающих из сдвигателей 5 и 6 и блока 13 памяти констант, к коду (из кода), записанному в регистре сумматоравычитателя при предыдущей итерации, и команды записи кодов в регистры, в сдвигатели 5 и 6 - команды сдвига кодов в соответствии с программой вычисления, в блок 13 памяти констант - команды выборки и выдачи константы, соответствующей номеру итерации. Команды записаны-в узле 34 в виде кодов, в которых для каждого из управляемых блоков 2-13 цифрового преобразователя координат отведено свое поле;, для коммутаторов 7 - 12 одноразрядные.поля (код команды 0 передача кода с первого входа коммутатора на выход, код i - передача кода с второго входа на ВЕЛХОД) ; для сумматоров-вычитателей 2 - 4 двухразрядные поля (код команды 00 сложение, код команды 01 - вычитание, код команды 10 - запись в регистр); для сдвигателей 5 и 6 и блока 13 памяти констант -р -разрядное поле, где р - целое число, превышающее (/2+1) . Преобразователь работает следуюЩим образом. По командам из блока 19 коммутаторы 10 и 11 передают в множительные блоки 14 и 15 исходные координаты х(, и yjjj. из блока 1 памяти исходных координат .и угла, а коммутатор 12 - величину 1/k из блока 18 памяти величины, обратной коэффициенту деформации. Коммутаторы 7 и 8 передают коды x,(.,/k и Умсх/ из множительных блоков 14 и 15 в сдвигатели 5 и 6, в которых по командам из блока 19 установлен нулевой сдвиг кодов. Величины и через; сдвигатели 5 и 6 поступают в сумматоры-вычитатели 2 и 3, где по командам из блока 19 записываются в регистры. Одновременно с указанными операциями коммутатор 9 передает в сумматор-вычитатель 4 код 2iiot цех из множительного блока 16, на информационные входы которого вводятся коды«иск из блока 1 и 2и из блока 17 памяти масштабного коэффициента. Код 2il oi J,-X по команде из блока 19 записывается в регистр сумматора-вычитателя 4.

Затем по командам из блока 19 коммутаторы 7 и 8 подключают к информационным входам сдвигателей 5 и б выходы соответственно второго 3 и первого 2 с.умматоров-вычитателей, коммутатор 9 подключает к информационному входу третьего сумматора-вычитателя 4 выход блока 13 памяти констан и преобразователь по командам из бло ка 19 выполняет последовательно итерации по зависимостям (3) - (5) алгоритма Волдера от итерации с номером до итерации с номером , где 245 - заданная максимальная погрешность учета углаоi,-;, .

При каждой i-й итерации по командам из блока 19 с выхода сумматоравычитателя 3 через коммутатор 7 в сдвигатель 5 поступает код , выра ботанный при предыдущей (1-1)-и итерации, а с выхода сумматора-вычитателя 2 через коммутатор 8 в сдвигатель б поступает код Xi-,, выработанный При предыдущей (1-1)-и итерации сдвигатели 5, и Ь сдвигают коды у,, и х, на 1 разрядов вправо и neper дают сдвинутые коды У,.- и х,-.-2 в сумматоры-вычитатели 2 и 3 соответственно; в сумматорах-вычитателях 2 и 3 коды у,,.и х., 2 в зависимости от канала и значения коэффициента либо прибавляются к кодам х,-., и y соответственно, хранящимся в регистрах 9умматоров-вычитателей 2 и Э, либо вычитаются из кодов у,., (коэффициент i , определенный при предыдущей (1-1)-и итерации, выдается из блока 19); полученные коды х и у, записываются в регистры сумматоров-вычитателей 2 и 3 вместо хранившихся там до этого кодов х, и У4 I одновременно с перечисленными операциями коммутатор 9 передает из блока 13 в сумматор-вычитатель 4 код 1-й константы arctig 2, который с учетом выработанного при предыдущей (1-1)-и итерации значения коэффициента вычитает код этой константы из накопленного кода угла (Х-сстъСк-) прибавляет код конетанты к коду угла (з дстиО-О вырабатывает новый код углао(. / приближающегося с каждой новой итерацией к нулю; знак этого кода углаос с, запоминается в .блоке 19 в качестве

знака коэффициента , для следующей (1-1-1)-й итерации.

Таким образом, при 1-й итерации преобразователь вырабатывает коды координат X и у и коэффициент ,.

После выполнения итерации с номером коммутаторы 7 и 8 по командам из блока 19 подключают информационные входы сдвигателей 5 и б .к выходам множительных блоков 14 и 15 соответственно, в.сдвигателях 5 и 6 устанавливается нулевой сдвиг кодов, коммутатор 10 подключает первый информационный вход множительного блока 14 к вЕлходу сумматора-вычитателя 3, коммутатор 11 подключает первый информационный вход множительного блока 15 к выходу сумматора-вычитателя 2, а коммутатор 12 подключает вторые информационные входы обоих множительных блоков 14 и 15 к выходу сумм тора-вычитателя 4, в регистре которого в этот момент записан код

Тогда в множительных блоках 14 и 15 вырабатываются коды произведений

Уи-г-оостп/г иц- ости/2 °°гзетственно. Эти коды посту-пают соответственно через коммутатор 7 и сдвигатель 5 в сумматор-вычитатель 2 и через коммутатор 8 и бдвигатель б в сумматор-вычитатель 3, где код Уц()п)7 прибавляется к коду х „/ а код, X j. ( вычитается из кода Уп(7. образуя выходные координа 0ыи УВЫХ поступающие на выходы преобразователя.

Этими операциями заканчивается преобразование координат х.. и у,, в систему координат, повернутую на уголОС сх относительно исходной системы координат.

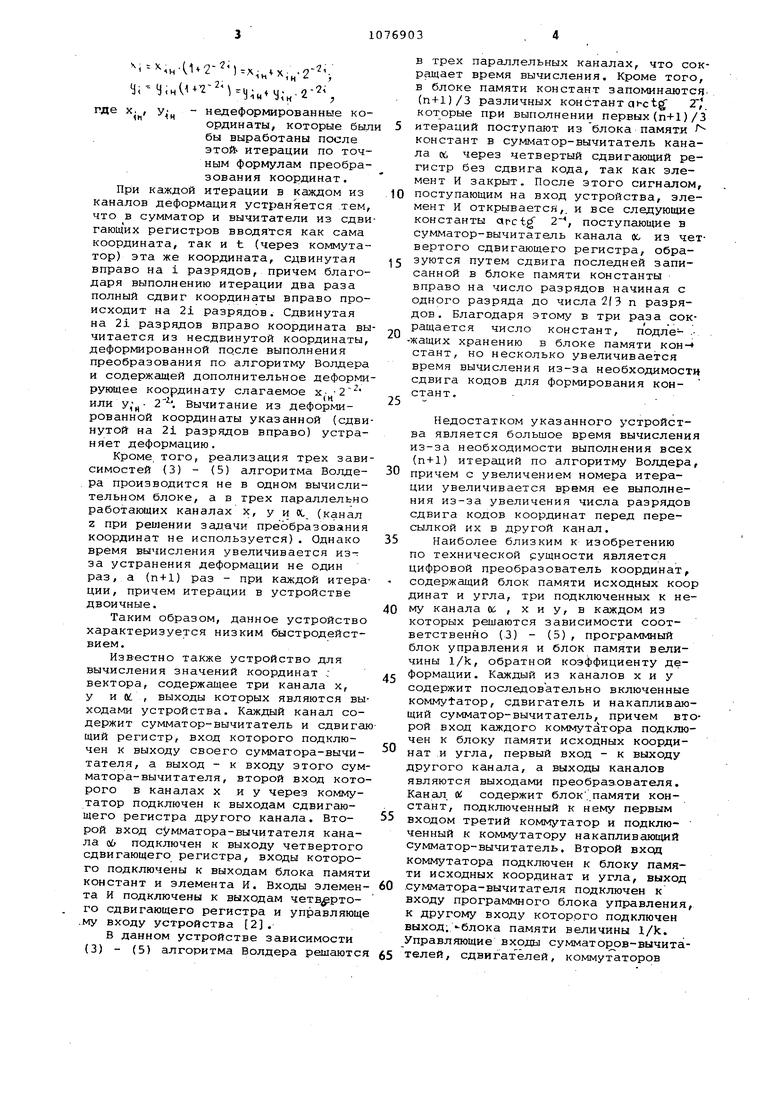

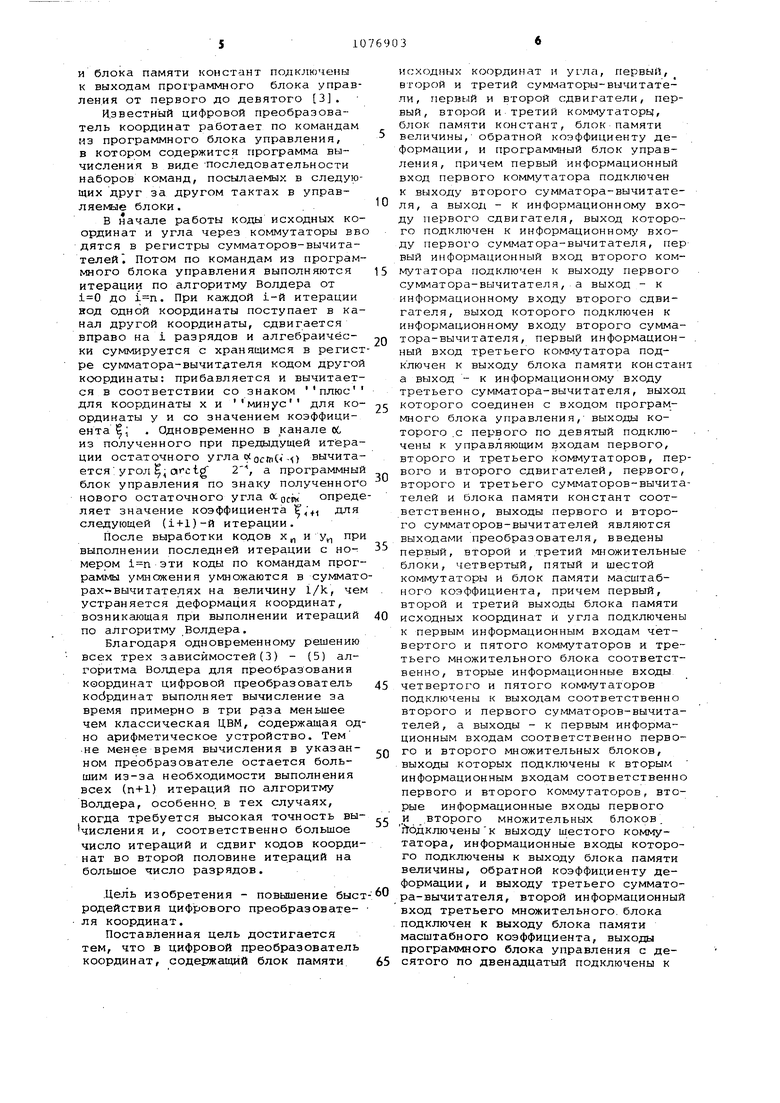

Программный блок 19 управления, осуществляющий управление блоками 2-13 преобразователя при решении описанной задачи, работает по алгоритму, представленному на фиг. 3.

Алгоритм работы блока 19 состоит из двух ветвей: выработки кода текущей команды и управления адресом следующей команды.

Адрес команды (правая ветвь алгоритма на фиг. 3) вырабатывается следующим образом.

Номер j текущей команды начиная с поступает в узел 33 и проверяется на равенство его номеру jj команды конца программы. При этом используется условный переход по условию . При невыполнении этого ус ловия (при ) номер j в виде кода из узла 33 поступает в узел 35 в качестве адреса, по которому из последнего выбирается и выдается в узел 33 код (j-H) , Этот код задерживается на время выработки и исполнения в преобразователе j-й команды. (В блок-схеме алгоритма это отмечено блоком Ожидание). Задерж-ка, как и вообще вся .синхрониза ция работы блока 19, осуществляется генератором 36 тактовых импульсов, . Когда номер j становится равным номеру к f происходит переход к окончанию работы преобразователя (к блоку ;Стоп). Код команды в 2-13 преобра зователя вырабатывается по левой ве ви алгоритма на фиг. 3. В узел 3.3, кроме номера ) команд поступающего из узла 35, поступает также из блока 4 код знакового разр да кода угла о: ocmi приЛ ocwi t Номер команды j .проверяется на выполнение его равенства номеру jnep , соответс вующему команде, выполненной после выполнения в преобразователе (tl/2 + l итераций по алгоритму Волдера. При невыполнении условияj-jnep номерj используется для выработки адреса текущей команды вместе с проверкой условия , В зависимости от это го условия .номер j или передается в узел 34 в качестве адреса (при N,(0) , или происходит переход к адресу 1-v m , где j + k (чтобы номер ко манда не совпал с одним из номе ров j i j t ) . По выработанному адресу j или jf.m из узла 34 выбирается и выдает ся в блоки 2-13 код команды для выполнения в преобразователе текущей итерации алгоритма Волдера при ; +1 или код ()i-4i..команды для выполнения в преобразователе текущей ит.ерации алгоритма .Волдера при J -iКогда выполняется условие } jпер (после окончания итерации с номером 1- и/2), номер jfiep поступает в узел 34 в качестве адреса, по которому выбирается код команды для умножени кода углаЫо(тпп; коды координат ХП/-2 и Уг,/2 / 3 по следующему номеру ° адресу, из узла 34 выбирается код команды для приба ления кода i| „, - uocmnrz к®ДУ и/,2 и вычитания кода х„, - оС ост из кода Уи)2 Такое построение преобразователя позв-рляет без ухудшения точности вычислений уменьшить практически в два раза - с (п+1) до (vr/2+l) - число итераций по алгоритму Волдера и заменить вторую половину итераций по этому алгоритму операциями умножения кодов координат Хщ Уп/2 , вычисленных при итерации с номером , на код остаточного угла (60(12 / вычисленного при этой-итерации, и операциями вычитаний кода произведения Хщ. «octfin/a з кода координаты Уц/2 и прибавления кода произведения УП/Ч осцп/2 коду коор динаты х„(2 Ввиду того, что числа разрядов, на которые сдвигаются коды координат при выполнении алгоритма Волдера,. увеличиваются с увеличением номера итерации, время выполнения второй половины итераций существенно превышает время выполнения первой половины итераций, так что исключение второй половины итераций и замена ее двумя простыми операциями умножения л алгебраического суммирования (обе операции суммирования выполняются одновременно в двух каналах х и у) позволяет почти в два раза уменьшить время вычислений и соответственно повысить быстродействие преобразователя. Расчеты, выполненные для случая построения предлагаемого преобразовав теля и прототипа на элементах тех же серий микросхем 133,556 и К589 и при одинаковой точности вычислений (погрешность учета угла of исх е более .45°), показывают, что, если даже считать среднее время выполнения одной итерации одинаковым для обоих преобразователей, рремя, затрачиваемое толькона собственно преобразование коодинат (без устранения деформации координат), в предлагаемом преобразователе на 41% меньше, чем в прототипе. Кроме того, среднее время выполнения одной итерации в предлагаемом преобразователе по сравнению с . известным на 10-20% меньше, так как. максимальный сдвиг кодов в нем происходит не на и , а на п/2 разрядов, что позволяет применять более простые и, соответственно, с большим быстродействием сдвигатели. Умножение координат на величину 1/k для устранения деформации в прототипе реализуется программно, что требует дополнительного времени, эквивалентного времени выполнения нескольких итераций. В предлагаемом пре, образовауеле эта oпepaциV реализуется за время одной итерации с помощью множительных блоков, которые введены для выполнения основной задачи замены аторой половины итераций. В итоге быстродействие предлагаемого преобразователя по сравнению с прототипом повышается в 1,5-2 раза в зависимости от требуемой точности вычислений (повышение быстродействия тем больше,чем больше число п , характеризующее точность вычислений).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU868753A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КООРДИНАТ, содержащий блок памяти исходных координат и угла, первый, второй и третий сумматоры-вычислители, первый и второй сдвигатели, первый, второй и третий коммутаторы, блок памяти констант, блок памяти величины, обратной коэффициенту деформации , и программный блок управления, причем первый информационный вход первого коммутатора подключен к выходу второго сумматора-вычитателя, а выход - к информационному входу первого сдвигателя, выход которого подключен к информационному входу первого сумматора-вычитателя, пер вый 1нформационный вход второго коммутатора подключен к выходу первого сумматора-вычитателя, а выход - к информационному входу второго сдвигателя, выход которого подключен к информационному входу второго сумматора-вычитателя, первый информационный вход третьего коммутатора подключен к выходу блока памяти констант, а выход - к информационному входу третьего сумматора-вычитателя, вход которого соединен с входом прсц раммного блока управления, выходы которого с первого по девятый подключены к управляющим входам первого, вто рого и третьего коммутаторов, первого и второго сдвигателей, первого, второго и третьего сумматоров-вычитателей и блока памяти констант соот ветственно, выходы первого и второго сумматоров-вычитателей являются выходами преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введены первый, второй и третий множительные блоки, четвертый, пятый и шестой коммутаторы и блок памяти масштабного коэффициента, причем первый, второй и третий выходы блока памяти исходных координат и угла подключены к первым информационным S входам четвертого и пятого коммутато (Л ров и третьего множительного блока соответственно, вторые информационные входы четвертого и пятого коммутаторов подключены к выходам соответственно второго и первого сумматороввычитателей, а выходы - к первым информационным входам соответственно первого и второго множительных бло .ков, выходы которых подключены к вторым информационным входам соответст х венно первого и второго коммутаторов, вторые информационные входы первого и второго множительных блоков подо ключены к выходу шестого коммутатора, 00 информационные входы которого подключены к выходу блока памяти величины, обратной коэффициенту деформации, и выходу третьего сумматора-вычитателя, второй информационный вход третьего множительного блока подключен к выходу блока памяти масштабного коэффициента,выходы программного блока управления с десятого по двенадцатый подключены к управляющим входам четвертого, пятого и шестого коммутаторов соответственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1973 |

|

SU445042A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппаратурная реализация элементарных функций в ЦВМ | |||

| Л., Изд-во ЛТУ, 1975, с | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1984-02-28—Публикация

1981-10-06—Подача