Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях,

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления экспоненциальной функции комплексного переменного.

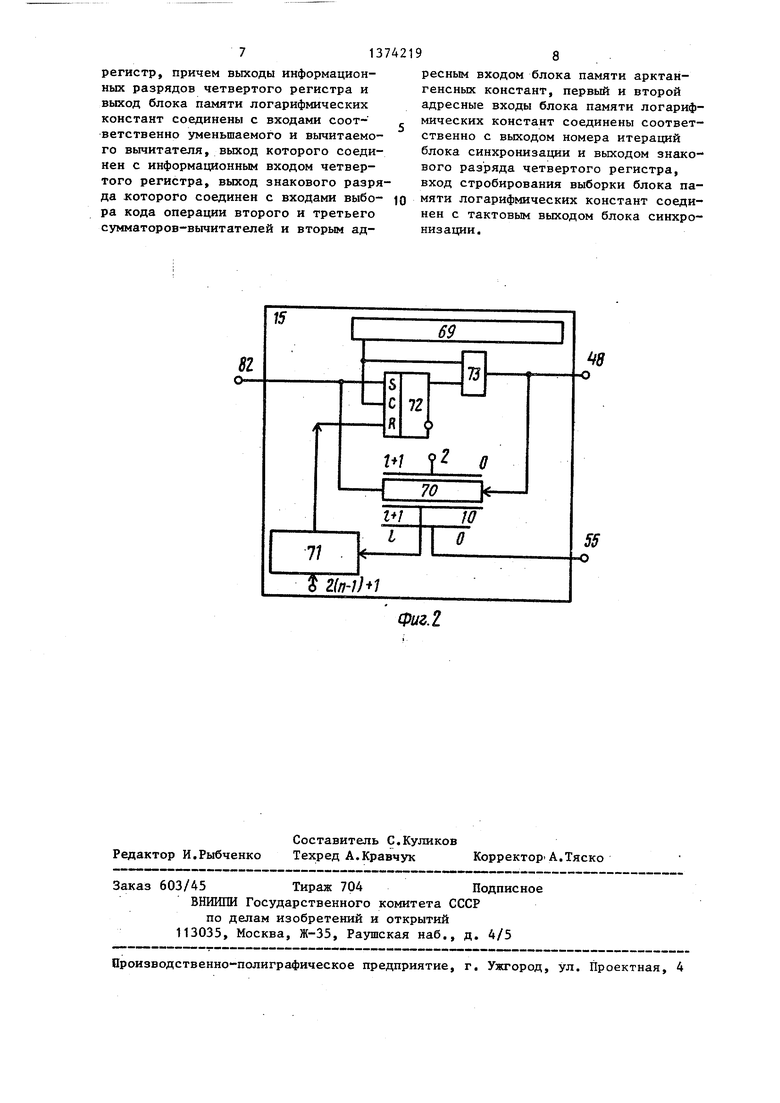

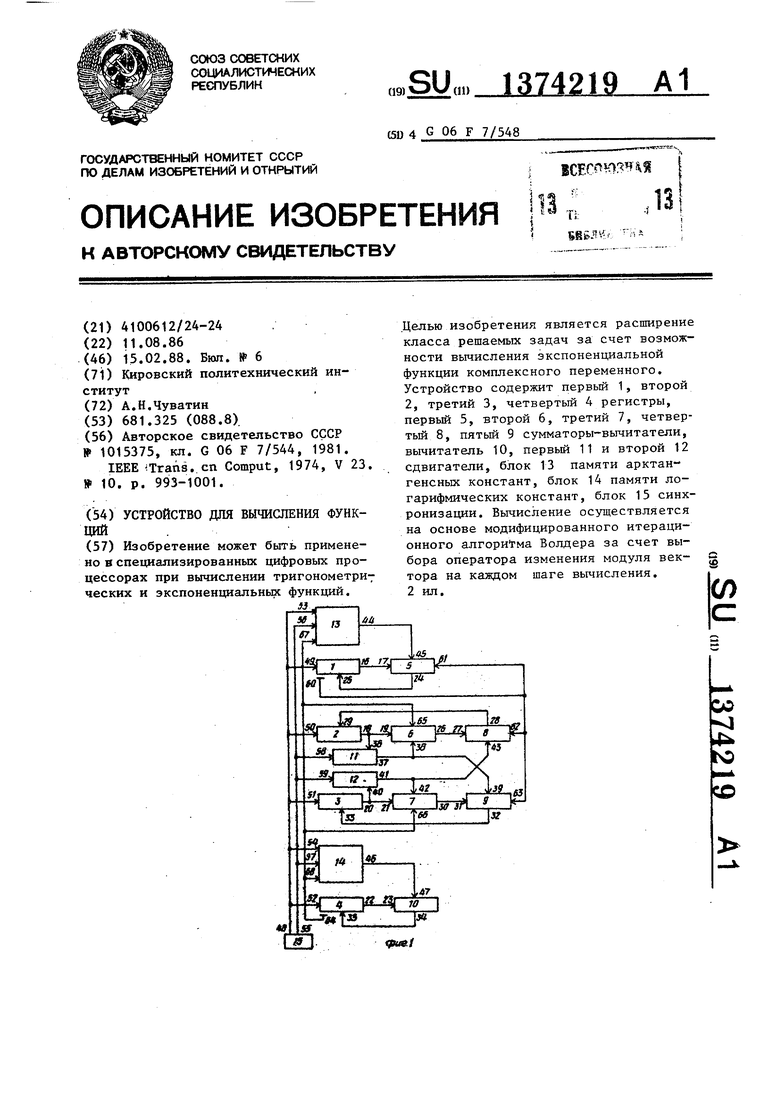

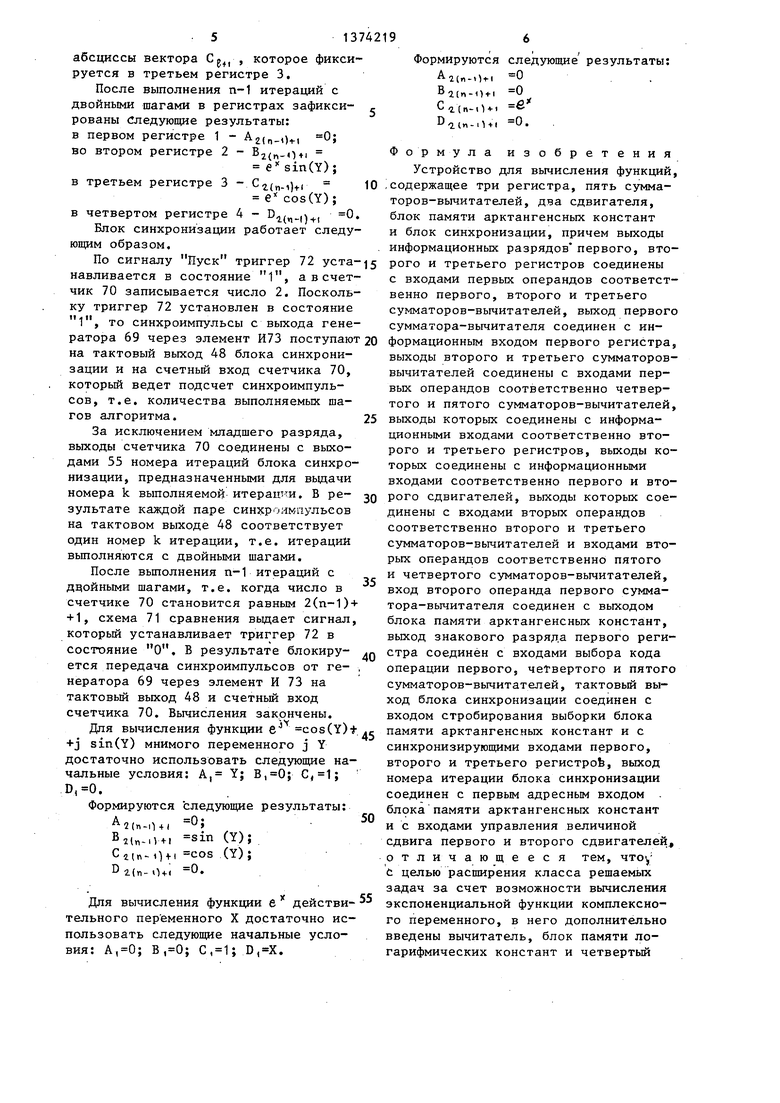

На фиг.1 представлена функциональная схема устройства; на фиг.2 - пример реализации блока синхронизации.

Устройство содержит первый, второй, третий и четвертый регистры 1-4 первый, второй, третий,. четвертьй и пятый сумматоры-вычитатели 5-9, вы- читатель 10, первый и второй сдвига- тели 11 и 12, блок 13 памяти арктан- генсных констант, блок 14 памяти логарифмических констант, блок 15 синхронизации, выходы 16 информационных разрядов первого регистра, вход 17 первого операнда первого сумматора- вычитателя, выходы 18 информационных разрядов второго регистра, вход 19 первого операнда второго сумматора- вычитателя, выходы 20 информационных разрядов третьего,.регистра, вход 21 первого операнда третьего сумматора- вычитателя, выходы 22 информационных разрядов четвертого регистра, вход 23 уменьшаемого вычитателя, выход 24 первого сумматора-вычитателя, информационный вход 25 первого регистра, выход 26 второго сзгмматора-вычитате- ля, вход 27 первого операнда четвертого сумматора-вычитателя, вькод 28 четвертого сумматора, информационный .вход 29 второго регистра, выход 30 третьего сумматора-вычитателя, вход 31 первого операнда пятого сумматора- вычитателя, выход 32 пятого сумматора-вычитателя, информационный вход 33 третьего регистра, выход 34 вычитателя, информационный вход 35 чет- вертого регистра, информационный вход 36 первого сдвигателя, выход 37 первого сдвигателя, вход 38 второго операнда второго сумматора-вычитателя, вход 39 второго операнда пятого сум- матора-вычитателя, информационный вход 40 второго сдвигателя, выход 41 второго сдвигателя, вход 42 второго операнда третьего сумматора-вычитателя, вход 43 второго операнда четвер- того сумматора-вычитателя, выход 44 , блока памяти арктангенсных констант, вход 45 второго операнда первого сумматора-вычитателя, выход 46 блока памяти логарифмических констант, вход 47 вычитаемого вычитателя, тактовый выход 48 блока синхронизации, синхронизирующие входы 49-52 соответственн первого, второго, третьего и четвертого регистров, вход 53 стробировани выборки блока памяти арктангенсных констант, вход 54 стробирования выборки блока памяти логарифмических констант, выход 55 номера итерации блока синхронизации, первьй адресный вход 56 блока памяти арктангенсных констант, первый адресный вход 57 блока памяти логарифмических констант, входы 58 и 59 управления величиной сдвига соответственно первого и второго сдвигателей, выход 60 знакового разряда первого регистра, входы 61-63 выбора кода операции соответственно первого, четвертого и пятого сумматоров-вычитателей, выход 64 знакового разряда четвертого регистра, входы 65,66 выбора кода операции соответственно второго и третьег сумматоров-вычитателей, вторые адресные входы 67 и 68 соответственно блока. памяти арктангенсных констант и блока памяти логарифмических констант. Блок синхронизации содержит генератор 69 синхроимпульсов, счетчи 70, схему 71 сравнения, триггер 72 и элемент И73.

Устройство работает следующим образом.

Введем следующие обозначения: Ag,Bg,Cg,Dg - переменные алгоритма для обозначения соответственно угла, ординаты, абсциссы, логарифма. Коэффициента удлинения модуля вектора на 1-м щаге;

,+1j - оператор направления поворота вектора на -м шаге; Pg 6 U + l оператор направления

изменения модуля вектора на 1-м шаге; 1 - сквозной номер шага от начала

вычислений;

k - номер вьшолняемой итерации. f(l+1)/2 для нечетных 1;

1/2 для четных 1; п + 2 - разрядность устройства; п - 1 - количество разрядов в дробной части числа, количество выполняемых итераций с двойными шагами.

rtOMe

.

Область определения фукнции: О 6 /X/ i 1; О t /Y/ Tr/2.

Область значения функции: .cos(Y) ; Ot/e ..sin(Y) .

Устройство реализует следующий ритм .вычисления функции е е e.cos(Y)+je --sin(Y) комплексн переменного Z X+jY: A,Y; В,0; С,1; D,X. Интерации

E 3HAK/Aj/; I Dgl I

A0,Aj-Ejarctg(2 Vl+Pj2 ))

В

p+i

Bg+EgCe2- +PgBe2- ,2 +P5Bg2e iСр4.1 Ср-ЕпВ

gDj+2

-iKt

De,,D -0;51n(I+Pt2- где ,2,...,2(п-1);

., Г(1+1)/2 для нечетных 1;

1/2 для четных 1. Результаты

В исходном положении в регистрах

находятся следующие данные: в первом регистре 1 - мнимая составляющая Y комплексного аргумента Z; во втором регистре 2 - число 0; в третьем регистре 3 - число 1; в четвертом реги- стре 4 - действительная составляющая X комплексного аргумента Z,

Блок 15 синхронизации вырабатывае распределенную во времени последовательность сигналов на своих выходах: на тактовом выходе 48 формируется последовательность синхросигналов, подаваемых на синхронизирующие входы 49-52 соответственно первого 1, второго 2, третьего 3 и четвертого 4 регистров и на входы стробирования выборки 53, 54 соответственно блока 13 памяти арктангенсных констант и блока 14 памяти логарифмических констант; на выходе 55 формируется последовательность номеров выполняемых итераций.

На каждой итерации вырабатьшаются два синхросигнала. Под воздействием

каждого синхросигнала реализуется один шаг алгоритма.

Режим работы (сложения или вычитания) первого 5, четвертого 8 и пятого

10

30

3742194

9 сумматоров-вычитателей задается сигналом с выхода 60 знакового разряда первого регистра 1. Режим работы - (сложения или вычитания) второго 6 и третьего 7 сумматоров-вычитателей задается сигналом с выхода 64 знакового разряда четвертого регистра. Этот же сигнал управляет выбором соответствующей логарифмической константы в блоке 14 памяти логарифмических констант и арктангенсной константы в блоке 13 памяти арктангенсных констант,

Предьщущее значение угла вектора Ag и арктангенсная константа поступают соответственно из первого регистра 1 и блока 13 памяти арктангенсной константы в .первый сумматор-вычита- тель 5, где формируется новое значение угла вектора Ag, , которое фиксируется в первом регистре 1.

Предыдущее значение логарифма коэффициента удлинения модуля вектора Dg и логарифмическая константа поступают соответственно из четвертого регистра 4 и блока 14 памяти логарифмических констант в вычитатель 10, где формируется новое значение логарифма коэффициента удлинения модуля

15

20

25

0

0

5

0

вектора Dg,, которое фиксируется в четвертом регистре 4.

В соответствии с номером выполняемой итерации в первом 11 и втором 12 сдвигателях выполняется сдвиг предыдущих значений соответственно ординаты Bg и абсциссы Ср вектора на k разрядов вправо, т.е. на выходах первого 11 и второго 12 сдвигателей формиру - Ц.

величины соответственно

- К

С{, 2 . 11ре;чьщущее значение ррдивектора В, ее приращения . ; Cg 2 поступают соответственно

11 и

5

ются и

на ты и

из первого регистра 1, первого второго 12 сдвигателей в цепь, coi-To- ящую из-второго 6 и четвертого 8 сумматоров-вычитателей, в результате в четвертом сумматоре-вычитателе 8 формируется новое значение ординаты вектора Bj., , которое фиксируется во втором регистре 2. Предыдущее значение абсциссы вектора С. , ее приращения и Вп 2 поступают соответственно из второго регистра 2 и второго 12 и первого 11 сдвигателей в цепь, состоящую из третьего 7 и пятого 9 сумматоров-вычитателей, в результате в пятом сумматоре-вычитателе 9 формируется новое значение

абсциссы вектора Cg, , которое фиксируется в третьем регистре 3.

После выполнения п-1 итераций с двойными шагами в регистрах зафиксированы Следующие результаты: в первом регистре 1 - А2(п-0 И во втором регистре 2 - В,,-),

(Y); в третьем регистре 3 С(„.,),

e cos(Y);

в четвертом регистре 4 - D,,s, 0. Блок синхронизации работает следуФ о р м у ла изобретения Устройство для вычисления функций, 10 .содержащее три регистра, пять сумма- торов-вычитателей, два сдвигателя, блок памяти арктангенсных констант и блок синхронизации, причем выходы информационных разрядов первого, втоющим образом.

По сигналу Пуск триггер 72 уста-15рого и третьего регистров соединены

навливается в состояние 1, а в счет-с входами первых операндов соответстчик 70 записывается число 2. Посколь-венно первого, второго и третьего

ку триггер 72 установлен в состояниесумматоров-вычитателей, выход первого

, то синхроимпульсы с выхода гене-сумматора-вычитателя соединен с ин 1

ратора 69 через элемент И73 поступают 20 формационным входом первого регистра.

на тактовый выход 48 блока синхронизации и на счетньй вход счетчика 70, который ведет подсчет синхроимпульсов, т.е. количества выполняемых шагов алгоритма.

За исключением младшего разряда, выходы счетчика 70 соединены с выходами 55 номера итераций блока синхронизации, предназначенными для выдачи

выходы второго и третьего сумматоров- вычитателей соединены с входами первых операндов соответственно четвертого и пятого сумматоров-вычитателей, 25 выходы которых соединены с информационными входами соответственно второго и третьего регистров, выходы которых соединены с информационными входами соответственно первого и втономера k выполняемой итераш-ш. В ре- jg рого сдвигателей, выходы которых сое- зультате каждой паре синхр ямпульсов на тактовом выходе 48 соответствует один номер k итерации, т.е. итераций вьшолняются с двойными шагами.

После выполнения п-1 итераций с двойными шагами, т.е. когда число в счетчике 70 становится равным 2(п-1) +1, схема 71 сравнения вьщает сигнал, которьй устанавливает триггер 72 в

35

динены с входами вторых операндов соответственно второго и третьего сумматоров-вычитателей и входами вторых операндов соответственно пятого и четвертого сумматоров-вычитателей, вход второго операнда первого сумматора-вычитателя соединен с выходом блока памяти арктангенсных констант, выход знакового разряда первого регистра соединён с входами выбора кода операции первого, четвертого и пятого сумматоров-вычитателей, тактовьш выход блока синхронизации соединен с входом стробирования выборки блока памяти арктангенсных констант и с синхронизирующими входами первого, второго и третьего регистроЬ, выход номера итерации блока синхронизации соединен с первым адресным входом . блока памяти арктангенсных констант и с входами управления величиной сдвига первого и второго сдвигателей, отличающееся тем, чтоу с целью расширения класса решаемых задач за счет возможности вычисления экспоненциальной функции комплексного переменного, в него дополнительно введены вычитатель, блок памяти логарифмических констант и четвертый

состояние О . В результате блокируется передача синхроимпульсов от генератора 69 через элемент И 73 на тактовый выход 48 и счетньй вход счетчика 70. Вычисления закончены.

Для вычисления функции е cos(Y)t +j sin(Y) мнимого переменного j Y достаточно использовать следующие начальные условия: А, Yj В,0; С,1; D,0.

Формируются следующие результаты

2(n-l44l

Bib-iVti sin (Y); Сц„.,) + cos (Y); D 2(n- Ui 0

у

Для вычисления функции e действи-

тельного переменного X достаточно использовать следующие начальные условия: А,0; В,0; С,1} D,X.

следующие результаты:

0, .

0 6

0.

Ф о р м у ла изобретения Устройство для вычисления функций, 10 .содержащее три регистра, пять сумма- торов-вычитателей, два сдвигателя, блок памяти арктангенсных констант и блок синхронизации, причем выходы информационных разрядов первого, вто15рого и третьего регистров соединены

выходы второго и третьего сумматоров- вычитателей соединены с входами первых операндов соответственно четвертого и пятого сумматоров-вычитателей, выходы которых соединены с информационными входами соответственно второго и третьего регистров, выходы которых соединены с информационными входами соответственно первого и второго сдвигателей, выходы которых сое-

динены с входами вторых операндов соответственно второго и третьего сумматоров-вычитателей и входами вторых операндов соответственно пятого и четвертого сумматоров-вычитателей, вход второго операнда первого сумматора-вычитателя соединен с выходом блока памяти арктангенсных констант, выход знакового разряда первого регистра соединён с входами выбора кода операции первого, четвертого и пятого сумматоров-вычитателей, тактовьш выход блока синхронизации соединен с входом стробирования выборки блока памяти арктангенсных констант и с синхронизирующими входами первого, второго и третьего регистроЬ, выход номера итерации блока синхронизации соединен с первым адресным входом . блока памяти арктангенсных констант и с входами управления величиной сдвига первого и второго сдвигателей, отличающееся тем, чтоу с целью расширения класса решаемых задач за счет возможности вычисления экспоненциальной функции комплексного переменного, в него дополнительно введены вычитатель, блок памяти логарифмических констант и четвертый

71374219

регистр, причем выходы информационных разрядов четвертого регистра и выход блока памяти логарифмических констант соединены с входами соот- ветственно уменьшаемого и вычитаемого вычитателя, выход которого соединен с информационным входом четвертого регистра, выход знакового разряда которого соединен с входами выбо- ю ра кода операции второго и третьего сумматоров-вычитателей и вторым ад8

ресным входом блока памяти арктан- генсных констант, первый и второй адресные входы блока памяти логарифмических констант соединены соответственно с выходом номера итераций блока синхронизахщи и выходом знакового разряда четвертого регистра, вход стробирования выборки блока памяти логарифмических констант соединен с тактовым выходом блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления эллиптических функций | 1987 |

|

SU1474641A2 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для вычисления логарифма | 1987 |

|

SU1432513A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

Изобретение может быть применено н специализированных цифровых процессорах при вычислении тригонометрии ческих и экспоненциальных функций. LW .Целью изобретения является расширение класса решаемых задач за счет возможности вычисления экспоненциальной функции комплексного переменного. Устройство содержит первый 1, второй 2, третий 3, четвертый 4 регистры, первый 5, второй 6, третий 7, четвертый В, пятый 9 сумматоры-вычитатели, вычитатель 10, первый 11 и второй 12 сдвигатели, блок 13 памяти арктан генсных констант, блок 14 памяти логарифмических констант, блок 15 синхронизации. Вычисление осуществляется на основе модифицированного итерационного алгоритма Волдера за счет выбора оператора изменения модуля вектора на каждом шаге вычисления. 2 ил. / р k Фие/

Фиг. 2

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| IEEE Trans | |||

| СП Comput, 1974, V 23 | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| р | |||

| Счетный полукруг для расчета радиосетей | 1921 |

|

SU993A1 |

Авторы

Даты

1988-02-15—Публикация

1986-08-11—Подача