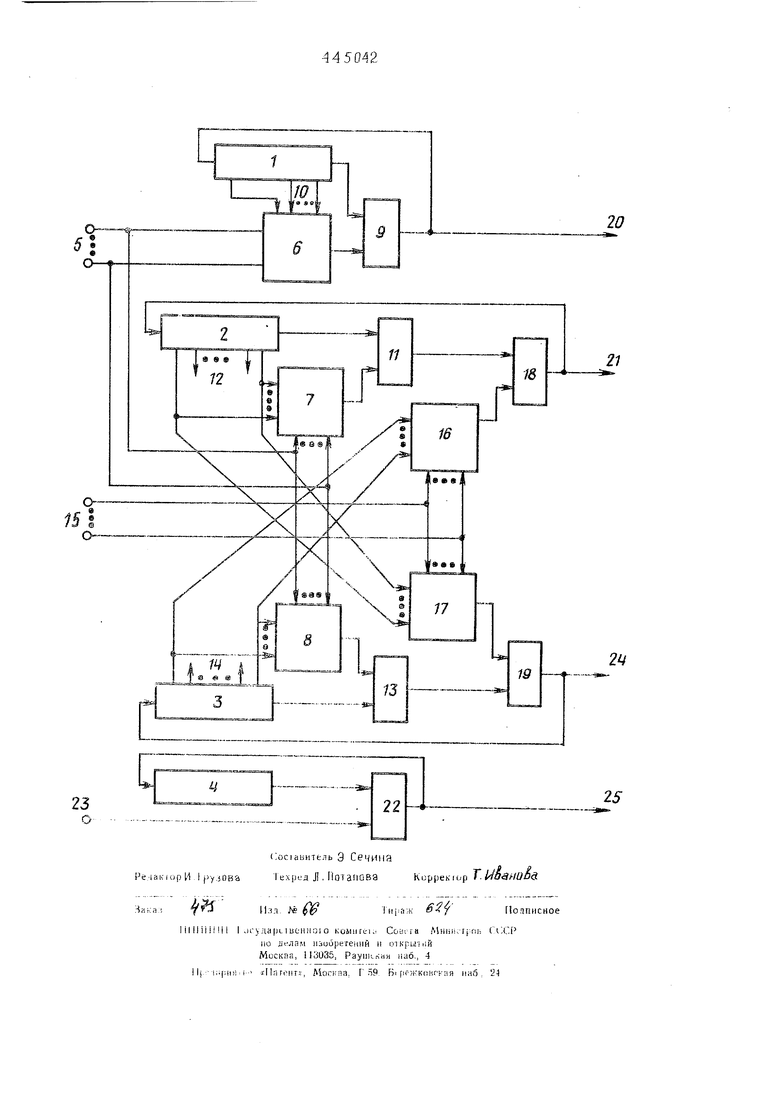

Устройство относится к облас ти вычислительной техники и предназначено для построения на его о нове специализированных ЦВМ. Известно арифметическое устройство, работающее по алгоритму Волдера. , i/i+i yi+ iXi2-;;.; XL4i Xt- li/t2 Si-n и позволяющее вычислять y Hi (У СО$Л -f Xi ) 7 ,, л v гпая-и. а п я} - начальные данные; lt,6; - значения крординат и угла на t -и шаге; 1 - функция, показывающая направление вращения и равная (I) 3i (+1, если BI О, (-1 если BI (8) Г ч - (1 если yi. О, (d ь - .i; если Н о;(4) - угловая постоянная, равная arc-bq 2 - коэффициент общего удлинения вектора, равный произведению коэффициентов удлинения на каждой шаге при решенмш жригономеаржчбских за дач Цель Р1зобреченая расширение набора операции aps устройства ВолдерВо Это достигается feij ройотво дополнительно соде жм1 cpi матор 4eTBepfbifl сдвигающий регист третий четвертый ж пятый номшути блоки, два вычитателя. RH. ход сумматора соединен с четвертым выходом устройства и входом четвертого сдвигающего регистра, выходы после,7днего с первой груп пой входов третьего коммутирующего o-jiOKaj выход старшего разряда четвертого одвигаюш,его регистрао первым входом сумматора Бтор.ой вход которого связан с выходом третьего коммутирующего блока. Вторая группа входов третьего ком мутирующего блока подключена соответственно к третьей группе входов ус ройства и вторым группам входов четвертого и пятого комь утирующих блоков. Выход пер- Бого вычитателй соединен с вторым входом второго сумматора -Бычита-теля, первый вход первого вычита с выходом старшего разряда первого сдвигающего регистра, а второй вход первого вычитаделя о выходом четвертого комиутирующе го блока, первая группа входов которого связана соответственно с одноименными виходами первого сдвигающего регистра. Выход ;второго вычмтателя подключен к второму входу первого сумматора-вы-читателя, первый вход второго вычитателя - к выходу отершего разряда второго сдвигающего регистра а второйвход второго вычитателя - к выходу пятого коммутирую1дего блОхча, первая группа входов кото рого соединена еоответственпо о одноиыенныыи выходами второго сдв гающего регистра. На чертеже показана схема арифметического устройства, где сдвигающие регистры правлнющие входыi к оммутИРУющие блокиi сумматор; выходы регистра Ij первый вычитателъ5 выходы регистра 2| второй вычйтатель |, выходы регистра 3 | управляющие входы; коммутирующие блоки i сумматоры-вычитатели | выход Z, I выход У I сумматор-вычитатель J - вход угловой постоянной выход X I выход 9 Устройство работает по алгошхи , полученному преобразоваием алгоритма Болдера |4f-i/l- Z % i2XL .1 Xl-Xi2 f - -jlУi2- Кроме того, устройство дополительно позволяет решать соотноенияде Кр - К01,ффициент удлинения вектора Б алгоритме (6) координаты l-t-1 5 получаемые аждом шаге, соответствуют кооринатам вектора, дважды повернуого по алгоритму Волдера на ол d-l . Коэффициент удлинения вектоа на каждом шаге равен и . 1 + у -Sfi -2) 9 коэффициент общего удлинения Ki- l Bl- Jl r Если алгоритм (6) дополнить i4.| й4S l.s J взять равной (3) или рУНКЦйШ можно соответственно вычисять (I) или (2). В этом случае оэффициент удлинения равен К. Для вычисленияаге 1П7 алгоMSM (6) дополняется , -i, iZ-di ,.. , .т-Ь .. --l4i i, 4-l ecfl-u У 1, еслит ZL Выражение (IIJ позволяет при ычислении Z умножением 1 на ksi привести Z к одному асштабу с координатами х и у. При вычислении 5Г 5//7 устойотво работает следующим образоы. 54 Zi yitXi и &(.paii-TL(:;i иоответ сгвенно в pejH;:Tpax 1 - 4/ С началом очередного шага происходит следующее По одиоуу из управляющих входов Ь на коммутирующие блоки t,f и в из устройства управления поступает команда, по которой коммутирующий блок б подключает к входу сумматора 9 один из сдвиговы выходов 10 регистра I так, что на вход сумматора 9 поступает 2/ 2 , Коммутирующий блок 7 подсоединяет к входу вычитателя II один из сдвиговых выходов 12 регистра 2 так, что на вход вычитателя li поступает у Коммутирующий блок 8 подключает к входу Бычитателя 13 один из сдвиговых выходов 14 регистра 3 так, что на вход вычитателя 13 поступает )(12(По одному из управляющих входов 15 на коммутирующие блоки 16. 17 из устройства управления подаёт ся команда, по которой коммутирующий блок 16 подсоединяет к входу суыматора-вычитателя 18 один из сдвиговых выходов 14 регистра 3 так, что на вход сунматора-вычитателя 18 проходит мутирующий блок 17 подключает к входу сумматора-вычитателя 19 одия из сдвиговых выходов 12 регистра 2 так, что на вход сумматорр-вычитателя 19 поступает У/2-(.-3/ На второй вход сумматора 9 с выхода регистра I подается ц . Zt-.f , получающееся на выходе сумматора 9, записывается в pernci I и, кроме того, черев выход 20 направляется в устройство уоравления, где используется для определенияНа второй вход вычитателя II с выхода регистра 2 поступает gi , С выхода,вычитателя II разность {УгУ12 подается на второй вход Суиматора-Бычитателя 18, где в соответствии с Jfi суммируется (вычитается) сХ( , поскупающим с выхода коммутирующего блока 16. Значение « лучаемое на выходе сумматора-иычитателя 18, записывается в регистр 2 и через выход 21 поступает и упчройство управлении, где Б используется для определения Ji , На второй вычитателя 13 с выхода регистра 3 проходит Х/ . С выхода вычктателя 13 разность /у- v п ) ( L i подается на второй вход сумматора-вычктателя 195 где в соответствии с ; вычидается (суммируется) , поступающим с выхода коммутирующего блока 17. Значение Xi. получаемое на выходе суыматора-вычитателя 19 записывается в регистр 3 Для получения значение 0i с выхода регистра 4 подается на вход сумнатора-Бычитателя 22, на второй вход которого из запоминающего устройства по входу 23 поступает угловая постоянная В соответствии с 3i в сумматоре-вычихателе Bl су;Л1Ируегся (вычитается) с угловой лосгоянной, равной 2di -. B{,Jri , получаемая на выходе сумматора-вычитателя, записываетон в регистр 4о Процесс повторяется до выполнения заданного количества шагов. Б конце операции результаты У цVU- Ю MniVT fi4/j3jHf, Л4|«lUiJl быть выведены соответственно по линиям 20 - 25, В других режимах работа арифметического устройства аналогична работе в режиме вычисленияагс5/п.| о той разницей, что 1/, получается, как функция знака Bl снимаемого в устройство управлени ; или как функция знас выхода с выхода 21 о на yt Ui EflMET ИЗОБРЕТЕНИЯ Арифметическое устройство, ии держащее три сууиатора-вычитателя, три сдвигающих регистра, два коммутирующих блока, причем выходы первого сдвигающего регистре соединены с первой rpj/ппой одноиь енных входов первого коммутирующего блока; выход которого соединен о первым входом первого сумматоравычйТателя. а выходы второго сдвп гав Щего periicipa соединены с первой одноименных входов рого ког Тирр}щего блока, выход которого соединен с первым BXLriiiia второго (лмиатора -вычитателя, 1М; ход прр-ипгп п/ммагорг -вычитателп соединен с первым выходом устройства и с входом второго сдвигающего регистра, выход второго сумматора-вычитателя соединен с вторым выходом устройства и с входом первого сдвигающего регистра, выход третьего сумматора-вычитателя соединен с третьим выходом устро ства и входом третьего сдвигающего регистра, старший разряд которого соединен с первым входом третьего сумматора-вычитателя, а второй вход третьего сумматора-вычитателя соединен с первой группой входов устройства; вторые группы входов первого и второго коммутирующих блоков соединены соответственно с второй группой входов устройства, отличающееся тем, что, с целью расширения класса решаемых задач, устройство дополнительно содержит сумматор, четвертый сдвигающий регистр, третий, четвертый и пятый коммутирующие блоки, два вычитателя, причем выход сумматора соединен с четвертым выходом устройств и входом четвертого сдвигающего регистра, выходы которого соединен с первой группой входов третьего коммутирующего блока, выход старшего разряда четвертого сдвигающего регистра соединен с первым входом сумматора, второй вход которого соединен с выходом третьего коммутирующего блока; вторая группа входов третьего коммутирующего блока соединена соответственно с третьей группой входов ycтpoйcтiia и вторыми группами входов четвертого и пятого коммутирующих блоков; выход первого вычитателя соединен с вторым входом второго сумматоравычислителя; первый вход первого вычитателя соединен с выходом старшего разряда первого сдвигающего регистра, а второй вход первого вычитателя соединен с выходом четвертого коммутирующего блока, первая группа входов которого соединена соответственно с одноименными выходами первого сдвигающего регистра; выход второго вычитателя соединен с вторым входом первого суыматоравычитателя; первый вход второго вычитателя соединен с выходом старшего разряда второго сдвигающего регистра, а второй вход второго вычитателя соединен с выходом пятого коммутирующего блока, первая группа входов которого соединена соответственно с одноименными выходами второго сдвигающего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1975 |

|

SU547765A1 |

| Функциональный преобразователь | 1980 |

|

SU924714A1 |

| Арифметическое устройство | 1978 |

|

SU750483A1 |

| Арифметическое устройство | 1978 |

|

SU746508A1 |

| Арифметическое устройство | 2016 |

|

RU2625528C1 |

| Устройство для преобразования компонент тензора | 1978 |

|

SU734703A1 |

| Устройство для вычисления гиперболических функций | 1980 |

|

SU957208A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

| Арифметическое устройство | 1975 |

|

SU550634A1 |

| Устройство для вычисления тригонометрических функций | 1981 |

|

SU1003079A1 |

Авторы

Даты

1974-09-30—Публикация

1973-01-03—Подача