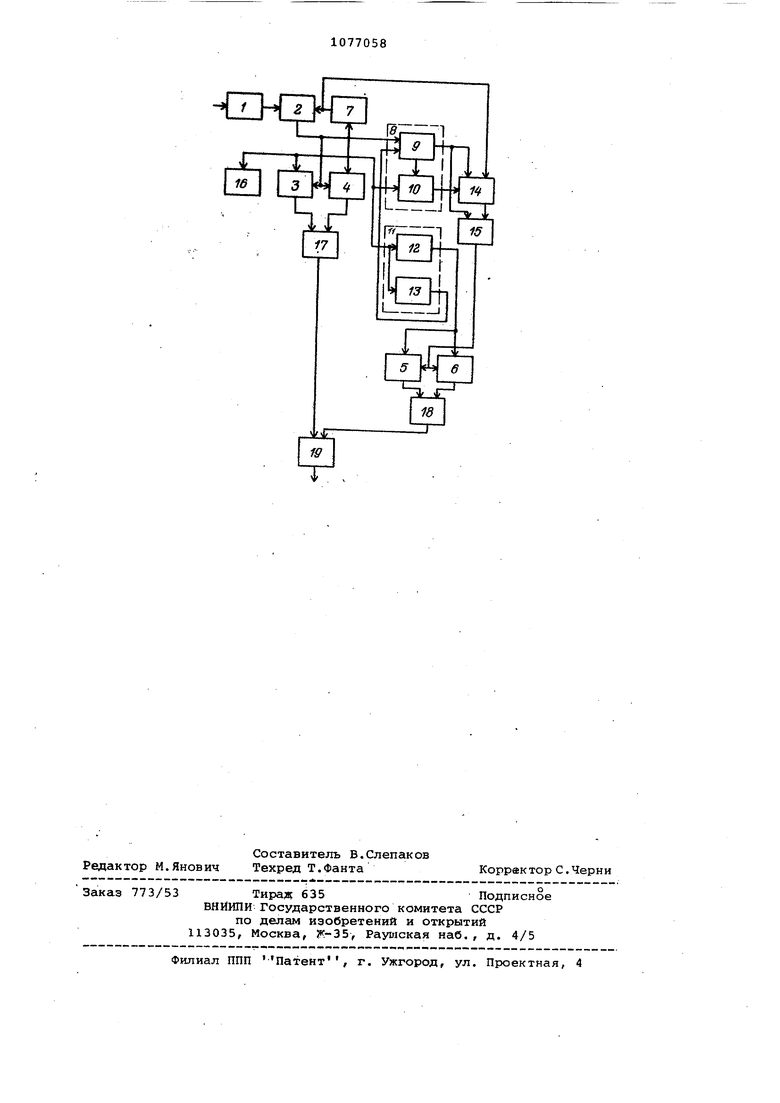

Изобретение относится к электро связи и может использоваться в устройствах контроля систем переда чи данных. По основному авт.св. 743214 известен анализатор качества канал связи, содержащий последовательно соединенные селектор импульсов по длительности и счетчик информацион символов, выход которого соединен первыми входами первого и второго элементов сравнения, выходы которых соединены соответственно с пер вым и вторым входами элемента ИЛИ а также хронизатор, выход которого соединен с вторыми входами первого и второго элементов сравнения и с входом элемента задержки, выход которого соединен с входом сброса счетчика информационных символов С Однако известный анализатор дае информацию о состоянии канала лишь в текущий момент времени, не предсказывая состоя-ние канала в по дуквдий, что снижает достоверность анализа-качества канала связи. Цель изобретения - повышение до стоверности анализа путем прогнози рования состояния канала связи на очередном интервале анализа. Указанная цель.достигается тем что в анализатор качества канала связи, содержащий последовательно соединенные селектор импульсов по длительности и счетчик информационных символов, выход которого соединен с первыми входами первого и второго элементов сравнения, выходы которых соединены соответстве но с первым и вторым входами элемента ИЛИ, а также хронизатор, выход которого соединен с втбрьомн входами первого и второго элементо сравнения и с входом элемента задержки, выход которого соединен с входом сброса счетчика информацион ных символов, введены последовательно соединенные блок памяти, блок вычитания, сумматор, третий элемент сравнения, дополнительный элемент ИЛИ и деишфратор, а такЖе четвертый элемент сравнения и блок задержек, при этом первый вход блока памяти соединен с выходом счетчика информационных символов, первый и второй выходы блока памяти соединены соответственно с вторым входом сумматора и с вторым входом блока вычитания, третий вход которого соединен с выходом элемента задержки, первый выход блока задержек соединен с в1орым входом третьего элемента сравнени первый и второй входы которого объ единены соответственно с первым и вторым входами четвертого элемента сравнения, выход которого соедине с вторым входом дополнительного элемента ИЛИ, второй выход блока задержек соединен с вторым входом блока памяти, третий вход которого соединен с йходом блока задержек и с выходом хронИзатора, выход элемента ИЛИ соединен с вторым входом дешифратора, блок памяти вып олнен в виде последовательно соединенных первого и второго регистров, причем первый и второй входы и второй выход первого регистра являются соответственно первым и вторым входами и первым выходом блока памяти, третьим входом и вторым выходом которого являются соответственно второй вход и выход второго регистра, а блок задержек выполнен в виде первого и второго дополнительных элементов задержки, объединенные входы которых являются входом блока задерлсек-, первым и вторым выходами которого являются выходы соответственно первого и второго дополнительных элементов задержки. На чертеже представлена структурная электрическая схема предлагаемого анализатора. Анализатор качества канала связи содержит селектор 1 импульсов по длительности, счетчик 2 информационных символов,- первый, второй, третий и четвертый элементы сравнения 3,4,5 и 6, элемент задержки 7, блок 8 памяти, содержа11ийпервый и второй регистры 9 и 10, блок 11 задержек, содержащий первый и второй дополнительные элементы задержки 12 и 13, блок.14 вычитания, сумматор 15, хронизатор 16, элемент ИЛИ 17, дополнительный элемент ИЛИ 18 и дешифратор 19. Анализатор работает следуквдим образом. На вход селектора 1 импульсов по длительности поступает аддитивная смесь бинарного сигнала с шумом. Селектор 1 импульсов по длительности выделяет только импульсы, длительность которых находится в пределах интервала селекции известной длительности информационных символов. Импульсы с выхода селектора 1 импульсов по длительности поступают на вход счетчика 2 информационньгх символов, выходы которого соединены с первым и вторым элементами сравнения 3 и 4 . Один из них определяет максимально допустимое, а другой - минимально допустимое значение счетчика 2 информационных символов. Граничные значения определяются на основании известного количества информационных символов на определенном промежутке времени. Опрос первого и второго элементов сравнения 3 и 4 производится сигналом с выхода хрониэатора 1Ь, по которому производится запись содер жимого первого регистра 9 во второй регистр 10 (значение Xj,) блока 8 памяти. Этим же сигналом, задери жанным в блоке 11 задержек вторым дополнительным элементом задержки 13на время записи информации во второй регистр 10 блока 8 памяти, производится запись содержимого счетчика 2 информационных сигетолов в первый регистр 9 блока 8 памяти (значение Х), Этим же сигналом, задержанным элементом задержки 7 на время записи информации J первый регистр 9 блока В памяти и на время срабатывания первого и второго элементов сравнения 3 и 4 про водится сброс счетчика 2 информаци онных символов и вычитание содержимого первого регистра 9 (Х) и второго регистра 10 (X-j) блока В п мяти в блоке 14 вычитания В сумматоре 15 производится суммирование содержимого первого регистра (Х) блока памяти 8 и полученного рассогласования ДХ , Х Х2-)- Х Выход сумматора 15 соединен, с третьим и четвертым элементами сравнения 5 и б. Один из них определяет максимально допустимое, дру гой - минимально допустимое значен сумматора 15. Граничные.-значения сумматора 15 выбираются такими же, как и граничные значения счетчика 2 информационных символов. Опрос третьего и четвертого элементов сравнения 5 и 6 производится сигна лом с выхода хронизатора 16, задержанным в блоке 11 задержек первым дополнительным элементом задер ки 12 на время срабатывания блока 14вычитания и сумматора 15. Сигна лы с выхода третьего и четвертого элементов сравнения 5 и б поступают на Вход дополнительного элемента ИЛИ 18, а сигналы с выходов первого и второго элементов сравнения 3 и 4 поступают на входы элемента ИЛИ 17. Сигналы с выходов элемента ИЛИ 17 и дополнительного элемента ИЛИ 18 поступают на входы дешифратора 19, с выхода которого виимаются снгналы, характеризующие качество связи согласно таблице. Сигналы с выходов элемента ИЛИ 17 Сигналы с выходов элемента ИЛИ 18 Сигнал на выходе деши фра тора Оценка контроля ка- Хоро-Удов&ет-Плочества канала связи ший . воритель хой Технико-экономическа-я эффективч ность анализатора качества канала связи заключается в повышении достоверности анализа за счет предсказания состояния канала в последующий момент времени и введения новой оценки качества канала Удовлетворительный наряду с плохой и Хороший. Знание предсказания последующей оценки состояния канала связи при приеме информации позволяет более оперативно принимать меры по устранению причин ухудшения качества канала связи и тем самым повышать качество канала связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор качества канала связи | 1983 |

|

SU1088139A1 |

| Преобразователь перемещения в код | 1987 |

|

SU1438001A1 |

| Устройство для оценки состояния канала связи | 1986 |

|

SU1438012A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1269174A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для контроля канала связи | 1988 |

|

SU1536517A2 |

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| Анализатор качества канала связи | 1979 |

|

SU813802A1 |

АНАЛИЗАТОР КАЧЕСТВА КАНАЛА СВЯЗИ по авт. св. 743214, о т л и чающийся тем, что, с целью повышения достоверности анализа путем прогнозирования состояния канала связи на очередном интервале анализа, в него введены последовательно соединенные блок памяти, блок вычитания, сумматор, третий элемент сравнения, дополнительный элемент ИЛИ и дешифратор, а также четвертый элемент сравнения и блок задержек, при этом первый вход блока памяти соединен с выходом . счетчика информационных символов, первый и второй выходы блока памяти соединены соответственно с вторым входом сумматора и с вторымвходом блока вычитания, третий вход которого соединен с выходом элемента задержки, первый выход блока зедер жек соединен с вторым входом элемента сравнения, первый и второй входы которого объединены соответственно с первым и BToptJM входами Четвертого элемента сравнения, выход которого соединен с вторым входом дополнительного элемента ИЛИ, второй выход блока задержек соединен с вторым входом блока памяти, третий вход которого соединен с входом блока задержек и с вьаходом хронизатора, выход элемента ИЛИ соединен с вторым входом дешифратора, блок памяти выполнен в виде последовательно соединенных первого и второго регистров, причем первый и второй входы и второй вы(Л ход первого регистра являются соответственно первым и вторым входами и первым выходом блока памяти, третьим входом и вторым выходом которого являются соответственно вто рой вход и выход второго регистра, а блок задержек выполнен в виде первого и второго дополнительных элементов задержки, объединенные vj входы которых являются входом блока | задержек, первым и вторым выходами которого являются выходы соответг о ственно первого и второгодополниел тельных элементов задержки. 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Анализатор качества канала связи | 1978 |

|

SU743214A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-28—Публикация

1982-06-09—Подача