ния параметра с выхода первого буфер- датчика 5 интервалов анализа переного регистра 13 на выход блока 10 экстраполяции и далее через блок 11 селекторов в блок 12 регистрации. Для этого во втором блоке 29 селекторов формируется управляющий сигнал, поступающий на управляющий выход блока 10.

По окончании второго периода анализа на управляющий вход блока 10 с выхода датчика 5 интервалов анализа поступает сигнал, переписывающий информацию из первого буферного регистра во второй записывающий второе значение вычисленного параметра в первый буферный регистр 13, записывающий и продвигающий 1 в сдвигающем регистре 17. Через время С, на входах элементов И 21, 23 и 28 образуется комбинация 1011, по которой формируется импульс на выходе только второго элемента И 23,

При наличии диух отчетов прогноз вычисляется по формуле:

записывает содержимое второго буфер ного регистра 14 в третий буферный регистр 15, первого буферного регистра 13 - во второй буферный ре40 гистр 14, записывает в первый буфер ный регистр 13 третьего значения вы численного параметра, продвигает и записывает 1 в сдвигающем регистр 17. Через время Ј на входах эле45 ментов И 21, 23 и 28 образуется ком бинация 1111, по которой формируетс импульс на выходе только первого эл мента И 21. В этом случае используется следующая формула экстраполя50 н:

a (j + 1) 3a(j) - 3a(j-1) + + a(j-2).

(5)

55

Сигнал с выхода первого элемента И 21 обеспечивает прием значений параметра, вычисленных по результата последнего измерения, с.выходов перзаписывает содержимое второго буферного регистра 14 в третий буферный регистр 15, первого буферного регистра 13 - во второй буферный регистр 14, записывает в первый буферный регистр 13 третьего значения вычисленного параметра, продвигает и записывает 1 в сдвигающем регистре 17. Через время Ј на входах элементов И 21, 23 и 28 образуется комбинация 1111, по которой формируется импульс на выходе только первого элемента И 21. В этом случае используется следующая формула экстраполя н:

a (j + 1) 3a(j) - 3a(j-1) + + a(j-2).

(5)

Сигнал с выхода первого элемента И 21 обеспечивает прием значений параметра, вычисленных по результатам последнего измерения, с.выходов первого буферного регистра 13 на вход второго блока 26 умножения через первый информационный вход третьего блока 30 селекторов и запуск второго блока 26 умножения через первый управляющий вход третьего блока 30 селекторов. Задержанный во втором элементе 19 задержки на время Ј} равно времени работы второго блока 26 умножения, сигнал с выхода первого элемента И 21 подается на управляющий вход сумматора 25 и разрешает его запуск. В сумматоре 25 производится сложение чисел, поступающих на его иформационные входы с выходов третьег буферного регистра 15 и второго блока 26 умножения. Одновременно сигнал с выхода второго элемента 19 задержк поступает на второй управляющий вход третьего блока 30 селекторов и обеспечивает прохождение числа с выхода второго буферного регистра 14 через гторой информационный вход третьего блока 30 селекторов на информационный вход второго блока 26 умножения и запуск его подачей сигнала на его управляющий вход. Через время t , равное времени работы второго блока 26.умножения, которое обеспечивается в четвертом элементе 2А задержки, управляющие сигналы подаются на вторые управляющие входы блоков 18 и 31 селекторов, разрешая прохождение через вшорые информационные входы данных соответственно с выхода сумматора 25 и второго блока 26 умножения на входы уменьшаемого и вычитаемого блока 27 вычитания, а также управляющего сигнала на запуск этого блока 27 с управляющего выхода первого блока 18 селекторов. Результат выполнения операции вычитания и управляющий сигнал поступает с выходов блока 27 соответственно на вторые информационный и управляющий входы второго блока 29 селекторов и затем на выход блока 10 экстраполяции.

Формула изобретения 50

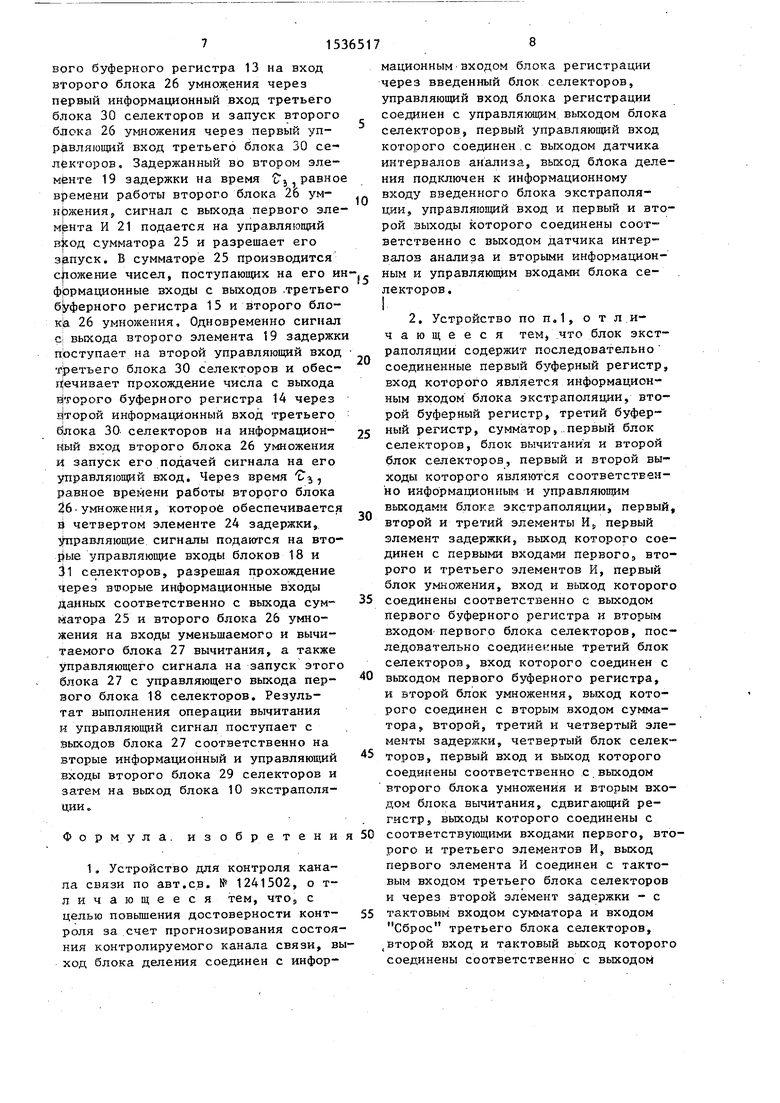

1. Устройство для контроля канала связи по авт.св. № 1241502, о т- личающееся тем, что, с

целью повышения достоверности контроля за счет прогнозирования состояния контролируемого канала связи, выход блока деления соединен с инфор

5

0

5

0

0

5

0

5

5

мационным входом блока регистрации через введенный блок селекторов, управляющий вход блока регистрации соединен с управляющим выходом блока селекторов, первый управляющий вход которого соединен с выходом датчика интервалов анализа, выход блока деления подключен к информационному входу введенного блока экстраполяции, управляющий вход и первый и второй выходы которого соединены соответственно с выходом датчика интервалов анализа и вторыми информационным и управляющим входами блока селекторов.

2. Устройство по п.1, отличающееся тем, что блок экстраполяции содержит последовательно соединенные первый буферный регистр, вход которого является информационным входом блока экстраполяции, второй буферный регистр, третий буферный регистр, сумматор, первый блок селекторов, блок вычитания и второй блок селекторов, первый и второй выходы которого являются соответственно информационным и управляющим выходами блок экстраполяции, первый, второй и третий элементы И, первый элемент задержки, выход которого соединен с первыми входами первого, второго и третьего элементов И, первый блок умножения, вход и выход которого соединены соответственно с выходом первого буферного регистра и вторым входом первого блока селекторов, последовательно соедипегные третий блок селекторов, вход которого соединен с выходом первого буферного регистра, и второй блок умножения, выход которого соединен с вторым входом сумматора, второй, третий и четвертый элементы задержки, четвертый блок селекторов, первый вход и выход которого соединены соответственно с выходом второго блока умножения и вторым входом блока вычитания, сдвигающий регистр, выходы которого соединены с соответствующими входами первого, второго и третьего элементов И, выход первого элемента И соединен с тактовым входом третьего блока селекторов и через второй элемент задержки - с тактовым входом сумматора и входом Сброс третьего блока селекторов, (второй вход и тактовый выход которого соединены соответственно с выходом

второго буферного регистра и тактовым входом второго блока умножения, выход второго элемента И соединен с тактовым входом первого блока умножения и через третий элемент задержки - с тактовыми входами первого и четвертого блоков селекторов, выход третьего элемента И соединен с тактовым входом второго блока селекторов, второй вход и управляющий вход которого соединены соответственно с выходом первого буферного регистра и управляющим выходом блока вычитания, управляющий вход которого соединен с уп0

равляющим выходом первого блока селекторов, выход второго элемента задержки соединен с входами Сброс первого и четвертого блоков селекторов через четвертый элемент задержки, выход второго буферного регистра соединен с вторым входом четвертого блока селекторов, тактовые входы первого, второго и третьего буферных регистров, вход первого элемента задержки, тактовый и управляющий входы сдвигающего регистра объединены и явля- ются управляющим входом блока экстраполяции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения момента изменения свойств случайного процесса | 1983 |

|

SU1166149A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Параллельно-последовательное множительное устройство | 1982 |

|

SU1156065A1 |

| Устройство для определения моментов изменения свойств случайного процесса | 1985 |

|

SU1282159A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Устройтво передачи и приема цифрового телевизионного сигнала | 1986 |

|

SU1394465A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

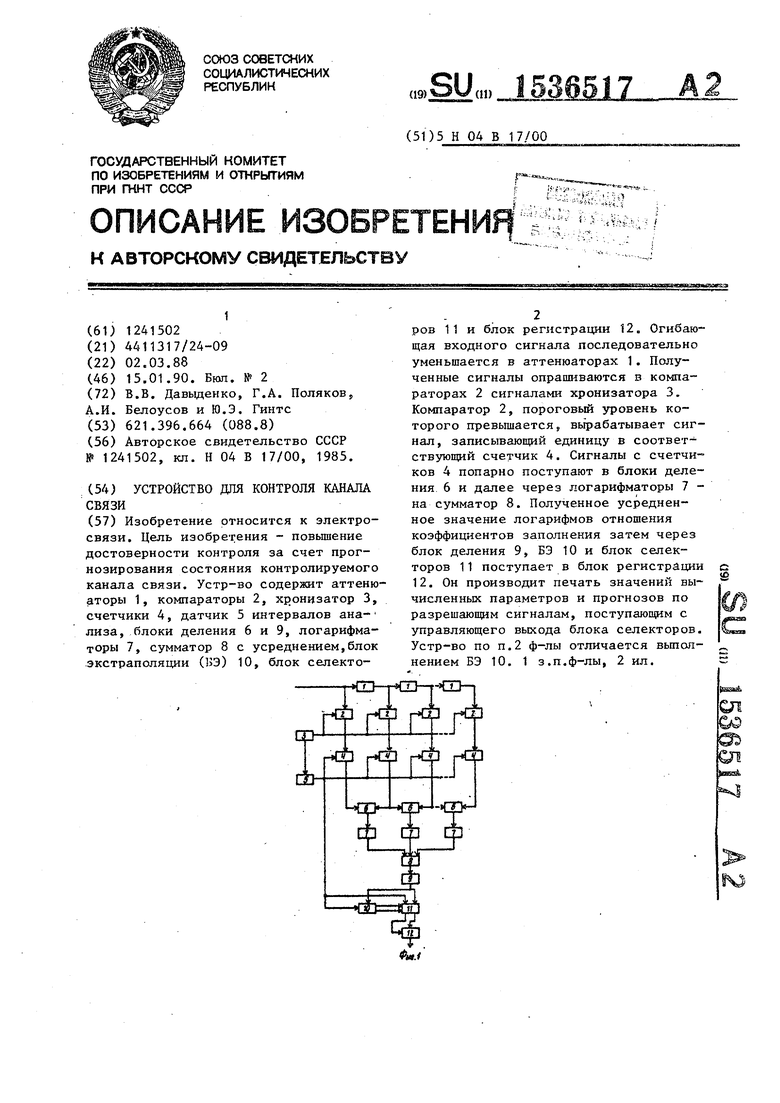

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности контроля за счет прогнозирования состояния контролируемого канала связи. Устройство содержит аттенюаторы 1, компараторы 2, хронизатор 3, счетчики 4, датчик 5 интервалов анализа, блоки деления 6 и 9, логарифматоры 7, сумматор 8 с усреднением, блок экстраполяции /БЭ/ 10, блок селекторов 11 и блок регистрации 12. Огибающая входного сигнала последовательно уменьшается в аттенюаторах 1. Полученные сигналы опрашиваются в компараторах 2 сигналами хронизатора 3. Компаратор 2, пороговый уровень которого превышается, вырабатывает сигнал, записывающий единицу в соответствующий счетчик 4. Сигналы с счетчиков 4 попарно поступают в блоки деления 6 и далее через логарифматоры 7 - на сумматор 8. Полученное усредненное значение логарифмов отношения коэффициентов заполнения затем через блок деления 9, БЭ 10 и блок селекторов 11 поступает в блок регистрации 12. Он производит печать значений вычисленных параметров и прогнозов по разрешающим сигналам, поступающим с управляющего выхода блока селекторов. Устройство по п.2 ф-лы отличается выполнением БЭ 10. 1 з.п. ф-лы, 2 ил.

С дырода блоха 5

С выхода

fAOKU Э

К бходам блока 11

| Устройство для контроля канала связи | 1985 |

|

SU1241502A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-01-15—Публикация

1988-03-02—Подача