1

Изобретение относится к запоминающим устройствам.

По основному авт. св. № 883975 известно устройство, содержащее накопитель, регистры числа, группы элементов ИЛИ, регистры адреса, счетчик адресов, блок контроля, блок управления и блок местного управления, коммутаторы, счетчик адресов, регистр адреса отказов, вход которого соединен с вы-)о ходом блока контроля, первый вход со входом счетчика разрядов, второй выход подключен ко входам коммутаторов, причем выход накопителя подключен к первым входам первого и второго is регистров-числа и ко входу третьего регистра числа, входы накопителя соединены с выходами элементов ИЛИ, входы элементов ИЛИ первой группы подключены к выходам первого регистра адре-20 са ивторого регистра адреса, вход которого соединен с выходом счетчика адресов, первый выход второго регистра числа и выход первого регистра числа

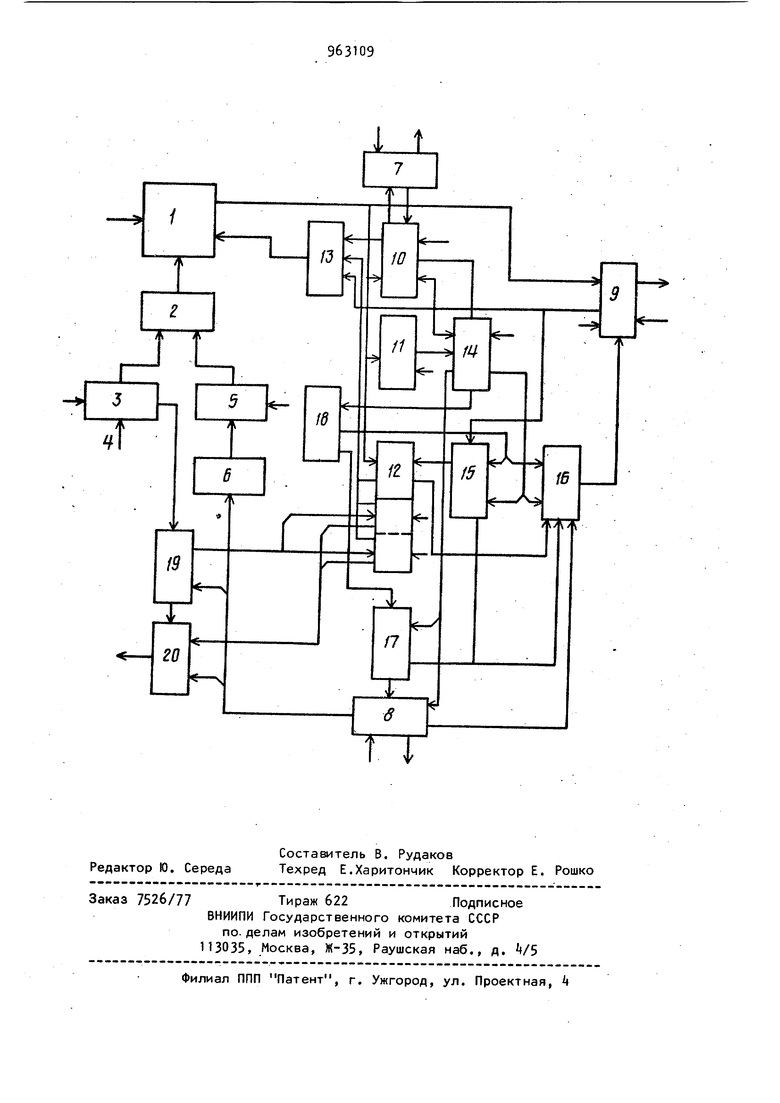

подключены к одним из входов вторТ5й группы элементов ИЛИ, вторые входы и выходы второго регистра числа соединены соответственно с выходом блока местного управления и первым входом блока контроля, второй вход которого соединен с выходом третьего регистра числа, один из выходов блока управления подключен к управляющим входам накопителя, первого и второго регистров адреса, счетчика адресов, первого, второго и третьего регистров числа, блока контроля и блока местного управления, входы четвертого регистра числа подключены соответственно к выходам накопителя и первого коммутатора, а выходы - к другим входам элементов второй группы и первому входу второго коммутатора, выход которого подключен к первому входу первого коммутатора, вторые и третий входы первого и второго коммутатора соединены соответственно с первыми выходами блока накопителя и счетчика разрядов, вто396рые входы которых подключены соответственно ко входам счетчика разрядов и блока управления, управляющие входы четвертого регистра числа и коммутато ров соединены с другими выходами блок управления, В этом устройстве отказавшие разря ды основных ячеек подменяются разряда ми ячеек накопителя, причем, если.резервные ячейки имеют отказавшие разряды, то они пропускаются и не участвуют в подмене отказавших разрядов ос новных ячеек 13, Недостатком этого устройства является невысокая надежность, поскольку установление соответствия между отказавшими разрядами основных ячеек и разрядами резервных ячеек производится при записи массива данных в накопитель. Если же после записи в основных или резервных ячейках накопителя возникнут дополнительные отказавшие разряды, то поскольку этот момент не фиксируется, весь дальнейший порядок подмены нарушается и наступает отказ всего устройства. Цель изобретения - повышение надеж ности устройства за счет сохранения работоспособности при возникновении дополнительных отказов в основных и резервных ячейках после записи массива данных в накопитель. Поставленная цель достигается тем, что в запоминающее устройство введены схема сравнения и блок свертки по модулю два, первый вход которого соединен с выходом первого регистра адреса а выходы подключены к одним из входов четвертого регистра числа и первому входу схемы сравнения, второй вход которой соединен с одними из выходов четвертого регистра числа, второй вход блока свертки по модулю два и третий вход схемы сравнения подключены к одному из выходов блока управления, один из входов которого соединен с выходом блока контроля, выход схемы сравнения является одним из управляющих выходов устройства. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит накопитель 1, первую группу элементов ИЛИ 2, первый регистр 3 адреса, имеющий вход , второй регистр 5 адреса, счетчик 6 адресов, блок 7 местного управления, блок 8 управления. К выходам накопителя 1 подключены один из входов первого регистра 9 числа, второго регистра 10 числа, вход третьего регистра 11 числа и один из входов четвертого регистра 12 числа. Устройство содержит также вторую группу элементов ИЛИ 13, блок 1A контроля, первый 15 и второй 1б коммутаторы, счетчик 17 разрядов, регистр 18 резервных ячеек, блок 19 свертки по модулю два и схему 20 сравнения. Устройство работает следующим образом. Для каждого линейного участка массива данных, которые записываются и считываются последовательно, выделяется последовательность резервных ячеек накопителя 1, В счетчик 6 при этом записывается адрес первой резервной ячейки, а со входа регистра 3 поступает адрес первой основной .ячейки записываемого или считываемого массива. Счетчик 17 разрядов в исходном сое-, тоянии обнулен. В режиме записи данных сначала осуществляется контроль исправности разрядов резервной ячейки. Адрес резервной ячейки из счетчика 6 передается через регистр 5 и элементы ИЛИ 2 на . вход накопителя 1, Производится считываже содержимого резервной ячейки в регистр 10, затем осуществляется запись-считывание обратного кода содержимого резервной ячейки в регистр 11. Содержимое регистров 10 и 11 подается на блок 14 контроля. Если отказавших разрядов в ячейке нет, то регистр 18 и счетчик 17 остаются в нулевом состоянии. При наличии отказавших разрядов в соответствующие им разряды регистра 18 записывается 1, в счетчик 17 записывается количество отказавших разрядов, а в маркерный разряд резервной ячейки накопителя с помощью блока 14 контроля через резистр 10 заносится 1, Далее производится запись массива данных. Данные поступают в регистр 9. Адрес первого слова данных, находящийся в регистре 3, через элементы ИЛИ 2 подается на вход накопителя 1. Обратный код первого слова из регистра 9 через элементы ИЛИ 13 записывается в основную ячейку накопителя, затем содержимое этой ячейки считывается в регистр 11 и осуществляется запись-считывание прямого кода того же слова в регистр 10. Прямой и обратный коды слова ере-, гистров 10 и 11 соответственно поступают в блок 14 контроля. Если блок 14 контроля не обнаруживает в ячейке отказавшие разряды, то в регистр 3 со входа 4 поступает следующий адрес и аналогично производится запись второго слова в основную ячейку накопителя 1, Если же в основной ячейке есть отказавшие разряды, то блок k контроля, счетчик 17 разрядов и регистр 18 выдают на коммутатор 15 сигналы, по которым из регистра 9 в младшие разряды регистра 12 передаются разряды слова, соответствующие отказавшим разрядам основной ячейки, причем в разряды регистра 12, соответствующие 1 регистра 18 (т. е. отказавшим разрядам резервной ячейки) запись не производится, эти разряды пропускаются и не используются. Одновременно с этим по сигналу от блока 1 контроля блок 8 управления выдает управляющие сигналы, по которым содержимое регистра 3 поступает на блок 19 свертки по модулю два, где формируется значение контрольного раз ряда адреса основной ячейки, имекхцей отказавшие разряды. Затем это значение заносится в один из двух разрядов регистра 12, специально отведенных дл этой цели. Кроме того, с блока 1А контроля в счетчик 17 записывается код, соответствующий количеству отказавших разрядов основной ячейки. Из блока 8 управ ления в блок 7 местного управления по ступает сигнал, по которому в маркерный разряд основной ячейки через регистр 10 записывается 1. Аналогично производится запись в следующую основ ную, ячейку, имеющую отказавшие разряды-, только соответствующие отказавшим разрядам ячейки, разряды регистра 9 заносятся в следующие свободные разря ды регистра 12 (с пропуском разрядов, соответствующих отказавшим разрядам резервной ячейки). После того, как вс разряды регистра 12 используются, сче тчик 17 выдает сигнал заполнения в блок 8 управления. В этот момент в ре гистре 3 находится адрес той основной ячейки, при определении отказавших ра зрядов которой происходит заполнение счетчика 17. По сигналу от блока 8 управления этот адрес подается на блок 19 свертки по модулю два, где формируется значение следующего контрольного разряда. Это значение заносится во второй контрольный разряд ре гистра 12. Таким образом, в двух конт рольных разрядах регистра 12 записываются результаты свертки по модулю 96 6 два адресов первой и последней основных ячеек, имеющих отказавшие разряды, истинные значения которых хранят- . ся в одной резервной ячейке. Затем адрес резервной ячейки из регистра адреса 5 через элементы ИЛИ 2 поступает на вход накопителя 1, а содержимое регистра 12 через элементы ИЛИ 13 заносится в резервную ячейку. После этого по сигналу из блока 8 управления в счетчике 6 формируется адрес следующей резервной ячейки. Чтение информации производится следующим образом. В регистр адреса 3 подается адрес первой основной ячейки считываемого массива данных, а в счетчике 6 формируется адрес первой резервной ячейки массива. Счетчик 17 при этом находится в нулевом состоянии. По сигналу из блока 8 управления производится передача содержимого счетчика 6 через регистр 5 и элементы ИЛИ 2 на вход накопителя 1. По этому адресу из резервной ячейки считывается слово в регистры 10 и 12. Если в маркерном разряде резервной ячейки код 1, то осуществляется запись-чтение обратного кода слова в регистр 11. Содержимое регистров 10 и 11 подается в блок I контроля. По сигналам от блока I контроля заносятся 1 в разряды регистра 18, соответствующие отказавшим разрядам данной резервной ячейки, а в сметчик 17 записывается количество этих разрядов. Если же в маркерном разряде резервной ячейки код О, то записьчтение обратного кода не производится, а счетчик 17 и разряды регистра 18 остаются в нулевом состоянии. Затем из регистра 3, в накопитель 1 постугГает адрес первой основной ячейки считываемого массива данных и производится считывание слова из накопителя в регистры 9 и 10. Если в маркерном разряде основной ячейки код О, следовательно в ней нет отказавших разрядов и слово из регистра 9 поступает на выход. Если же в маркерном разряде основной ячейки код 1, то производится запись-чтение обратного кода слова в регистр 11, Содержимое регистров Ю 4 11 подается в блок It контроля. По сигналу блока 1 t контроля блок 8 управления формирует управляющие сигналы, которые поступают в регистр 3, регистр 12, блок 19 свертки по модулю два и схему 20 сравнения. .В этот момент на регистре 3 находится адрес той основной ячейки, которая первой использует для подмены своих отказавших разрядов, разряды резервной ячейки, находящиеся в регистре 12 По этим сигналам указанный адрес сво- s рачивается по модулю два блоком 19, и результат свертки подается на один вход схемы 20 сравнения. На другой вход схемы 20 по сигналу блока 8 управления поступает первый контрольный 10 разряд из регистра 12, формируемый на этапе записи и хранящийся в данной резервной ячейке. Если сравнения не происходит, то в общем случае это означает, что з основных ячейках, имею- t5 щих отказавшие разряды, или в резервных ячейках, на которых чтение производится раньше, до обращения к данной основной ячейке, после записи массива данных в накопитель возникают отказы, 20 и порядок подмены отказавших разрядов основных ячеек нарушается. Схема 20 сравнения выдает сигнал ошибки, который поступает в процессор (не показан) и производится перезапись всего мае- 25 сива данных. При совпадении входных сигналов сигнал на выходе схемы 20 отсутствует. При этом по сигналам .лока Ik контроля, регистра 18 и счетчика 17 через зо коммутатор 16 младшие разряды регистра 12 передаются в регистр 9, причем разряды регистра 12, соответствующие разрядам регистра 18, находящимся в единичном состоянии, пропускаются. 0т казавшие разряды основной ячейки, таким образом, подменяются разрядами ре зервной ячей1 1. Затем сформированное слово из регистра 9 поступает на выход, В счетчик 17 записывается код, соответствующий количеству использованных разрядов регистра 12. Аналогич ный процесс продолжается до использования всех разрядов регистра 12, на что указывает соответствующее состояние счетчика 17 разрядов. Сигнал со счетчика 17 поступает на блок 8 управ ления, который выдает управл)дющие сиг налы на регистр 3, регистр 12, блок 19 и схему 20 сравнения. В это время на регистре 3 находится адрес той основной ячейки, при подмене неиеправных разрядов которой полностью задействуются разряды регистра 12 и происходит заполнение счетчика 17. Адрес основной ячейки-из регистра 3 поступает в блок 19 свертки по модулю два, а затем на один из входов 9631 98 схемы 20 сравнения. На другой вход схемы 20 сравнения поступает второй контрольный разряд из регистра 12, Если сравнение происходит, то сигнал на выходе схемы 20 отсутствует, счетчик 6 адреса по сигналам блока 8 управления формирует адрес следующей резервной ячейки, содержимое резервной ячейки считывается на регистр 12, и аналогично продолжается процесс считывания массива данных с подменой отказавших разрядов. Если же сравнения не происходят, на выходе схемы 20 сравнения появляется сигнал, который выдается в процессор и используется для перезаписи всего массива данных. Преимущество предлагаемого устройства заключается в том, что при считывании данных в течение времени использования разрядов одной резервной ячейки для подмены отказавших разрядов основных ячеек, дважды контролируется правильность подмены отказавших разрядов и путем перезаписи исключается влияние отказов в разрядах основных и резервных ячеек, возникающих после записи данных в накопитель. Это повышает надежность устройства. Формула изобретения Запоминающее устройство с самоконтролем по авт. сВо № 883975, отличающееся тем, что, с целью повышения надежности устройства, в него введены схема сравнения и блок свертки по модулю два, первый вход которого соединен с выходом первого регистра адреса, а выходы поключены к одним из; ВХОДОВ четвертого регистра числа и первому входу схемы сравнения, второй вход которой соединен с одними из выходов четвертого регистра числа, второй вход блока свертки по модулю два и третий вход схемы сравнения подключены к одному из выходов блока управления, один из входов которого соединен с выходом блока контроля, выход схемы сравнения является одним из управляющих выходов устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 883975, кл. G П С 29/00, 1979 (прототип) .

I t

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1152044A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920849A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

| Запоминающее устройство | 1972 |

|

SU437127A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

t Т

Авторы

Даты

1982-09-30—Публикация

1981-03-24—Подача