го канала и первой группой информационных входов первого кан.ала, в каждом канале выходы первого и второго передающих регистров соединены соответственно с первой и второй группами информационных выходов канала, а информационные входы - -соответственно с выходами первого и второго

10831

74

коммутаторов, первые информационные входа которых подключены к третьей группе информационных входов канала, а вторые информационные входы - соответственно к второй и первой группам информационных входов канала и информационным входам первого и второго буферных регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство связи для вычислительной системы | 1977 |

|

SU734654A1 |

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО . СВЯЗИ ДЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащая 2Ц-1 каналов и блок синхронизации, первый выход которого соединен с входом синхронизации i-го канала

Изобретение относится к вычислительной технике и может быть исполь.зовано при построении ЭВМ и многопроцессорных вычислительных систем.

Известны устройства связи для вычислительной системы, содержащие блок синхронизации и объединенные в кольцо через две группы входив и выходов каналы связи, каждый из которых содержит два приемных регистра, два передающих регистра, два буферных регистра, блок управления, блок сравнения, регистр адреса и две группы элементов ИЛИ, причем два выхода синхронизахщи соединены с соответствунщими двумя входами синхронизации каждого канала lj.

Недостатки указанных устройств -. большие аппаратурные затраты, необходимые для их построения, и малая эффективность.

Наиболее близким к предлагаемому по технической сущности является многоканальное устройство связи для вычислительной системы, содержащее г нератор тактовых импульсов и объединенные в кольцо через две группы входов и выходов каналы связи, каждый из которых содержит два приемных регистра, два передающих регистра, два селектора-мультиплексора, построенных на четырех группах элементов И, блок сравнения, регистр адреса, три буфер ных регистра, блок формирования направления записи, регистр констант и блок управления, включающий регистр состояния, причем в.каждом канале управлякиций вход передаюощх регистров соединен с входом синхронизации канала и блока управления, соответствующие управлякхцие выходы которого соединены с соответствующими выходами устройства связи и управляющими входами селекторов-мультиплексоров, блока формирования направления записи и буферных регистров, выходы которых соединены с выходами соответствующих

групп информационных выходов устройства связи, соответствуняцие управляющие входы соединены с соответствующими входами блока управления, остальные соответствующие входы которого

соединены с выходами блока формирования направления записи и блока сравнения, входы третьей группьг входов которого соединены с выходами регистра адреса и с входами первой

группы входов блока формирования направления записи, вторая группа входов которого соединена с выходами регистра констант 2J .

Недостатками известного устройства Являются большие аппаратурные затраты и малая эффективность, связанная с большими затратами количества оборудования на единицу пропускной способности.

Цель изобретения - сокращение аппаратурных затрат и повышение эффективности устройства связи путем исключения в каждом канале известного устройства двух приемных и одного

буферного регистров и уменьшения количества оборудования, приходящегося на единицу пропускной способности.

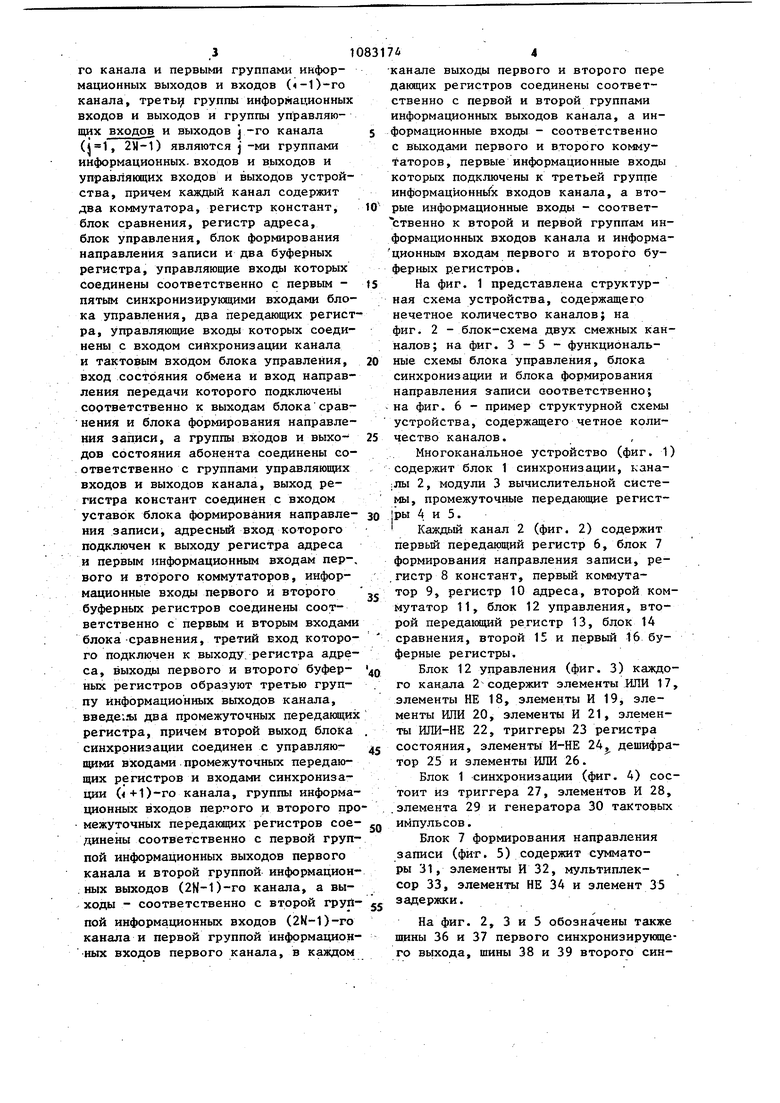

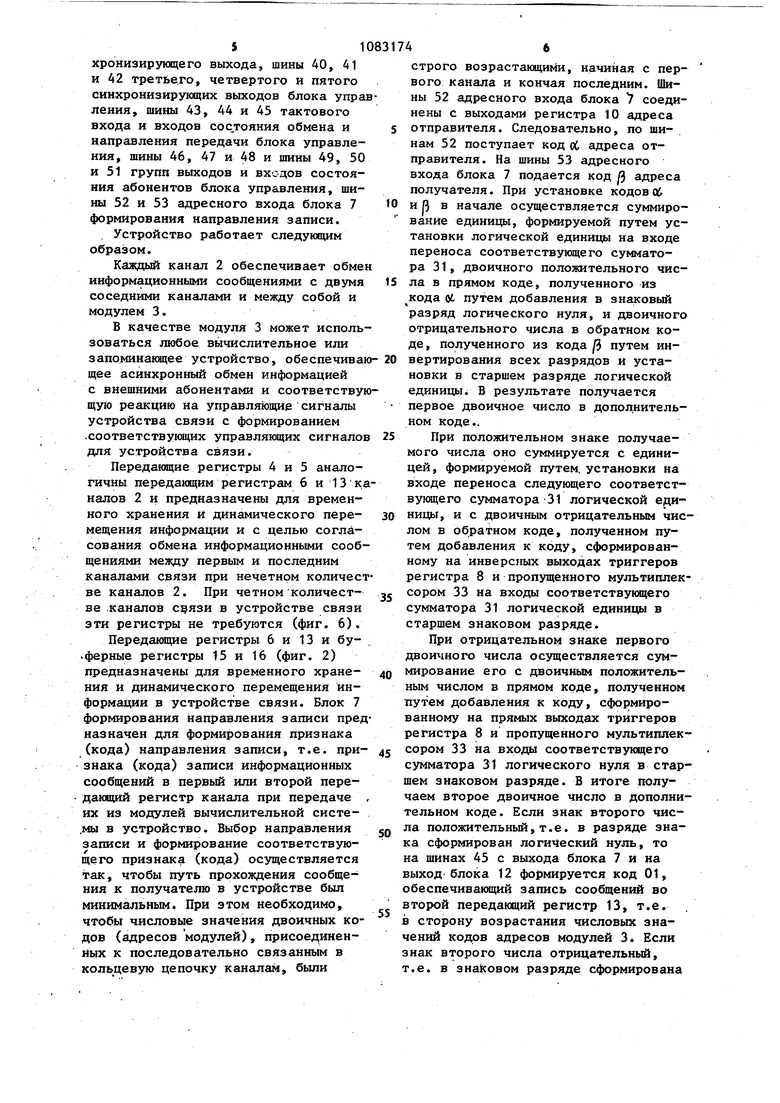

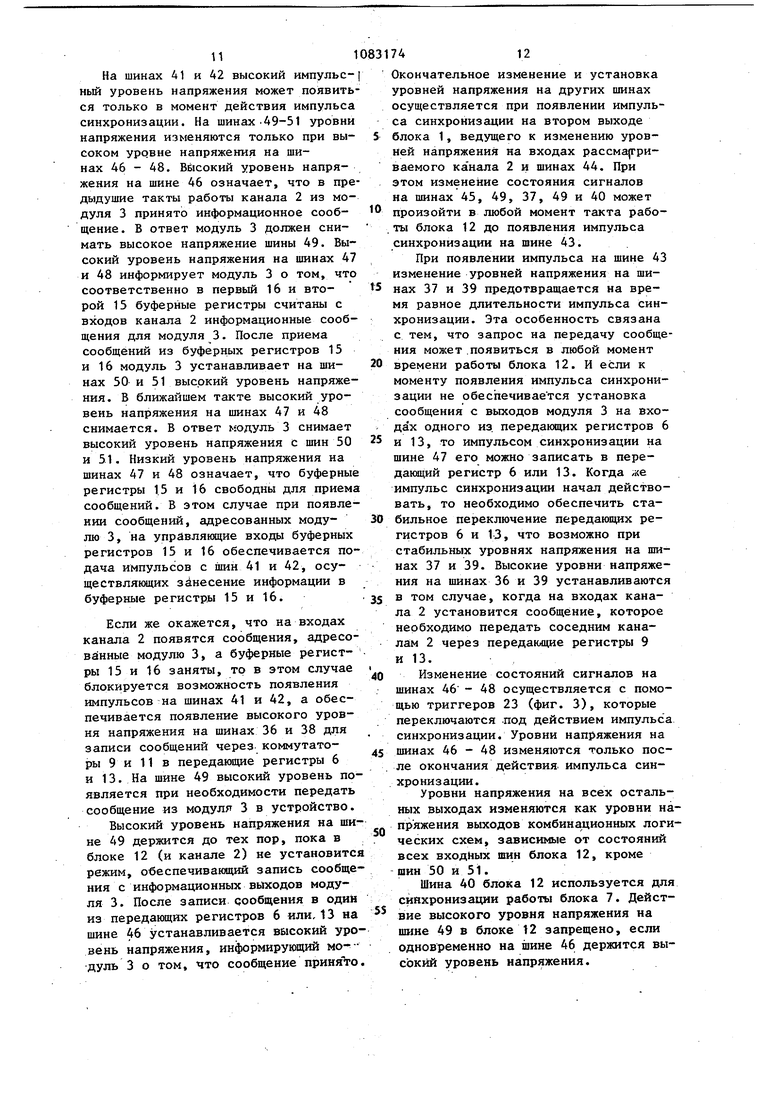

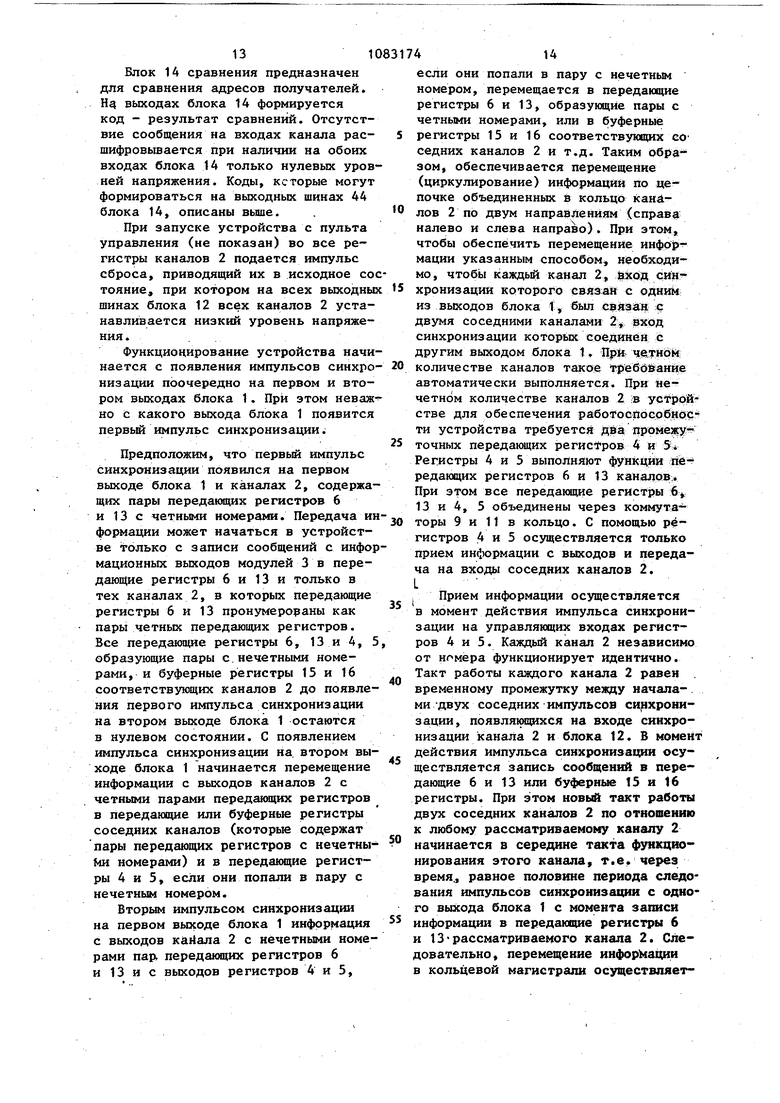

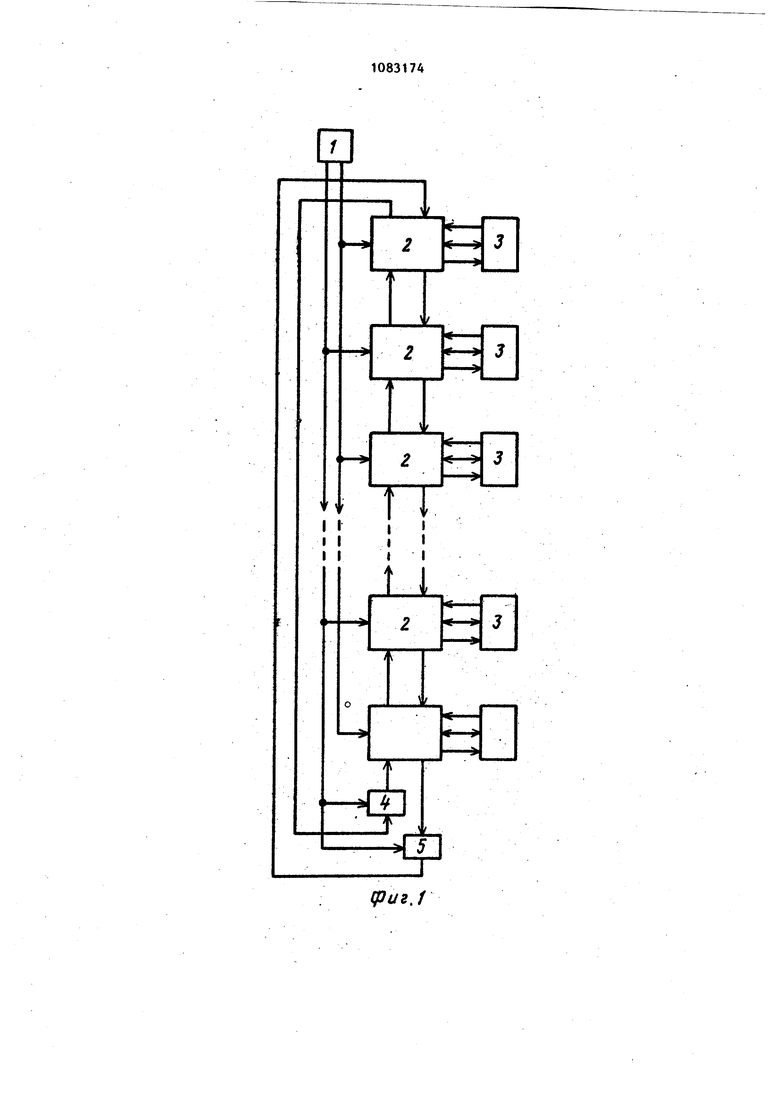

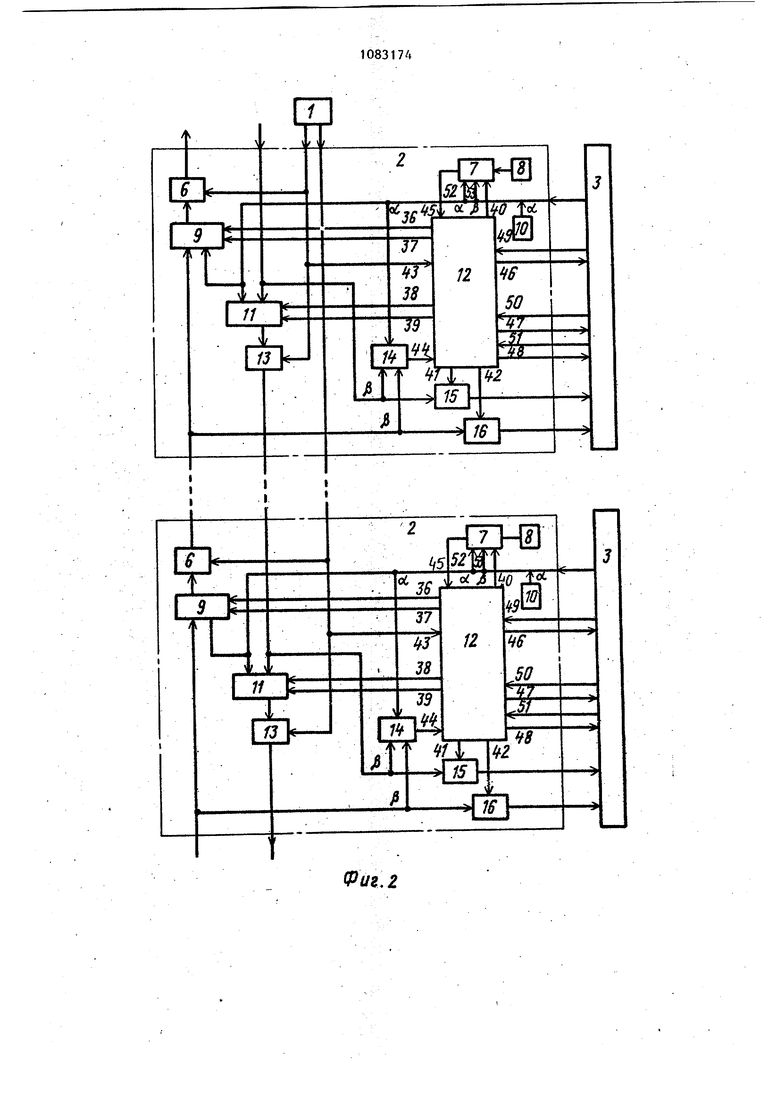

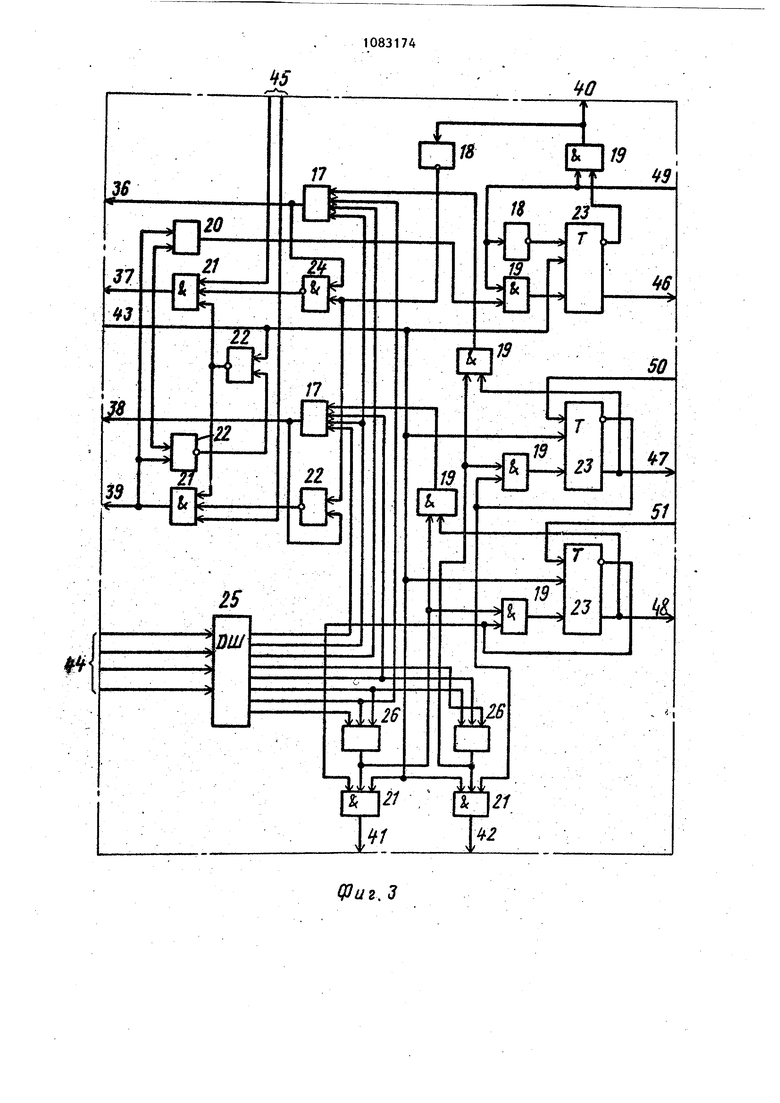

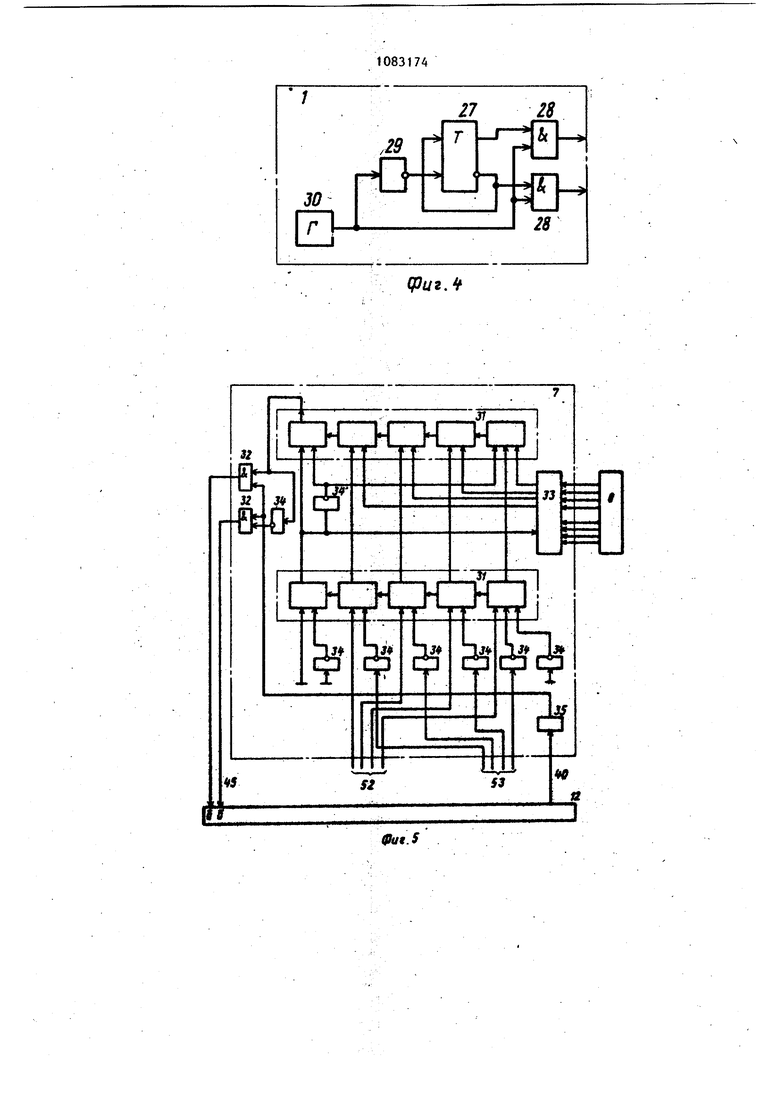

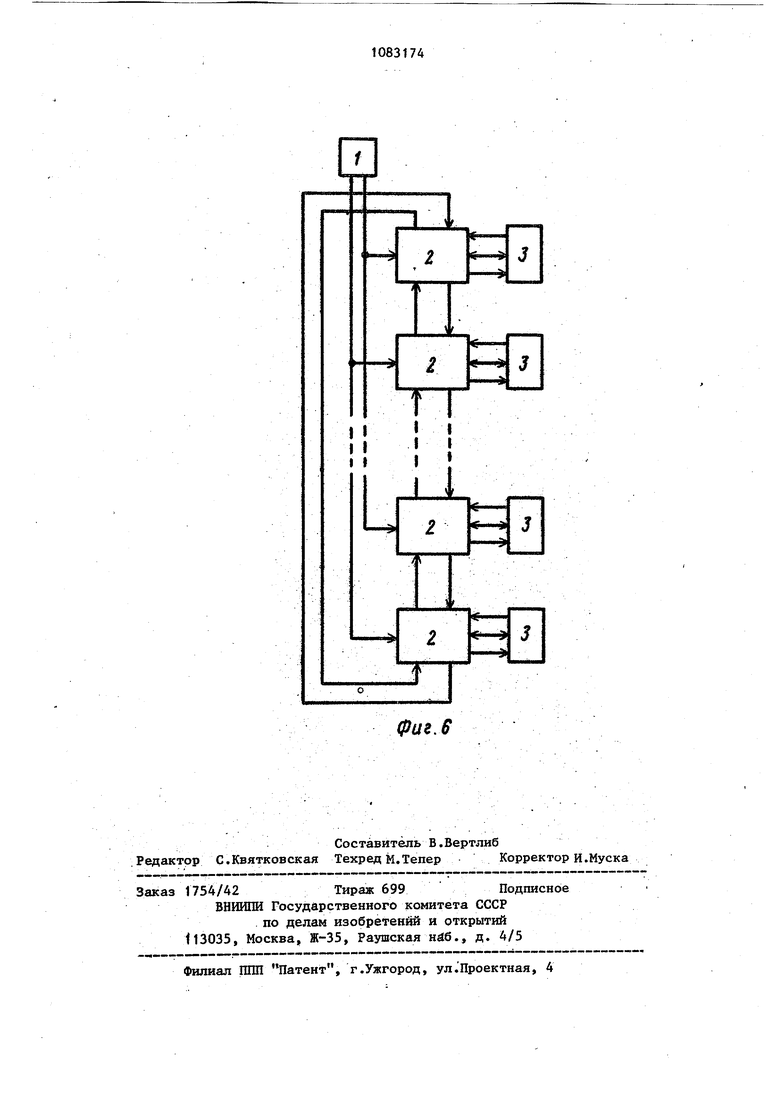

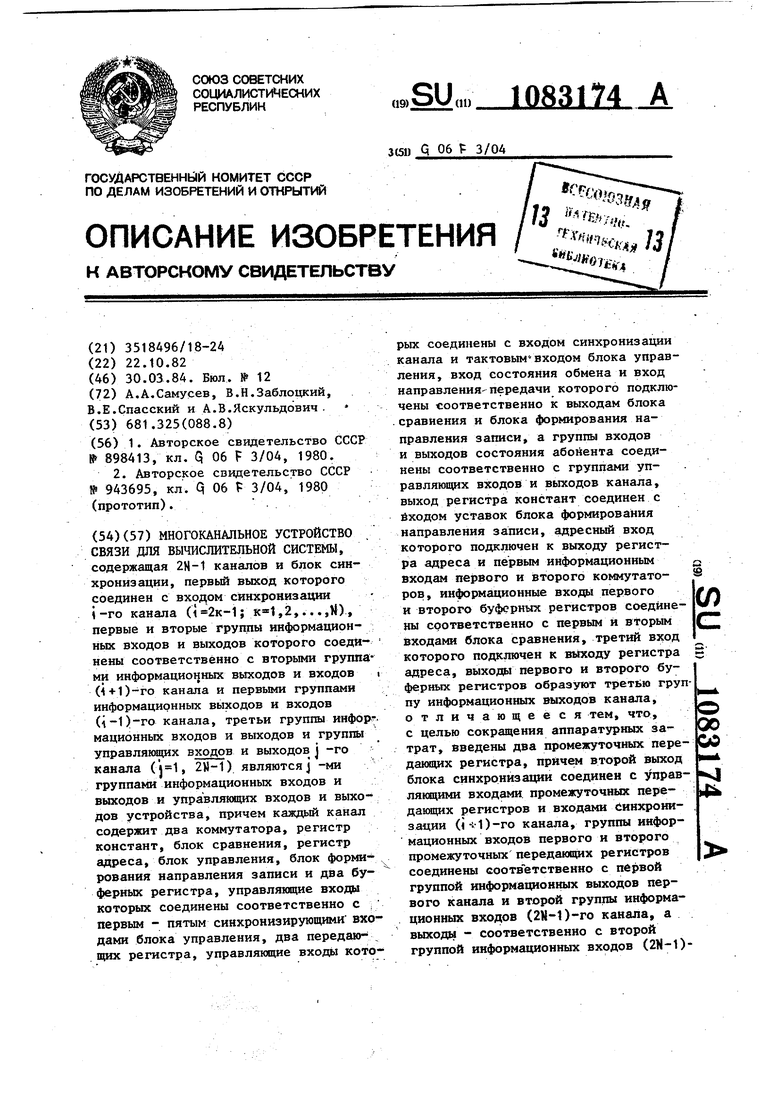

Поставленнаяцель достигается тем. что в многоканальное устройство, содержащее 2N-1 каналов и блок синхронизации, первый выход которого соединен с входом синхронизации 1-го канала (1 2к-1; ,2,...,N), первые и вторые группы информационных входов и выходов которого соединены соответственно с вторыми группами информационных выходов и входов ( +1).3 го канала и первыми группами информационных выходов и входов (-1)го канала, треть группы инфорйациоиных входов и выходов и группы управляющих входов и выходов j -го канала (, 2)1-1) являются j -ми группами информационных, входов и выходов и управляюцих входов и выходов устройства, причем каждый канал содержит два коммутатора, регистр констант, блок сравнения, регистр адреса, блок управления, блок формирования направления записи и два буферных регистра, управляющие входы которых соединены соответственно с первым пятым синхронизирующими входами блока управления, два передающих регист ра, управляющие входы которых соединены с входом синхронизации канала и тактовым входом блока управления, вход состояния обмена и вход направления передачи которого подключены соответственно к выходам блока сравнения и блока формирования направления записи, а группы входов и выхоДОН состояния абонента соединены соответственно с группами управляющих входов и выходов канала, выход регистра констант соединен с входом уставок блока формирования направления записи, адресный вход которого подключен к выходу регистра адреса и первым ннформационным входам первого и второго коммутаторов, информационные входы первого и второго буферных регистров соединены соответственно с первым и вторым входами блока сравнения, третий вход которого подключен к выходу; регистра адреса, выходы первого и второго буферных регистров образуют третью группу информационш)1х выходов канала, введеи-ы два промежуточных передающих регистра, причем второй выход блока синхронизации соединен с управляющими входами промежуточных передающих регистров и входами синхронизации (+1)-го канала, группы информа ционных входов пертого и второго пр межуточных передакящх регистров сое динены соответственно с первой груп пой информационных выходов первого канала и второй группой информацион .ных выходов (2М-1)-го канала, а выходы - соответственно с второй груй пой информационных входов (2N-1)-ro канала и первой группой инфррмацион -ных входов первого канала, в каждом U4 канапе выходы первого и второго пере дающих регистров соединены соответственно с первой и второй группами информационных выходов канала, а информационные входы - соответственно с выходами первого и второго коммутаторов, первые информационные входы которых подключены к третьей группе инфopмaциoнньfx входов канала, а вторые информационные входы - соответственно к второй и первой группам информационных входов канала и информационным входам первого и второго буферных регистров. На фиг. 1 представлена структурная схема устройства, содержащего нечетное количество каналов; на фиг. 2 - блок-схема двух смежных канналов; на фиг. 3 - 5 - функциональные схемы блока управления, блока синхронизации и блока фор 1ирования направления з-аписи соответственно; на фиг. 6 - пример структурной схемы устройства, содержащего четное количество каналов., Многоканальное устройство (фиг. 1) содержит блок 1 синхронизации, кана;Лы 2, модули 3 вычислительной системы, промежуточные передающие регист|ры 4 и 5. Каждый канал 2 (фиг. 2) содержит первый передакяций регистр 6, блок 7 формирования направления записи, регистр 8 констант, первый коммутатор 9, регистр 10 адреса, второй коммутатор 11, блок 12 управления, второй передакядий регистр 13, блок 14 сравнения, второй 15 и первый 16 буферные регистры. Блок 12 управления (фиг. 3) каждого кан.ала 2-содержит элементы ИЛИ 17, элементы НЕ 18, элементы И 19, элементы ИЛИ 20, элементы И 21, элементы ИЛИ-НЕ 22, триггеры 23 регистра состояния, элементы И-НЕ 24, дешифратор 25 и элементы ИЛИ 26. Блок 1 синхронизации (фиг. 4) состоит из триггера 27, элементов И 28, элемента 29 и генератора 30 тактовьпс импульсов. Блок 7 формирования направления записи (фиг. 5) содержит сумматоры 31, элементы И 32, мультиплексор 33, элементы НЕ 34 и элемент 35 задержки. На фиг. 2, 3 и 5 обозначены также шины 36 и 37 первого синхронизирунндего выхода, щины 38 и 39 второго синхронизирукщего выхода, шины 40, 41 и 42 третье.го, четвертого и пятого синхронизирующих выходов блока упра ления, шины 43, 44 и 45 тактового входа и входов состояния обмена и направления передачи блока управления, шины 46, 47 и 48 и шины 49, 50 и 51 групп выходов и входов состояния абонентов блока управления, шины 52 и 53 адресного входа блока 7 формирования направления записи. Устройство работает следующим образом. Каждый канал 2 обеспечивает обме информационными сообщениями с двумя соседними каналами и между собой и модулем 3. В качестве модуля 3 может исполь зоваться любое вычислительное или запоминающее устройство, обеспечива щее асинхронный обмен информацией с внешними абонентами и соответству щую реакцию на управляющие сигналы устройства связи с формированием .соответствующих управляющих сигнало для устройства связи. Передающие регистры 4 и 5 аналогичны передающим регистрам 6 и 13 к налов 2 и предназначены для временного хранения и динамического перемещения информации и с целью согласования обмена информационными сооб щениями между первым и последним каналами связи при нечетном количес ве каналов 2. При четном количестве .каналов в устройстве связи эти регистры не требуются (фиг. 6). Переданнцие регистры 6 и 13 и бу.ферные регистры 15 и 16 (фиг. 2) предназначены для временного хранения и динамического перемещения информации в устройстве связи. Блок 7 формирования направления записи пред назначен для формирования признака (кода) направления записи, т.е. признака (кода) записи информационных сообщений в первый или второй передающий регистр канала при передаче их из модулей вычислительной систе.мы в устройство. Выбор направления записи и формирование соответствующего признака (кода) осуществляется так, чтобы путь прохождения сообщения к получателю в устройстве был минимальным. При этом необходимо, чтобы числовые значения двоичных кодов (адресов модулей), присоединенных к последовательно связанным в кольцевую цепочку каналам, были строго вoзpacтaIaци iи, начиная с первого канала и кончая последним. Шины 52 адресного входа блока 7 соединены с выходами регистра 10 адреса отправителя. Следовательно, по шинам 52 поступает код сС адреса отправителя. На шины 53 адресного входа блока 7 подается код Я адреса получателя. При установке кодов Л и Д в начале осуществляется суммирование единицы, формируемой путем установки логической единицы на входе переноса соответствующего сумматора 31, двоичного положительного числа в прямом коде, полученного из кода ot путем добавления в знаковый разряд логического нуля, и двоичного отрицательного числа в обратном коде, полученного из кода путем инвертирования всех разрядов и установки в старшем разряде логической единицыi Б результате получается первое двоичное число в дополнительном коде.. При положительном знаке получаемого числа оно суммируется с единицей, формируемой путем, установки на входе переноса следующего соответствуклцего сумматора 31 логической единицы, и с двоичным отрицательным числом в обратном коде, полученном путем добавления к коду, сформированному на инверсных выходах триггеров регистра 8 и пропущенного мультиплексором 33 на входы соответствуняцего сумматора 31 логической единицы в старшем знаковом разряде. При отрицательном знаке первого двоичного числа осуществляется суммирование его с двоичным положительным числом в прямом коде, полученном путем добавления к коду, сформированному на прямых выходах триггеров регистра 8 и пропущенного мультиплексором 33 на входы соответствующего сумматора 31 логического нуля в старшем знаковом разряде. В итоге получаем второе двоичное число в дополнительном коде. Если знак второго числа положительный, т. е. в разряде знака сформирован логический нуль, то на шинах 45 с выхода блока 7 и на выход блока 12 формируется код 01, обеспечивакиций запись сообщений во второй передающий регистр 13, т.е. в сторону возрастания числовых значений кодов адресов модулей 3. Если знак второго числа отрицательный, т.е. в знаковом разряде сформирована логическая единица, то на шинах 45 формируется код 10, обеспечивающий запись сообщений в первый передающий регистр 6, т.е. в сторону убывания числовых значений кодов адресов моду лей 3. Направление, возрастания значений кодов (адресов модулей 3) соответствует направлению движения информации через передающие регистры 13 каналов 2. Момент появления кода на шинах 45 блока 7 синхронизируется сигналом на щине 40 с выхода блока 12. Время задержки элемента 35 равно времени переходных процессов в сумматорах 31 и мультиплексоре 33. Алгоритм работы блока 7 обеспечивает выбор кратчайшего пути, т.е. продвижения информации по пути, на котором будет пройдено минимальное количество промежуточной каналов 2. Регистр 8 констант предназначен ДЛ5. хранения константы 2N/2 в двоичном представлении в прямом коде, где 2М - количество пар передающих регистров 6, 13и4, 5в устройстве. Знаковый разряд в регистре 8 отсутст вует. Регистры 10 адреса предназначены для хранения адресов отправителей. При этом код адреса, во всех разрядах которого только логические нули расшифровывается как код Отсутстви сообщения. Блок 12 предназначен дл формирования управлякщих сигналов в каждом такте работы канала для бу ферных регистров 15 и 16, для коммутаторов 9 и 11 и модуля 3 в зависимости от сформированных сигналов кодов на выходах блока 14 сравнения выходах блока 7, состояния управляю щих выходов модуля 3. При этом под тактом работы блока 12 и канала 2 понимается временной промежуток меж ду моментами начала действия двух соседних импульсов синхронизации на шине 43 блока 12 и канала 2. Изменение состояний выходов блока 12 пр кращается после окончания действия импульса синхронизации. На входах дешифратора 25 по сигналам на шинах 44 с выхода блока 14 сравнения (фиг. 3) в каждом также формируется один из кодов: Чтение слева.и спра ва (), Чтение слева, справа передача () Чтение слева, справа свободно (ol.) Слева передача, справа чтение /U/f), Слева передача, справа передача (065) Слева .передача, справа свободно (ocg), Слева свободно, справа чтение (oi-j), Слева свободно, справа передача ( Слева свободно, справа свободно (). Выход дешифратора 25 соответс вующий входному коду () не используется. Реакция блока 12 на код (() обеспечивается благодаря установке на всех выходах .дешифратора 25 логического нуля. На шинах 45 формируется код направления записи с выходов блока 7. При формировании на шинах 45 кода 10 обеспечивается запись сообщений с выходов модуля 3 вправо, при формировании на шинах 45 кода 01 обеспечивается запись сообщения влево. Под направлением Запись вправо или влево подразумевается запись сообщений соответственно в первый 6 или второй 13 передакяций регистр. При этом под Чтение справа или слева понимается чтение информации с входов соответственно второго 11 или первого 9 :оммутаторов и запись ее соответственно во второй 15 или первый 16 буферные регистры. Блок 12 может функционировать так же, как и каждый канал 2, в одном из следующих режимов: Запись влево ( (), Запись вправо () Чтение справа (/Зз), Чтение слева (/1), Чтение-чтение ( г) , Чтение справа, запись вправо (/3), Чтение слева, запись влево (/5f), Чтение, справа, запись влево (/%), Чтение слева, запись вправо () Чтение-чтение, запись влево (pio) у Чтение-чтение, запись вправо (), Передача влево ( /3,2 ) , Передача вправо (), Передача-передача (/(4), Передача влево, запись вправо (((5), Передача влево, чтение слева ( Р(6 ) , Передача влево, чтение слева, запись вправо (/(7 ) Передача вправо, запись влево () Передача вправо, чтение справа ( Р|9 ) Передача вправо, чтение справа, запись влево (ftjo, Холо.стой ход (/,). . Значение логических уровней напряжения и кодов на входах и выходах блока 12 в момент действия импульса синхронизации на шине 43,приведено В таблице. Примечание. Обозначение X означает любой (неопределенньй) логический уровень напряжения на соответствующей шине. 11 На шинах 41 и 42 высокий импульсный уровень напряжения может пойвить ся только в момент действия импульса синхронизации. На шинах.49-51 уровни напряжения изменяются только при высоком уровне напряжения на шинах 46 - 48. Высокий уровень напряжения на шине 46 означает, что в пре дыдушие такты работы канала 2 из модуля 3 принято информационное сообщение. В ответ модуль 3 должен снимать высокое напряжение шины 49. Высокий уровень напряжения на шинах 47 и 48 информирует модуль 3 о том, что соответственно в первый 16 и второй 15 буферные регистры считаны с входов канала 2 информационные сообщения для модуля 3. После приема сообщений из буферных регистров 15 и 16 модуль 3 устанавливает на шинах 50 и 51 высокий уровень напряжения. В ближайшем такте высокий уровень напряжения на шинах 47 и 48 снимается. В ответ модуль 3 снимает высокий уровень напряжения с шин 50 и 5.1. Низкий уровень напряжения на шинах 47 и 48 означает, что буферные регистры 15 и 16 свободны для приема сообщений. В этом случае при появлении сообщений, адресованных модулю 3, на управляющие входы буферных регистров 15 и 16 обеспечивается подача импульсов с шин 41 и 42, осуществляющих занесение информации в буферные регистры 15 и 16. Если же окажется, что на входах канала 2 появятся сообщения, адресованные модулю 3, а буферные регистры 15 и 16 заняты, то в этом случае блокируется возможность появления импульсов на шинах 41 и 42, а обеспечивается появление высокого уровня напряжения на шинах 36 и 38 для записи сообщений через коммутаторы 9 и 11 в передающие регистры 6 и 13. На шине 49 высокий уровень появляется при необходимости передать сообщение из модуля 3 в устройство. Высокий уровень напряжения на шине 49 держится до тех пор, пока в блоке 12 (и канале 2) не установится режим, обеспечивающий запись сообщения с информационных выходов модуля 3. После записи сообщения в один из передаимцих регистров 6 или, 13 на шине 46 устанавливается высокий уровень напряжения, информирующий мо-дуль 3 о том, что сообщение npHKHTO 74 Окончательное изменение и установка уровней напряжения на других шинах осуществляется при появлении импульса синхронизации на втором выходе блока 1, ведущего к изменению уровней напряжения на входах рассма|гриваемого канала 2 и шинах 44. При этом изменение состояния сигналов на шинах 45, 49, 37, 49 и 40 может произойти в любой момент такта работы блока 12 до появления импульса синхронизации на шине 43. При появлении импульса на шине 43 изменение уровней напряжения на шинах 37 и 39 предотвращается на время равное длительности импульса синхронизации. Эта особенность связана с тем, что запрос на передачу сообщения может появиться в любой момент времени работы блока 12. И если к моменту появления импульса синхронизации не обеспечивается установка сообщения с выходов модуля 3 на входах одного из. передающих регистров 6 и 13, то импульсом синхронизации на шине 47 его можно записать в передающий регистр 6 или 13. Когда же импульс синхронизации начал действовать, то необходимо обеспечить стабильное переключение передающих регистров 6 и 13, что возможно при стабильных уровнях напряжения на шинах 37 и 39. Высокие уровни напряжения на шинах 36 и 39 устанавливаются в том случае, когда на входах канала 2 установится сообщение, которое необходимо передать соседним канала;м 2 через передающие регистры 9 и 13. Изменение состояний сигналов на шинах 46 - 48 осуществляется с помощью триггеров 23 (фиг. 3), которые переключаются .под действием импульса синхронизации. Уровни напряжения на шинах 46 - 48 изменяются только после окончания действия импульса синхронизации. Уровни напряжения на всех остальных выходах изменяются как уровни напряжения выходов комбинационных логических схем, зависимые от состояний всех входных шин блока 12, кроме шин 50 и 51. Шина 40 блока 12 используется для синхронизации работы блока 7. Действие высокого уровня напряжения на шине 49 в блоке 12 запрещено, если одновременно на шине 46 держится высокий уровень напряжения. Блок 14 сравнения предназначен для сравнения адресов получателей. Н выходах блока 14 формируется код - результат сравнений. Отсутствие сообщения на входах канала расшифровывается при наличии на обоих входах блока 14 только нулевых уров ней напряжения. Коды, которые могут формироваться на выходных шинах 44 блока 14, описаны вьше. При запуске устройства с пульта управления (не показан) во все регистры каналов 2 подается импульс сброса, приводящий их в исходное со тояние при котором на всех выходны шинах блока 12 всех каналов 2 устанавливается низкий уровень напряжения . Функционирование устройства начи нается с появления импульсов синхро низации поочередно на первом и втором выходах блока 1. При этом неваж но с какого выхода блока 1 появится первь (шпульс синхронизации. Предположим, что первый импульс синхронизации появился на первом выходе блока 1 и каналах 2, содержа щих пары передающих регистров б и 13 с четными номерами. Передача и формации может начаться в устройстве только с записи сообщений с инфо мационных выходов модулей 3 в передающие регистры 6 и 13 и только в тех каналах 2, в которых передающие регистры 6 и 13 пронумерованы как пары четных передающих регистров. Все передавшие регистры 6, 13 и 4, образующие пары с.нечетными номерами, и буферные регистры 15 и 16 соответствующих каналов 2 до появления первого импульса синхронизации на втором выходе блока 1 остаются в нулевом состоянии. С появлением импульса синхронизации на. втором выходе блока 1 начинается перемещение информации с выходов каналов 2 с четными парами передшощих регистров в передающие или буферные регистры соседних каналов (которые содержат пары передающих регистров с нечетныfm номерами) и в передшощие регистры 4 и 5, если они попали в пару с нечетным номером. Вторым импульсом синхронизации на первом выходе блока 1 информация с выходов кайала 2 с нечетными номерами пар, передающих регистров 6 и 13 и с выходов регистров 4 и 5, если они попали в пару с нечетным номером, перемещается в передающие регистры 6 и 13, образующие пары с четными номерами, или в буферные регистры 15 и 16 соответствующих СО седних каналов 2 и т.д. Таким образом, обеспечивается перемещение (циркулирование) информации по цепочке объединенных в кольцо каналов 2 по двум направлениям (справа налево и слева направо). При этом, чтобы обеспечить перемещение информации указанным способом, необходимо, чтобы каждый канал 2, jaxOft сия хронизации которого связав с одниЬ из выходов блока 1, был с двумя соседними каналами 2 йход синхронизации коТорьк соединен с другим выходом блока 1. При четной количестве каналов такое требование автоматически выполняется. При We- четном количестве каналов 2 ;в устройстве для обеспечения работоспбсобности устройства требуется npoMej y точных передакнцих регистров 4 и 5 Регистры 4 и 5 выполняют функции передающих регистров 6 и 13 каналов.. При этом все передакмцие регистры 6 13 и 4, 5 объединены через коммутаторы 9 и 11 в кольцо. С помощью регистров .4 и 5 осуществляется только прием ин юрмации с выходов и передача на входы соседних каналов 2. L , Прием информации осуществляется в момент действия импульса синхронизации на управляющих входах регистров 4 и 5. Каждый канал 2 независимо от номера функционирует идентично. Такт работы каждого канала 2 равен . временному промежутку между началами -двз соседних импульсов си хронизации, появлякшфихся на входе синхронизации канала 2 и блока 12. В момент действия импульса синхронизации осуществляется запись сообщений в передающие 6 и 13 или буфернью 15 и 16 регистры. При этом новый такт работы двух соседних каналов 2 по отношению к любому рассматриваемому каналу 2 начинается в середине такта функционирования этого каыала, т.е. через время., равное половине периода следования импульсов синхронизации с одно го выхода блока 1 с момента записи информации в передающие регистры 6 и 13-рассматриваемого канала 2. Следовательно, перемещение информации в кольцевой магистрали осуществляет15ся со скоростью, соответствующей сум марной частоте следования импульсов синхронизации с обоих выходов блока 1. В любом такте функционирования в каждом канале 2 устанавливается один из режимов паботы, соответствую щих режимам рабо ibi блока 12 . Любой режим функционирования рассматриваемого канала устанавливается следую.л(Км образом. Под действием импульса синхронизации, подаваемого на вход синхрониЭ)ации соседних по отношению к рассматриваемому каналов 2, на входы рассматриваемого канала 2 подаются новые сообщения или все входы устанавливаются в Нулевые логические сос тояния. Каждое сообщение имеет следующие поля: полб адреса получателя поле адреса отправителя; поле данных Входы каналов 2, соответствующие полям адреса получателя, соединены с входами первой и второй групп входов блока 14 сравнения. До появления импульса синхронизации на входе синхронизации рассматриваемого канала 2 на обоих входах блока 14 устанавливаются коды адресов получателя из поля адреса получателя сообщений, установившихся на входах рассматриваемого канала 2, а на выходе (шины 44) блока 14 устанавливается код результата сравнения кодов адресов получателя на каждом из двух входов блока 14 с адресом модуля 3, поступающего с вьпсодов регистра 10 адреса. Одновременно на информационных выходах модуля 3 может также появит ся сообщение, сопровождаемое сигналом на шине 49 блока 12. К моменту появления импульса син хронизации на шине 43 на щинах 45 уже сформирован код направления записи ,| а на выходах блока 12 устанав ливаются уровни напряжения, обеспечивающие функционирование канала 2 в сформировавшемся режиме в соответ ствии с таблицей. Направление перемещения информации в каждом режиме Фтнкционирования определяется найме кованием режима. При режиме j осуществляется за пись сообщения, установившегося выходах модуля 3, во второй передаю щий регистр 13. Первый передаюций ; регистр 6 устанавливается в нулевое состояние. На входах канала 2 сообщ ние отсутствует. Буферные регист74ры 15 и 16 могут находиться в произ вольном состоянии. При режиме / осуществляется запись сообщения установившегося на выходах модуля 3 в первый передающий регистр 6. На в-ходах канала 2 сообщение отсутствует. Второй передающий регистр 13 устанавливается, в нулевое состояние. Буферные регистры 15 и 16 могут находиться в произвольном состоянии. При режиме р осуществляется чтение сообщения с первой группы информационных входов канала и запись его во второй буферный регистр 15. На остальных входах к.анала 2 и информационных выходах модуля 3 сообщения отсутствуют. Первьй буферный регистр 16 может находиться в произвольном состоянии. Второй буферньп регистр 15 должен быть свободен для записи сообщения. Оба передающих регистра 6 и 13 устанавливаются в нулевое состояние. При режиме j} осуществляется чтение сообщенияс второй группы информационных входов кансша и запись его в первый буферный регистр 16. На остальных входах канала 2 и информационных выходах модуля 3 сообщения отсутствуют. Второй буферньй регистр 15 может находиться в произвольном состоянии. Первьй буферный регистр 16 должен быть свободен для записи сообщения. Оба передающих регистра 6 и 13 устанавливаются .в нулевое состояние. При режиме /3 осуществляется чтение сообщений обоих информационных групп входов канала 2 и запись .их в соответствующие буферные регистры 15 и 16. На информационных выходах модуля 3 сообщение отсутствует. Оба буферных регистра 15 и 16 должны быть свободны для записи сообщений. Оба передакмцих регистра 6 и 13 устанавливается в нулевое состояние. При режиме Ь осуществляется чтение сообщения, с первой группы и информационных входов канала 2 и запись его во второй буферньй регистр 15, .а также запись сообщения, установившегося на выходах модуля 3. в первый передающий регистр 6. На остальных входах канала 2 сообщение отсутствует. Первый буферньй регистр 16 может находиться в произвольном состоянии. Второй буферный 1710 регистр 15 должен быть свободен для 3 аписи сообще ния. - Второй передаю1Е(ий .регистр 13 устанавливается в нулевое состояние. При режиме осуществляется чтение сообщения с второй группы информационных входов канала и запись его в первый буферный регистр 16, а так же запись сообщения, установившегося на выходах модуля 3, во второй передающий регистр 13. Второй буферный регистр 15 может находиться в произвольном состоянии. Первый буферньй регистр 16 должен быть свободен для записи, сообщения. На остальных входах канала сообщение отсутствует. Первый передающий регистр 6 уста навливается в нулевое состояние. При режиме g осуществляется чтение сообщения с первой группы информационных входов канала и запись его во второй буферный регистр 15, а так же запись сообщения, установившегося на выходах модуля 3, во второй передающий регистр 13. На остальных входах канала сообще ние отсутствует. Первый буферньй регистр 16 может находиться в произвол ком состоянии. Второй буферный регистр 15 должен быть свободен для за писи сообщения. Первый передающий ре гистр 6 устанавливается в нулевое состояние. При режиме fin осуществляется чтение сообщения со второй группы информационных входов канала и запись его в первый буферный регистр 16, а также запись сообщения, установившегося на выходах модуля 3,в первый переданнций регистр 6. На остальных входах канала 2 сообщение отсутствует. Второй буферный регистр 15 может находиться в произвольном состоянии. Первьш буферный регистр 16 должен быть свободен для записи сообщения. Второй передающий регистр 13 устанав ливается в нулевое состояние. При режиме |,о осуществляется чтение сообщений с обоих групп информационных входов канала 2 и запись их в соответствующие буферные регист ры 15 и 16, а также запись сообщения, установившегося на выходах модуля 3, во второй передающий регистр 13. Первый передающий регистр 6 устанавливается в нулевое состояние. Оба буферных регистра 15 4 и 16 должны быть свободны для записи сообщений. При режиме /(/ осуществляется чтение сообщений с обоих групп информа дионных входов канала 2 и запись их в соответствующие буферные регистры 15 и 16, а также запись сообщения, установившегося на выходах модуля 3, в первый передающий регистр 9. Второй передающий регистр 13 устанавливается в нулевое состояние. Оба буферных регистра должны быть свободны для записи сообщений . При режиме /,(2; осуществляется запись сообщения, установившегося на входах первой группы информационных входов канала 2, во второй передающий регистр 13. Второй буферный регистр 15 может находиться в произвольном состоянии при сообщениях на соответствующих входах канала 2, не адресованных соответствующему (своему) модулю 3, или должен быть занят при сообщениях на входах канала 2, адресованных соответствующему модулю 3. На остальных входах канала 2 сообщение отсутствует. На информационных выходах модуля 3 сообщение можеч отсутствовать или присутствовать, будучи направляемым для записи во второй передающий регистр 13. Первый передающий регистр 6 устанавливается в нулевое состояние. Первый буферный регистр 16 может находиться в произвольном состоянии. При режиме 13 осуществляется запись сообщения, установившегося на входах второй группы информационных входов канала 2, в первьй передающий регистр 6.. Первый буферный регистр 16 может находиться в произвольном состоянии. при сообщениях, не адресованных соответствукнцему модулю 3, или должен быть занят для записи сообщений, адресованных соответствукяцему модулю 3. На остальных входах канала 2 сообщения отсутствуют. На информационных выходах модуля 3 сообщение может отсутствовать или присутствовать, будучи направляемым для записи в первый передающий регистр 9, Второйпередаюий регистр 13 устанавливается в нулевое состояние. Второй буферный регистр 15 может находиться в произольном состоянии. 1910 , При режиме Рц осуществляется заг пись сообщений, установившихся на входах обеих групп информационных входов канала 2, в соответствующие передающие регистры 6 и 13. Буферные регистры 15 и 16 могут быть либо оба свободны в случае, если сообщения не адресованы модулю 3, либо могут быть оба занятыми для записи сообщений, адресованных модулю 3. Первьй буферный регистр 16 может быть занят при условии,-что соответствующее сообщение адресовано модулю 3, вто рой буферный регистр 15 может быть при этом в произвольном состоянии при условии, что другое соответствую щее сообщение не адресовано модулю 3 либо первый буферный регистр 16 может быть в произвольном состоянии при условии, что первое соответствую щее .сообщение не адресовано модулю,3 а второй буферный регистр 15 должен быть при этом занят при условии, что соответствующее (второе) сообщение адресовано соогветствующему модулю 3 На информационных выходах модуля 3 сообщение может отсутствовать или присутствовать. При режиме i осуществляется за пись сообщения, установившегося на входах первой группы информационных входов канала 2, во второй передающий регистр 13, а также запись сообщения , установившегося на выходах . модуля 3, в первый передающий регистр 6. Второй буферный регистр 15 может находиться в произвольном состоянии при сообщении на соответствую щих входах канала 2, не адресованного соответствующему модулю 3, или должен быть занят для записи сообщ ния, адресованного соответствующему модулю 3. Первый буферньй регистр 16 может находиться в произвольном состоянии. При режиме fi(g осуществляется запись сообщения, установившегося на входах первой группы информационных входов канала 2, во второй передающий регистр 13, а также чтения сооб щения первой группы информащюнных входов канала 2 и запись его в первый буферный регистр 16. Второй буферный регистр 15 может находиться в произвольном состоянии при сообщениях, не адресованных данному модуДлю 3, или должен быть занят для записи сообщения, адресованного заданному модулю 3. Первый буферный регистр 16 должен быть свободен для записи сообщений. На выходах модуля 3 сообщение может не быть либо может установиться сообщение для записи во второй передающий регистр 13, Первый передающий регистр 6 устанавливается в нулевое состояние. При режиме i осуществляется то же, что в режиме , кроме того, что на выходах модуля 3 устанавливается сообщение, записываемое в первый передающий регистр 9. . При режиме /g осуществляется то же, что и в режиме i , кроме того, что на выходах модуля 3 устанавливается сообщение, записываемое во второй передающий регистр 13. При режиме вт осуществляется запись сообщения со второй группы информационных входов канала 2 в первый переданяций регистр 6, а также чтение сообщений с первой группы информационных входов и запись его во второй буферный регистр 15. Первый буферный регистр 16 может находиться в произвольном состоянии при сообщении на соответствующих входах канала 2, не адресованных данному модулю 3, или должен быть занят для записи сообщения, адресованного соответствующему модулю 3. Второй буферный регистр 15 должен быть свобо-. ден для записи сообщений. На выходах модуля 3 сообщение может не быть либо может установиться сообщение для записи в первый передающий регистр 9. Регистр 13 устанавливается в нулевое пересостояние . При режиме осуществляется то же, что в режиме j9|g , кроме того, что на выходах модуля 3 устанавливается сообщение, записываемое во второй передающий регистр 13. При режиме Й2 сообщение на входах канала 2 и выходах модуля 3 отсутствует. Передаклцие регистры 6 и 13 устанавливаются в нулевое состояние. Таким образом, устройство обеспечивает обмен информации между модулями вычислительной системы при мень затратах оборудования в каждом канале.

-4

M I i

II I I II I I

--Ф

г

u

LA

tpuzj

fPae. 2

5

Tj

Фиг.З

0

4

30

Cpuz.f

Фиг.е

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1982-10-22—Подача